Фильтр по тематике

электроника

электроника

Верификация VHDL-описаний цифровых устройств, представленных в виде композиции управляющего и операционного блоков. Часть 2. Верификация на основе функционального покрытия

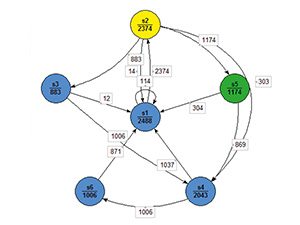

Во второй части статьи рассматривается функциональная верификация цифровых устройств, состоящих из управляющего и операционного блоков. Под такой верификацией понимается проверка выполнения всех переходов между внутренними состояниями, имеющихся в VHDL-модели управляющего блока, а для операционного блока – проверка использования значений входных операндов этого блока. СЭ №3/2018 808 0 0 электроника

электроника

Верификация VHDL-описаний цифровых устройств, представленных в виде композиции управляющего и операционного блоков. Часть 1. Верификация на основе покрытия VHDL-кода

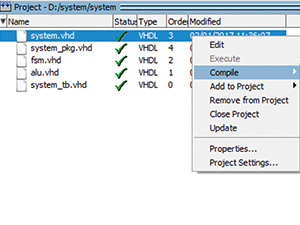

В статье описана методика проведения верификации VHDL-описаний цифровых устройств, представленных в виде композиции управляющего и операционного блоков. Под верификацией понимается проверка соответствия VHDL-описания проектируемого цифрового устройства спецификациям на проектирование. Для верификации используется логическое моделирование в системе Questa Sim (Mentor Graphics), выполняемое с покрытием VHDL-кода. СЭ №2/2018 1135 0 0 электроника

электроника

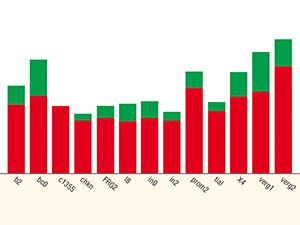

Эффективность проектирования заказных схем в синтезаторе LeonardoSpectrum

В статье сравнивается эффективность результатов проектирования заказных СБИС в различных версиях синтезатора LeonardoSpectrum. Эффективность определяется уменьшением площади и увеличением быстродействия синтезируемых схем. Сравнение версий проведено на примерах VHDL-описаний проектов цифровых схем. СЭ №1/2015 424 0 0 электроника

электроника

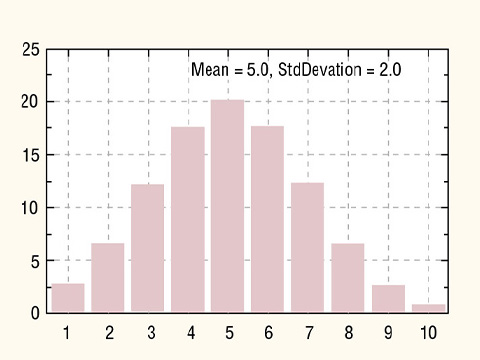

Средства VHDL для функциональной верификации цифровых систем: пакет RandomPkg

Статья посвящена описанию типов данных и функций пакета RandomPkg, входящего в методологию OS-VVM и предназначенного для псевдослучайной генерации чисел. На нескольких примерах показано, как можно использовать псевдослучайную генерацию в тестирующих программах. СЭ №1/2014 304 0 0