Введение

Цифровые устройства, представляемые в виде композиции (соединения) управляющего и операционного блоков, давно нашли широкое применение в практике проектирования [1]. В настоящее время проекты таких устройств задаются на языках VHDL и Verilog [2], предназначенных для проектирования цифровых схем на современной базе заказных СБИС (сверхбольших интегральных схем) либо программируемых пользователями логических интегральных схем типа FPGA.

По VHDL-описаниям проектов автоматически строятся синхронные логические схемы в том или ином базисе логических элементов, называемом технологическим (целевым) базисом либо целевой библиотекой логических элементов. В настоящее время процесс синтеза автоматизирован и важнейшей проблемой при создании проектов СБИС и систем на кристалле [3] является проблема верификации исходных спецификаций, представленных на VHDL либо других языках, используемых для алгоритмического описания проектируемых цифровых устройств и систем.

Под верификацией понимается проверка правильности исходного VHDL-описания, т.е. проверка соответствия составленного синтезируемого VHDL-описания проектируемой цифровой системы спецификациям на проектирование. Далее будут использоваться примеры VHDL-описаний устройств, однако применяемая методика и инструментальные средства применимы и к описаниям на языке Verilog.

Цифровые устройства рассматриваемого типа, как правило, входят в состав более сложных проектов. Для проведения верификации всего проекта в целом требуется провести сначала отдельную верификацию таких устройств. Проведение верификации VHDL-описаний цифровых устройств, представленных в виде композиции управляющего и операционного блоков, является целью данной статьи. В первой части статьи описывается маршрут моделирования в системе Questa Sim [4], позволяющий выполнить верификацию на основе моделирования проекта с покрытием VHDL-кода, вторая часть будет посвящена верификации на основе функционального покрытия.

Пример операционного устройства

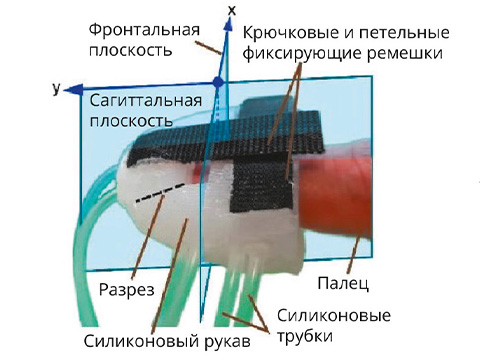

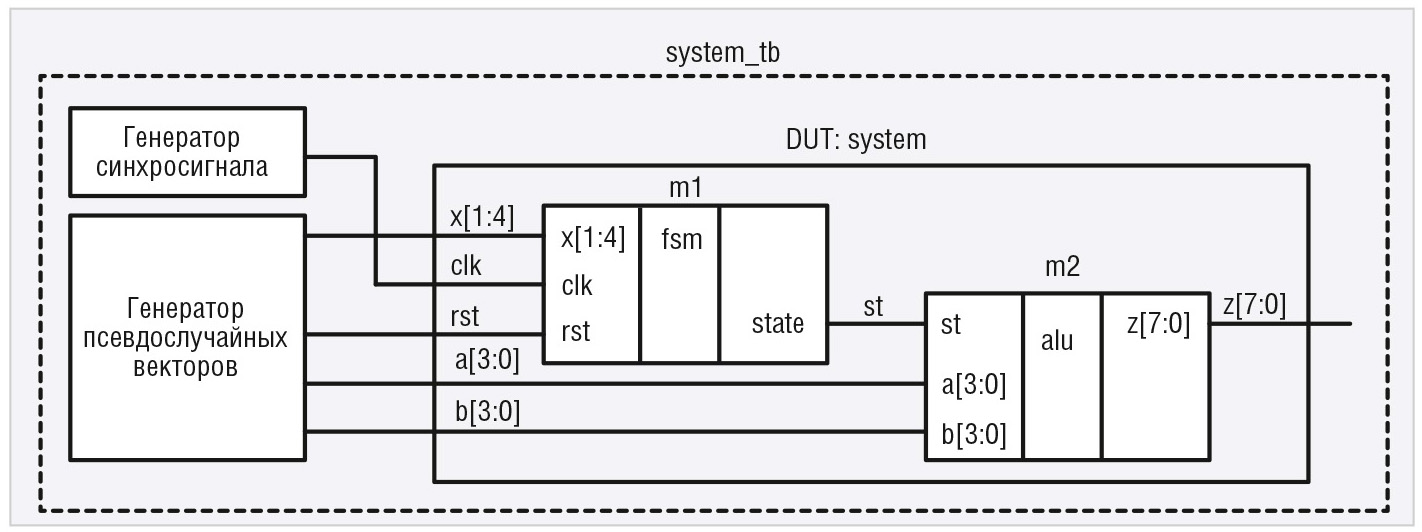

Простой пример цифрового устройства system представлен на рисунке 1.

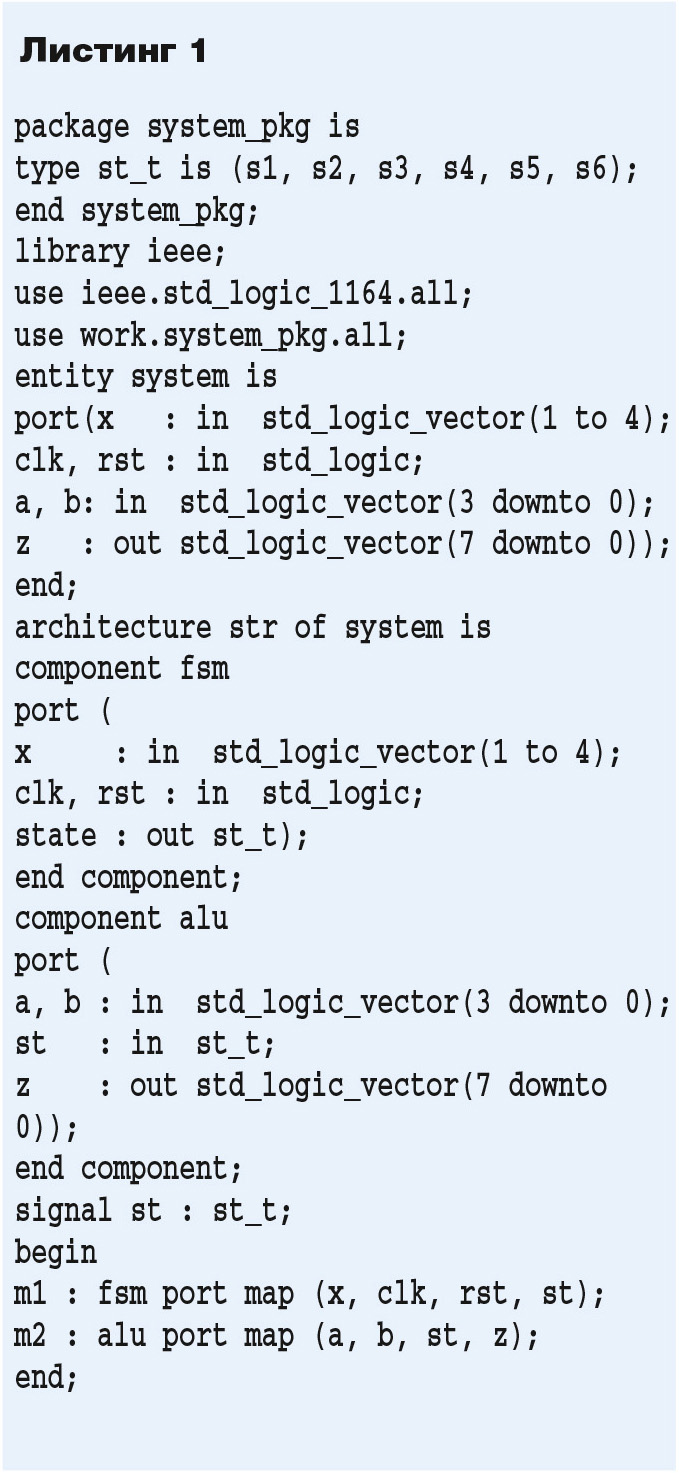

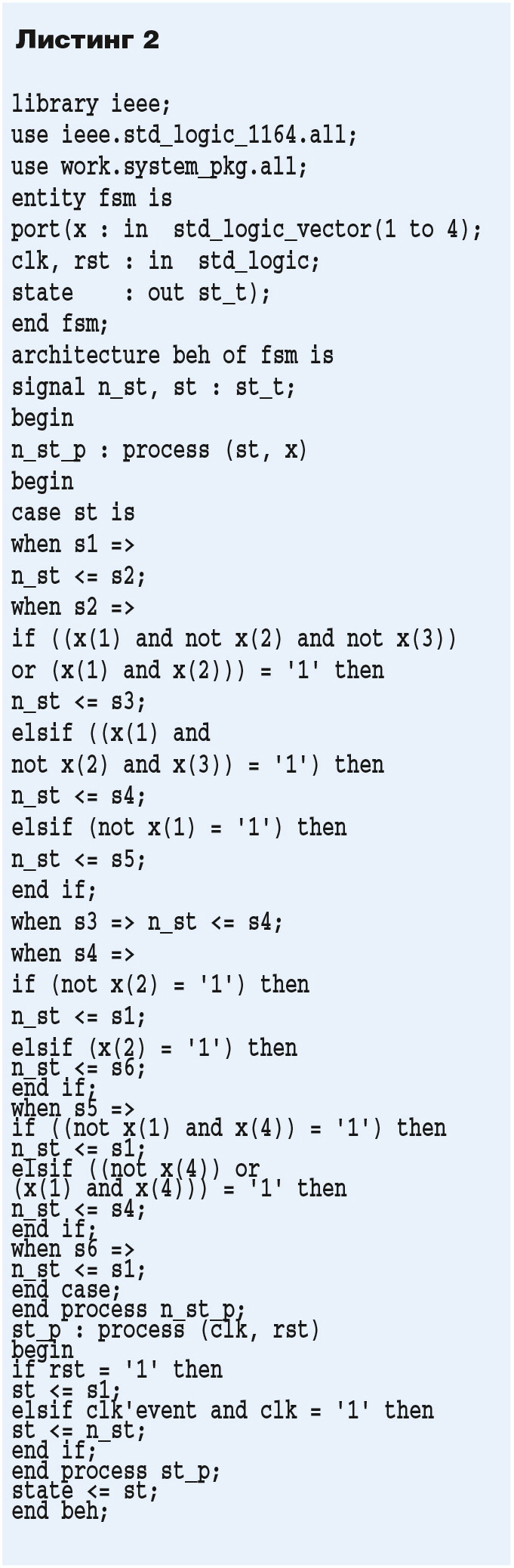

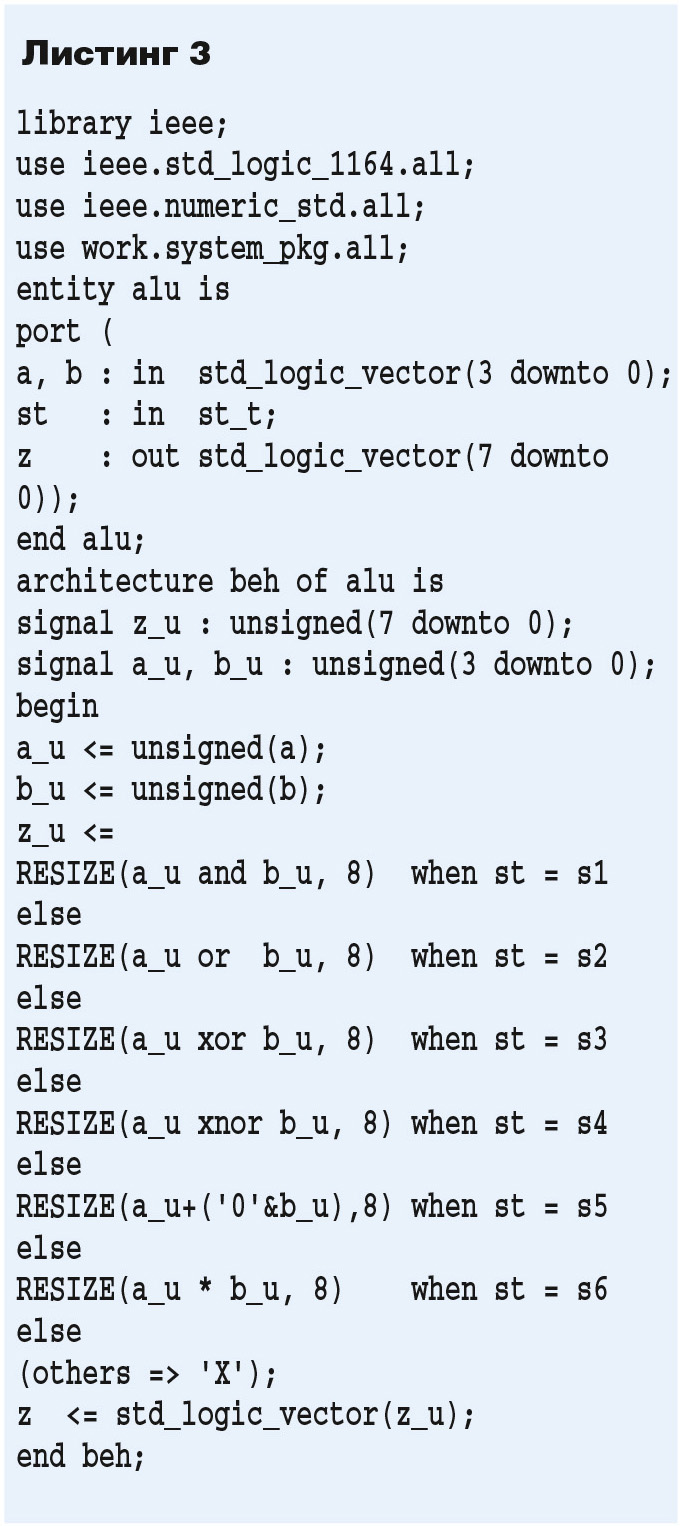

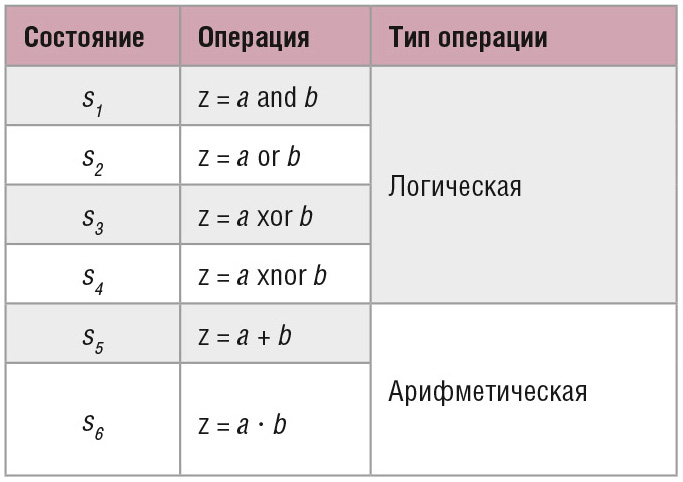

Описание устройства на языке VHDL представлено в листинге 1. Устройство состоит из двух подсхем (блоков): управляющий блок является конечным автоматом и имеет имя fsm (листинг 2), операционный блок – имя alu (листинг 3).

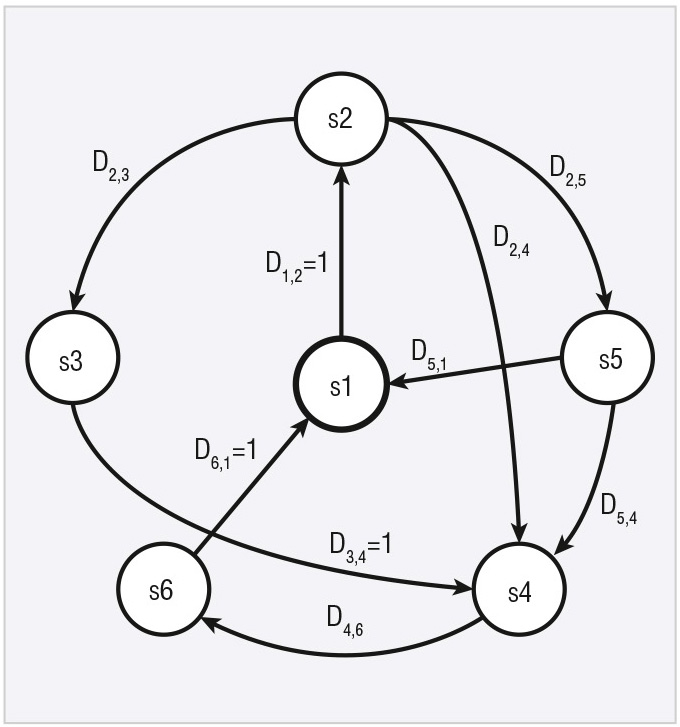

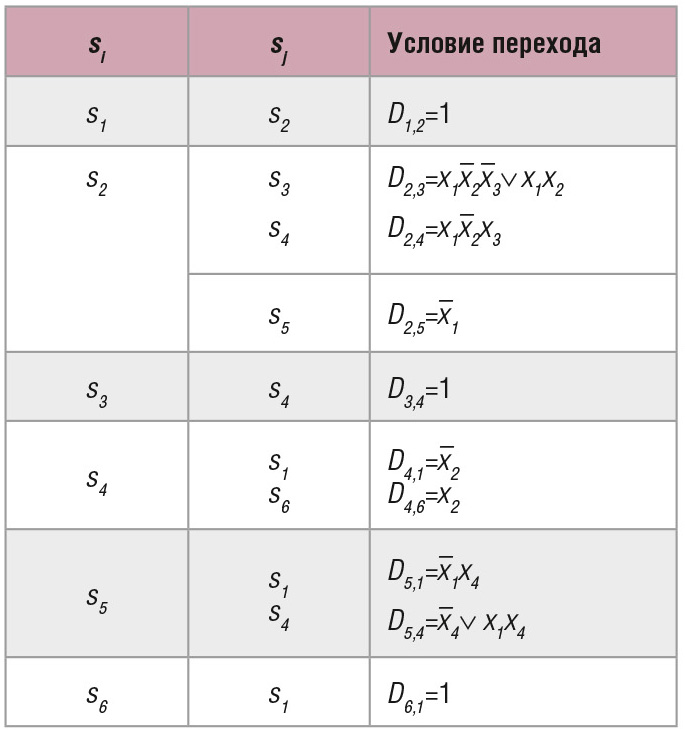

Управляющий автомат fsm задан графом G переходов (см. рис. 2), функции переходов даны в таблице 1. Если переход является безусловным, то ДНФ, задающая соответствующее условие перехода, равна единице.

На рисунке 2 не показаны асинхронные переходы из любого состояния si в начальное состояние s1 при единичном значении сигнала сброса rst. Двоичные входные векторы (порты) a, b называются операндами операционного блока. В примере число разрядов каждого из операндов равно четырём. Функции операционного блока заданы в таблице 2.

В зависимости от состояния функция операционного блока может быть либо арифметической (сложение либо умножение операндов a, b, понимаемых как двоичные коды чисел без знака), либо логической – в этом случае логическая операция выполняется над соответствующими разрядами двоичных векторов a, b.

Функционирование VHDL-модели управляющего автомата fsm осуществляется по тактам, смена состояния выполняется по переднему фронту синхросигнала clk. Управляющий автомат fsm начинает функционирование из начального состояния s1, меняет свои состояния и всегда возвращается в начальное состояние. Заметим, что для других цифровых устройств такого рода в графе переходов могут быть петли, что означает, что управляющий автомат не выходит из текущего состояния, а ожидает требуемую комбинацию управляющих входных сигналов x1, x2, x3, x4, чтобы перейти в другое состояние. В процессе функционирования цепочки состояний управляющего автомата образуют на графе G различные циклы. В данном простом примере каждый переход автомата из одного состояния в другое вызывает смену выполнения соответствующей операции в операционном блоке.

Верификация на основе покрытия VHDL-кода

Понятие «покрытие» при верификации применяется в различных контекстах и связано с выполнением операторов программы либо использованием (покрытием) при моделировании возможных входных воздействий и получением тех или иных реакций. Покрытие может относиться также к переключениям сигналов. В этом случае переключение сигнала считается покрытым, если в процессе моделирования произошли переключения в «обе стороны», т.е. сигнал переключился из 0 в 1 и обратно – из 1 в 0. Кроме операторов анализу на покрытие могут подвергаться также строки VHDL-кода, выражения, экземпляры компонентов (операторы port map). Покрытие характеризует текст программы с точки зрения исполнения фрагментов VHDL-кода при моделировании.

Применение процедур покрытия кода не предназначено для проверки правильности ожидаемых и получаемых реакций VHDL-модели цифровой системы на наборах значений входных сигналов и не гарантирует полной верификации.

Покрытие VHDL-кода как вид верификации исходит из общих принципов проверки правильности программ, написанных на любом (необязательно на VHDL) языке программирования, и не гарантирует (даже при 100% покрытии) полной верификации проекта. Тем не менее такой вид проверки текстов VHDL-программ, представляющих собой модели устройств, позволяет находить достаточно много ошибок в описаниях функционирования либо в структурах устройств. Наиболее простым понятием покрытия кода является покрытие строк. Данный вид покрытия может относиться как к структурному, так и функциональному описаниям системы и определяется следующим образом: если в данном сеансе моделирования с данным набором тестирующих векторов конкретная строка VHDL-кода была выполнена хотя бы один раз, то она является покрытой, если же строка кода ни разу не выполнялась, то она является непокрытой. В одной строке кода может содержаться несколько исполняемых операторов, поэтому считается, что более содержательным является покрытие операторов (в данном случае вместо строки кода рассматривается покрытие каждого исполняемого оператора). Напомним, что декларации в VHDL не являются исполняемыми и не подвергаются анализу на покрытие. В системе Questa Sim при моделировании можно указать следующие опции покрытия кода:

- Enable Statement coverage – позволяет системе моделирования подсчитать число выполнений каждого оператора в строке.

- Enable Branch coverage – подсчитывается число выполнений условий типа if/then/else и case и определяются случаи, когда истинное или ложное условие не выполнилось.

- Enable Condition coverage – анализируются выборы, сделанные в условиях if и case; данная опция является расширением Branch coverage.

- Enable Expression coverage – анализирует выражение в правой части оператора назначения сигнала (присвоения значения переменной) аналогично Condition coverage.

- Enable 0/1 Toggle coverage – считаются переходы логического сигнала из одного состояния в другое; учитываются только переходы из 0 в 1 и обратно.

- Enable 0/1/Z Toggle coverage – считаются переходы логического сигнала из одного состояния в другое; учитываются только переходы между значениями сигнала из множества {0, 1, Z}, где Z – значение «высокий импеданс» сигнала типа std_logic.

- Enable State Machine coverage – в VHDL-коде выделяется описание конечного автомата, для которого при моделировании подсчитываются пройденные (покрытые) переходы между внутренними состояниями, в которые попадает автомат.

Маршрут моделирования с покрытием кода

Чтобы выполнить покрытие кода при моделировании, требуется установить соответствующие опции при компиляции и выполнении моделирования. Рассмотрим данный вид моделирования на примере цифрового устройства. Далее перечислены шаги для выполнения моделирования с покрытием кода. Предполагается, что проект создан и проверен с помощью обычного моделирования, т.е. без покрытия кода [5].

Шаг 1. Установка опций покрытия кода перед выполнением компиляции

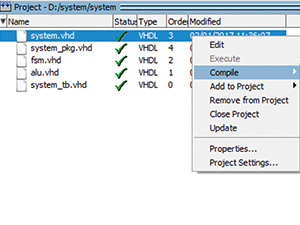

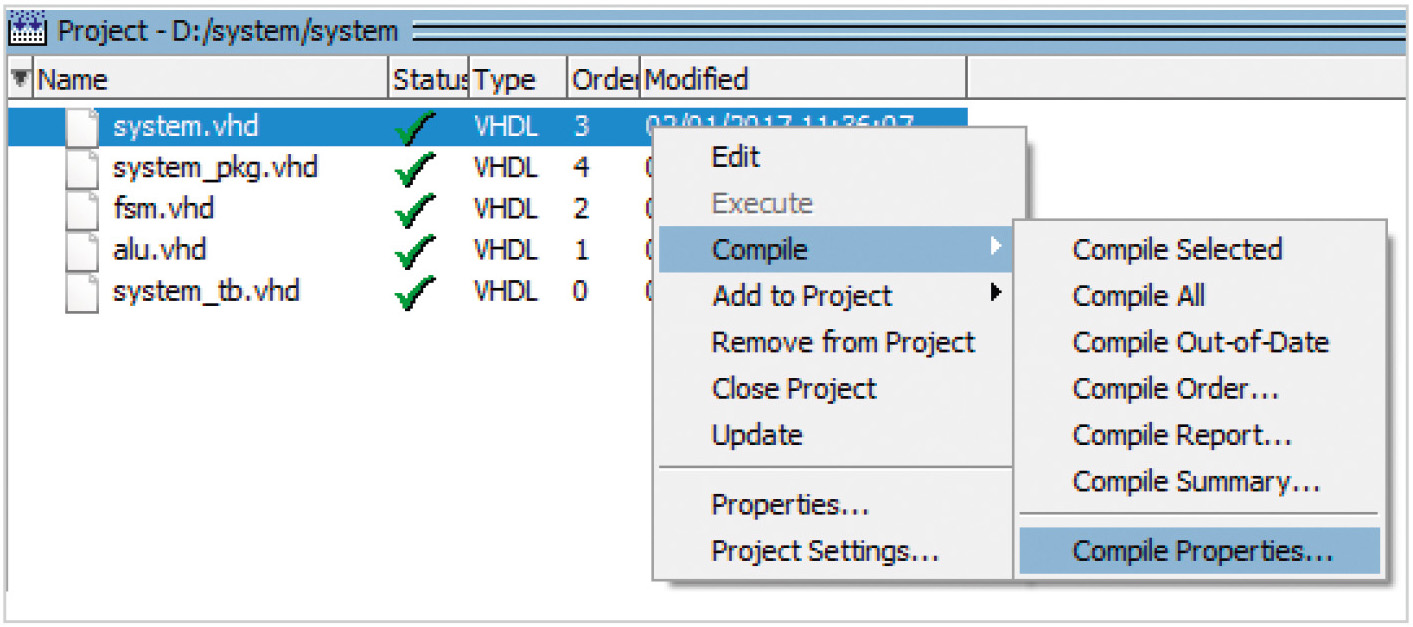

В закладке Project cначала требуется отметить требуемые файлы проекта, для которых планируется анализировать покрытие кода, а затем по правой клавише мыши открыть окно Compile Properties (см. рис. 3). Если это один файл, то можно установить курсор на этом файле.

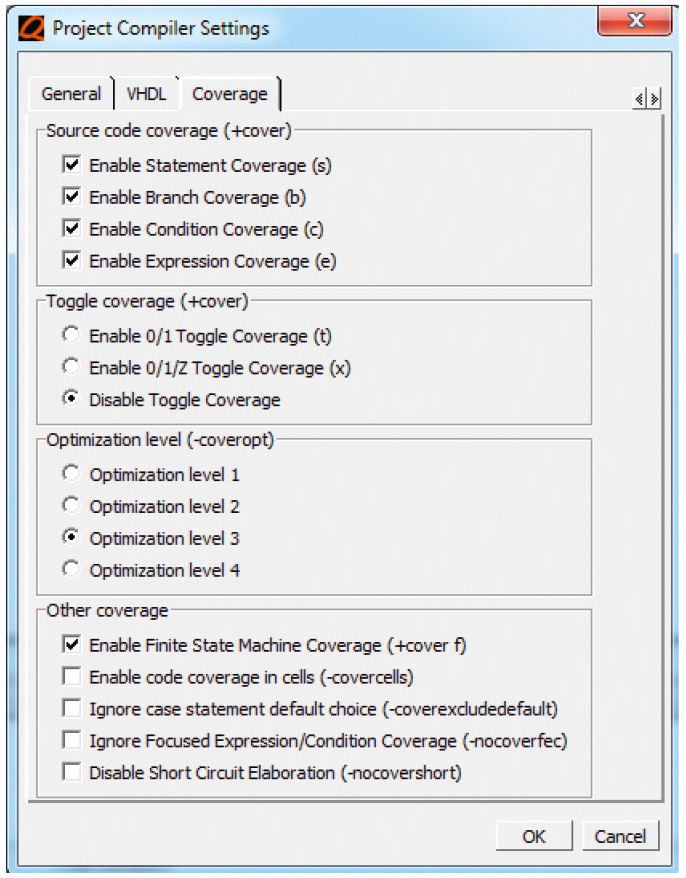

Открыв окно Compile Properties, в разделе Coverage требуется установить флаги (см. рис. 4):

- Enable Statement Coverage – для покрытия операторов;

- Enable Branch Coverage – для покрытия ветвлений;

- Enable Condition Coverage – для покрытия условных операторов;

- Enable Expression Coverage – для покрытия выражений;

- Enable Finite State Machine Coverage – для покрытия конечных автоматов.

После того как опции установлены, требуется нажать кнопку OK.

Шаг 2. Компиляция

Выполнить компиляцию можно различными способами: каждый модуль может компилироваться по отдельности, либо все они компилируются по команде Compile All.

Шаг 3. Установка опций покрытия кода перед моделированием и выполнение моделирования

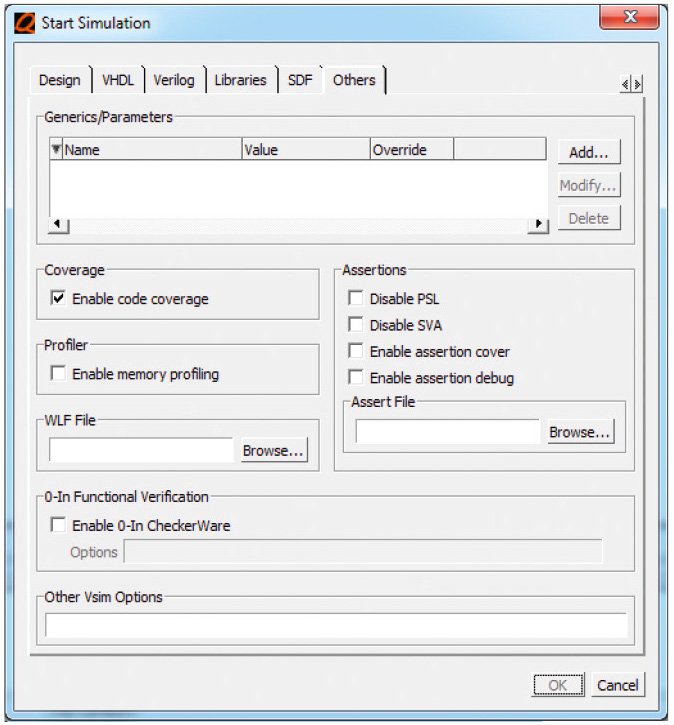

В закладке Simulation выбираем раздел Start Simulation, затем в закладке Others устанавливаем флаг Enable Code Coverage – «выполнять покрытие кода при моделировании» (см. рис. 5).

Затем осуществляется указание головного модуля, а после нажатия кнопки ОК совершается переход в режим моделирования. Дальнейшие действия являются стандартными для выполнения моделирования с использованием окон графического интерфейса. В режиме моделирования из окон Object сигналы переносятся в окно Wave. Выполнение моделирования осуществляется по команде Run All.

Шаг 4. Анализ покрытия одной строки кода

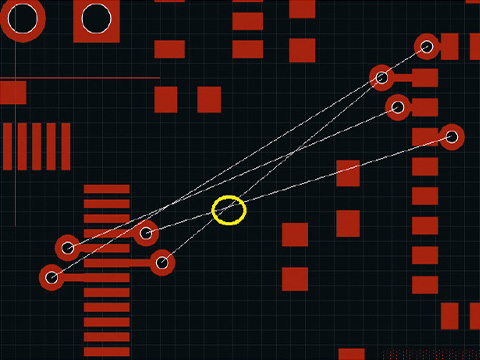

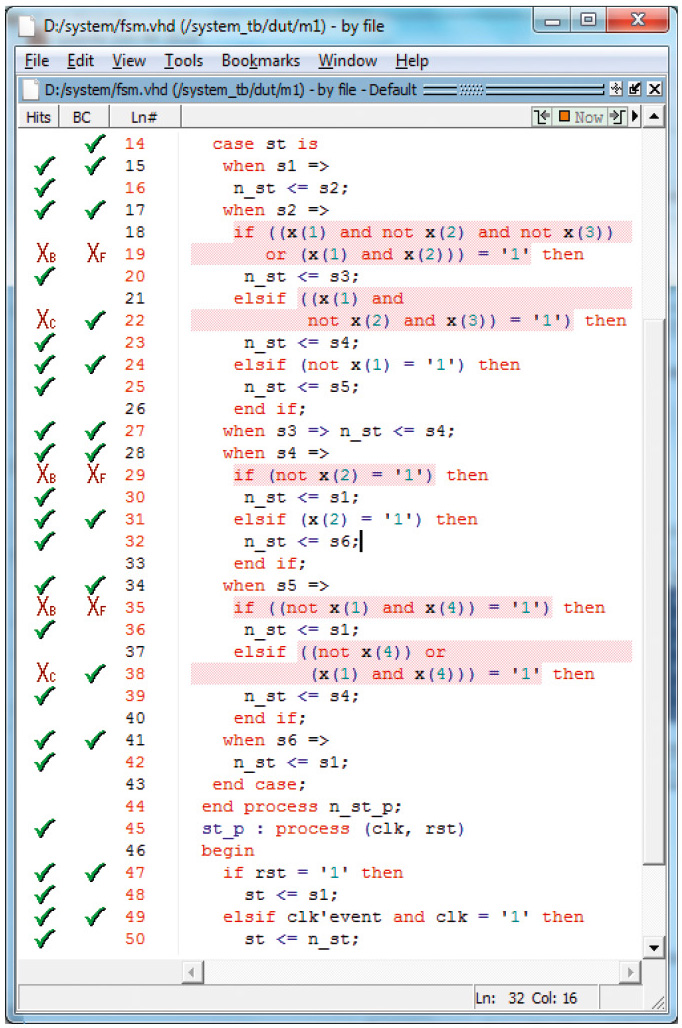

Чтобы увидеть, какие строки кода конкретного модуля отмечены как покрытые (непокрытые), требуется открыть текст этого модуля. На рисунке 6 символами XC, XB, XF отмечаются непокрытые строки VHDL-кода автомата.

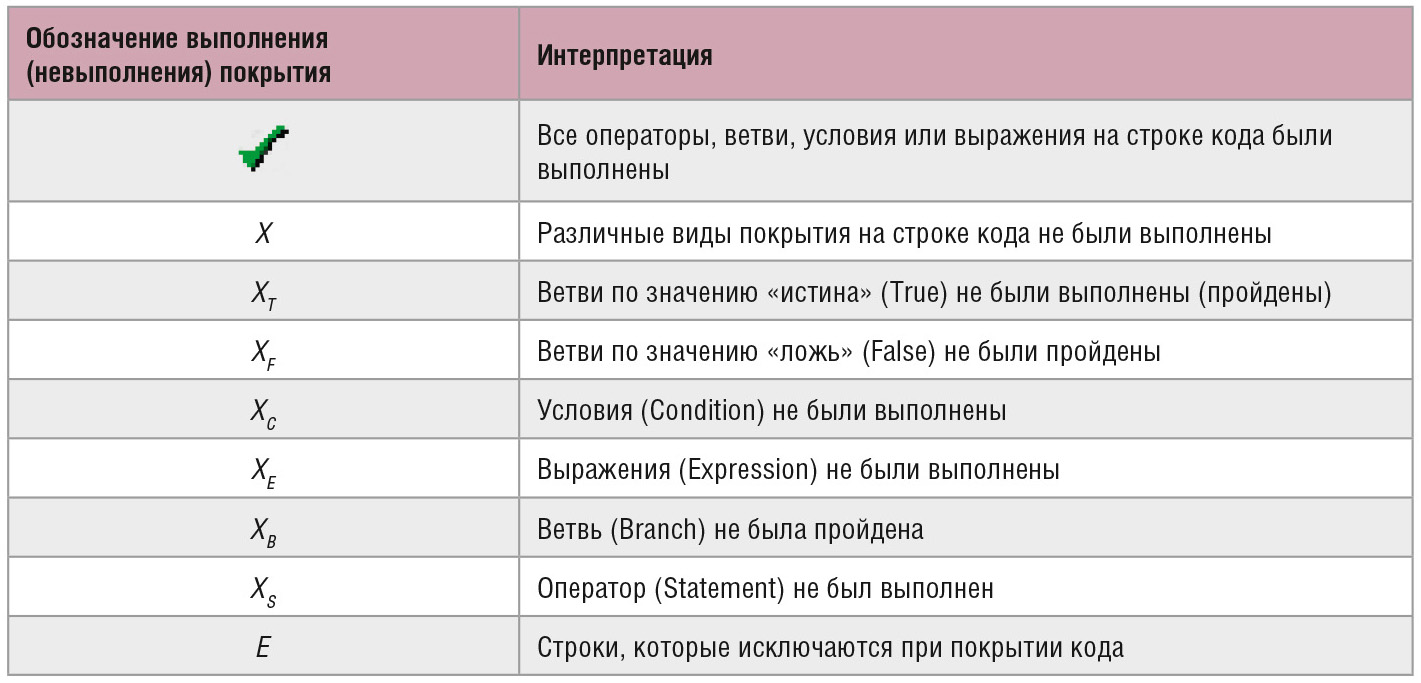

Значения данных символов, которые даны в отчёте о покрытии кода, приводятся в таблице 3.

Установив курсор на строку, можно получить отчёт о покрытии данной строки. Отчёт о покрытии строки можно также получить, выполнив View → Coverage → Details.

Шаг 5. Формирование общего отчёта о покрытии VHDL-кода

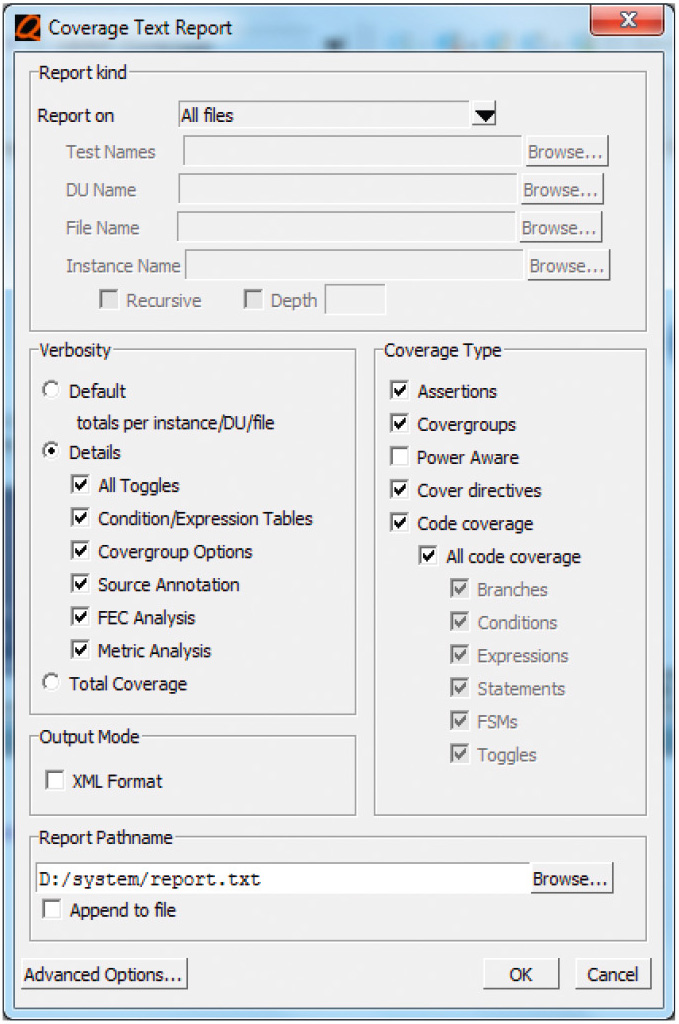

Чтобы получить общий отчёт о покрытии кода, нужно выполнить Tools → Coverage Report и выбрать форму представления отчёта: в виде текстового файла (Text) либо HTML-файла (HTML). Выбрав Text, требуется в открывшемся окне указать имя файла текстового отчёта (на рисунке 7 этот файл имеет имя report.txt).

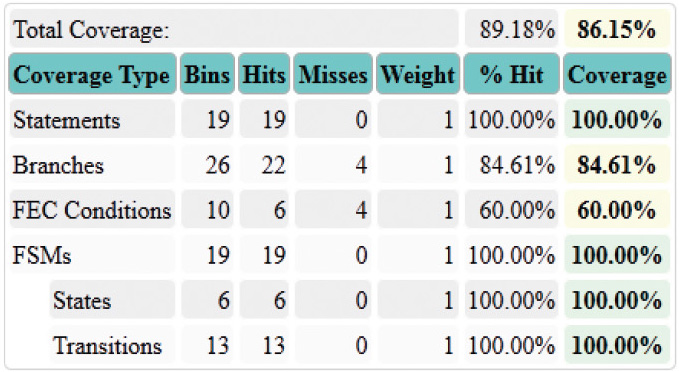

Кроме текстовых файлов отчётов, удобно получить итоговый отчёт в виде HTML-файла. Например, выполнив моделирование устройства system на 10 000 псевдослучайных входных наборов, можно добиться следующих результатов покрытия VHDL-кода (см. рис. 8).

В файле report.txt даётся подробный анализ причин того, почему не покрыта соответствующая VHDL-конструкция в той или иной строке. В данном примере непокрытыми явились строки VHDL-кода, в которых записаны условия переходов, – это и привело к тому, что нет 100% покрытия ветвей и условий в управляющем автомате. В книге [6] подробно описываются наиболее распространённые причины отсутствия таких покрытий. Например, условные операторы if должны иметь часть else, логические условия переходов должны быть ортогональными (не пересекаться) и т.д.

Заключение

Верификация на основе покрытия VHDL-кода может быть выполнена для VHDL-описаний проекта в целом, а не только для VHDL-описаний цифровых устройств, представленных в виде соединения управляющего и операционного блоков. Она позволяет найти «мёртвые» участки кода, проанализировать полноту применяемых тестов для моделирования, пересечение (ортогональность) логических условий и т.д. Другие, более сложные проблемы верификации решаются на основе функциональной верификации, которая рассматривается во второй части данной статьи. Там же будут более подробно описаны специальные средства системы моделирования Questa Sim, предназначенные для верификации конечных автоматов.

Литература

- Иванюк А.А. Проектирование встраиваемых цифровых устройств и систем. – Минск: Бестпринт, 2012.

- Поляков А.К. Языки VHDL и VERILOG в проектировании цифровой аппаратуры. – М.: СОЛОН-Пресс, 2003.

- Чэнь М., Цинь К., Ку Х.-М., Мишра П. Валидация на системном уровне. Высокоуровневое моделирование и управление тестированием. – М.: Техносфера, 2014.

- Лохов А., Рабоволюк А. Комплексная функциональная верификация СБИС. Система Questa компании Mentor Graphics // Электроника: наука, технология, бизнес. 2007. №3. с. 102–109.

- Бибило П.Н. Cистемы проектирования интегральных схем на основе языка VHDL. StateCAD, ModelSim, LeonardoSpectrum. – М.: СОЛОН-Пресс, 2005.

- Бибило П.Н., Авдеев Н.А. Моделирование и верификация цифровых систем на языке VHDL. – М.: ЛЕНАНД, 2017.

Если вам понравился материал, кликните значок — вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал —не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!