Всё разнообразие архитектур ЭВМ сводится к 4 классам вычислительных систем (ВС):

- ОКОД – ВС с одиночным потоком команд и одиночным потоком данных.

- ОКМД – ВС с одиночным потоком команд и множеством потоков данных.

- МКОД – ВС со множественным потоком команд и одиночным потоков данных.

- МКМД – ВС со множественным потоком команд и множеством потоков данных.

ОКМД представляет собой вычислительную систему с параллельной обработкой данных. К этому типу относятся так называемые «матричные процессоры». Они представляют собой массив процессоров, которые контролируются одним управляющим процессором, выполняя по его команде одну операцию над собственной порцией данных, хранящихся в локальной памяти. В связи с тем что обмена данными между процессорами нет, не требуется никакой синхронизации, что позволяет достигать огромных скоростей вычислений и легко расширять вычислительную систему, просто увеличивая количество процессоров.

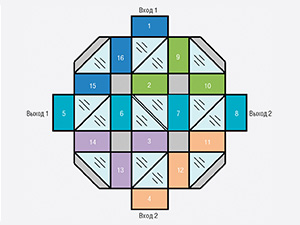

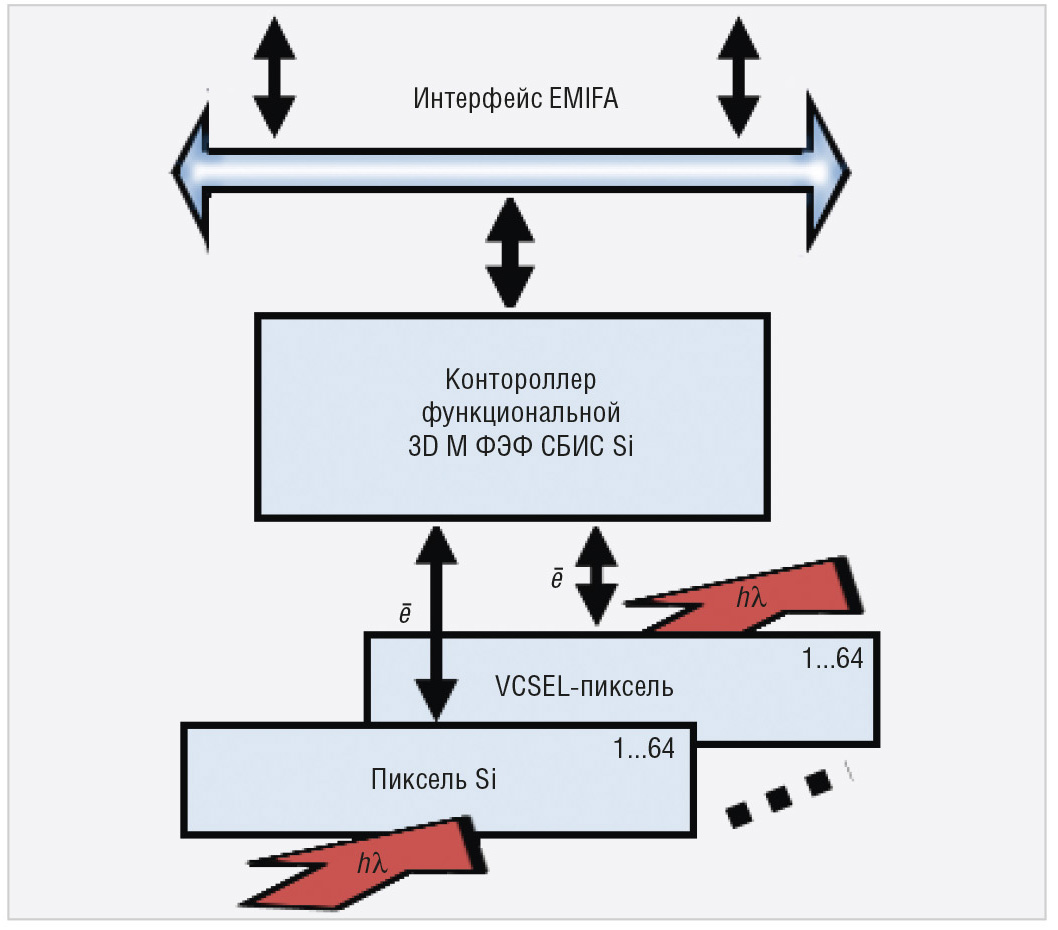

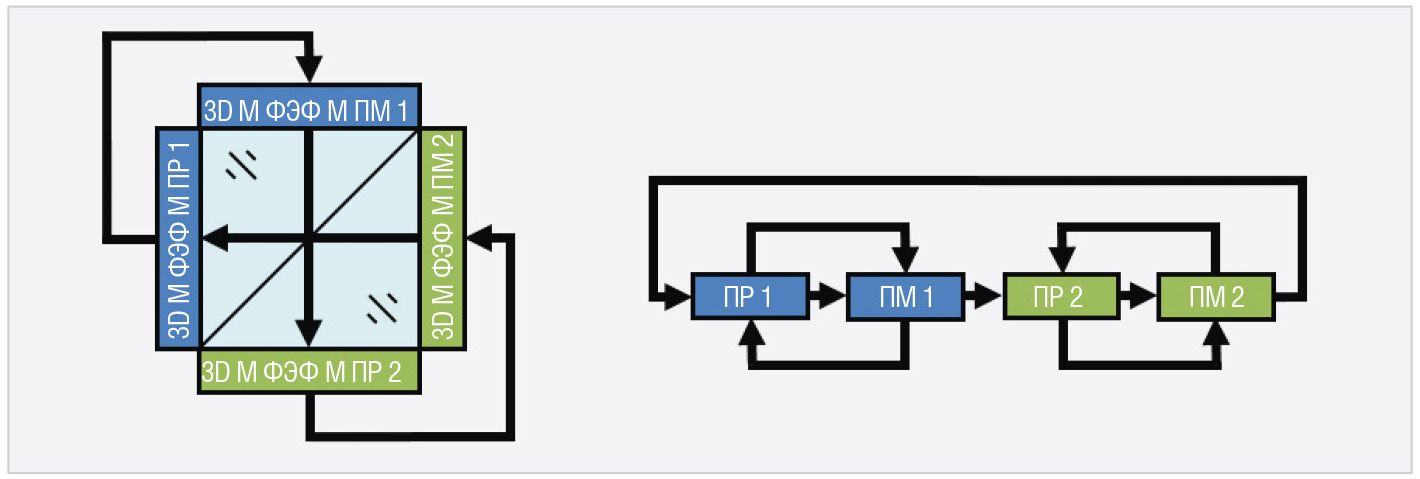

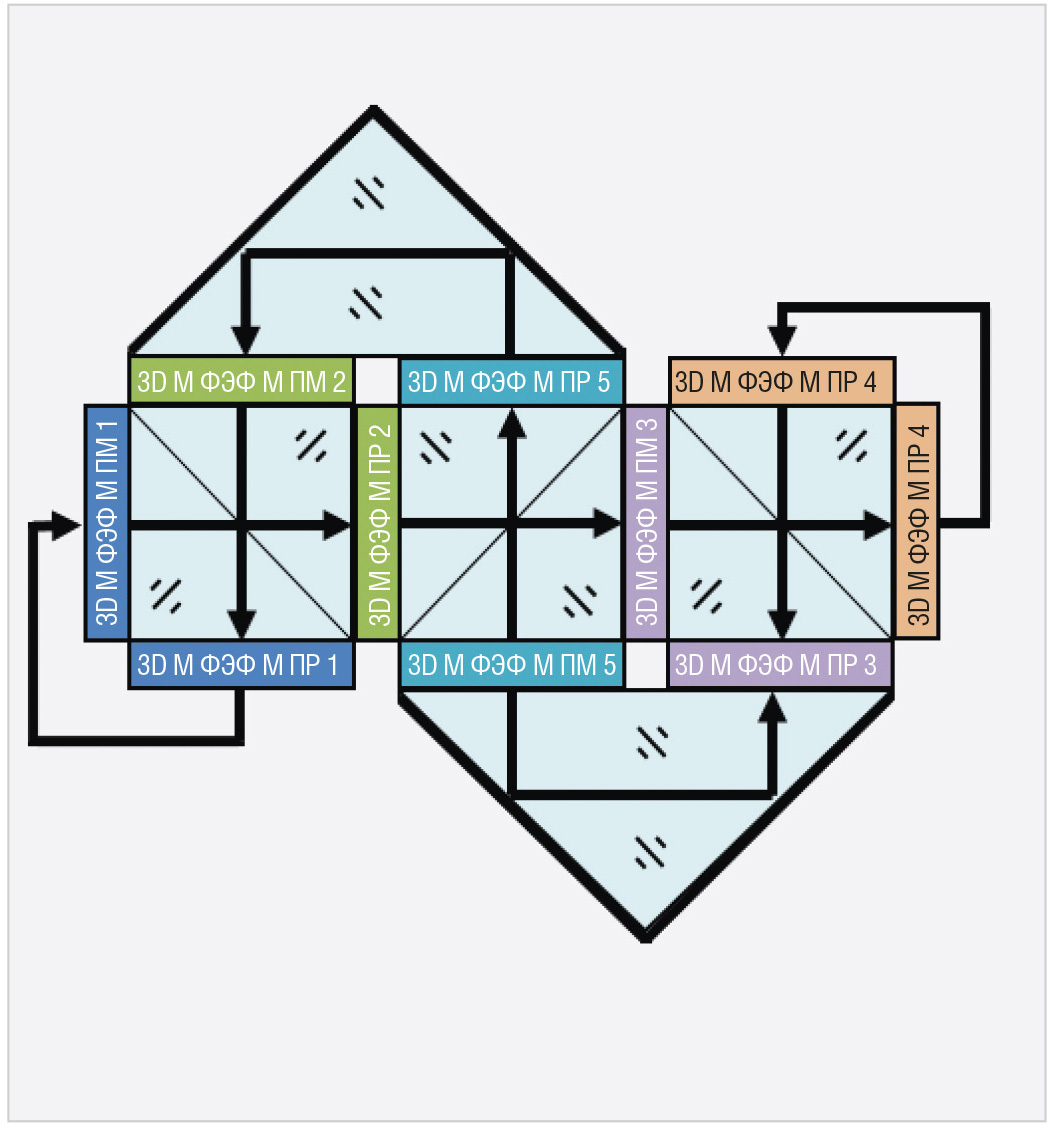

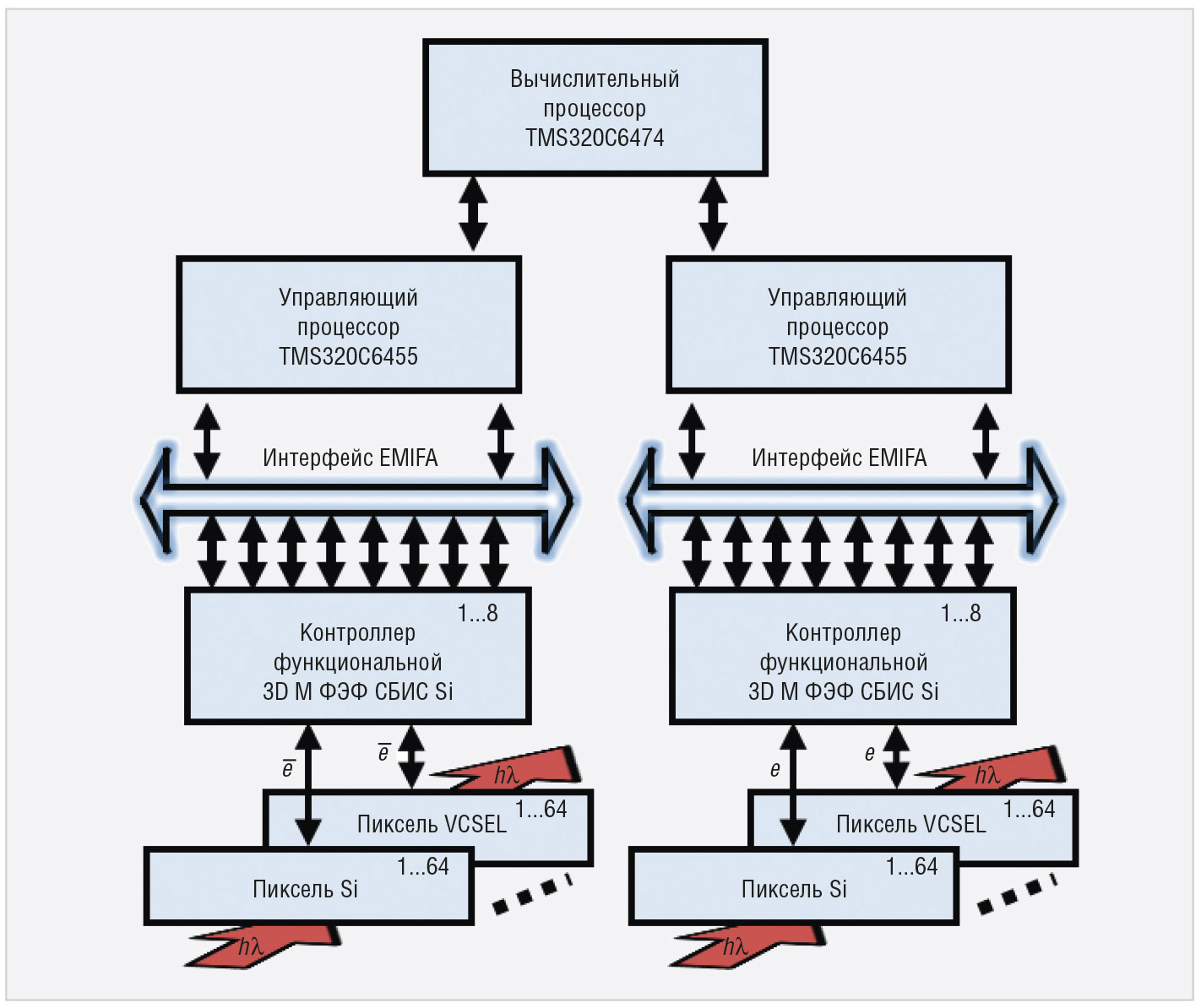

На рисунке 85 представлена структурная схема подключения функционального модуля 3D М ФЭФ М.

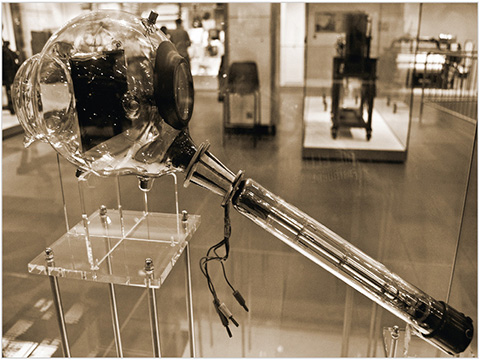

Скоростной порт ввода-вывода многоканальной оптической информации

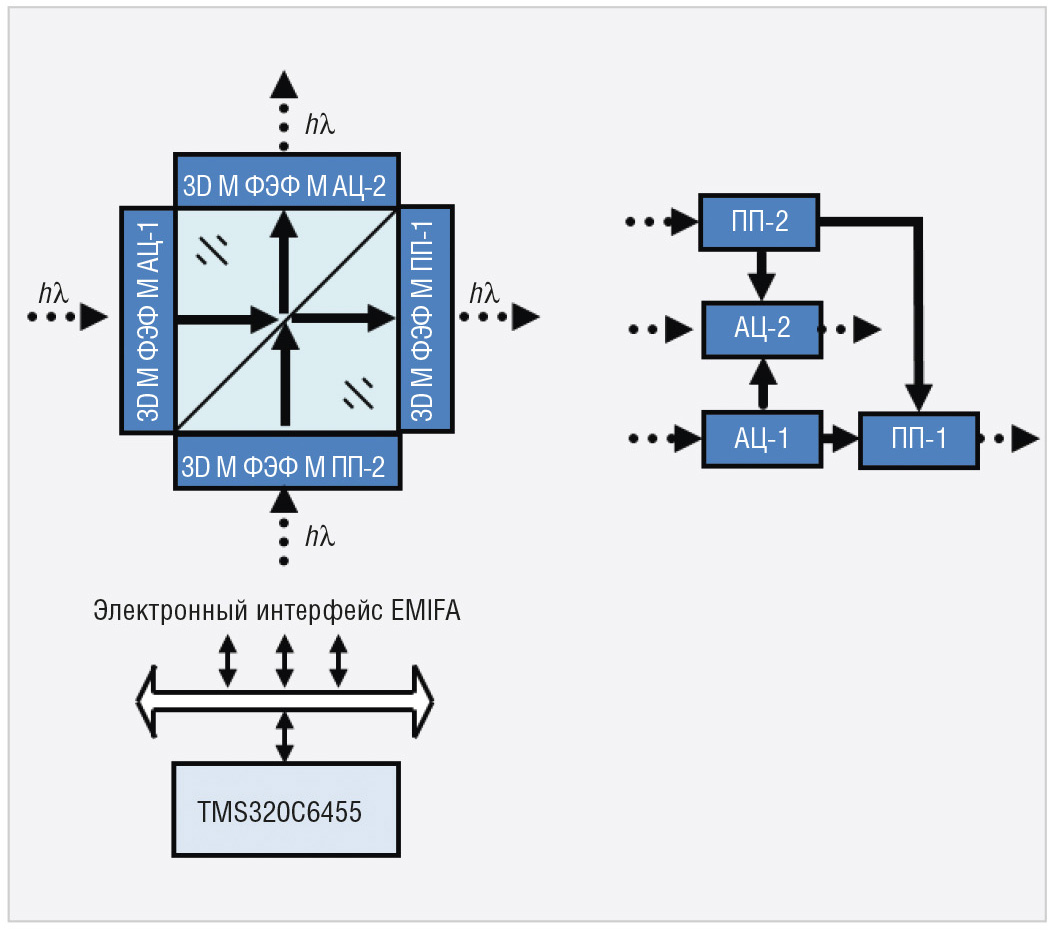

Скоростной порт ввода-вывода многоканальной оптической информации строится на базе двух 3D М ФЭФ М АЦ, двух 3D М ФЭФ М ПП и оптического многоканального призменного мультиплексора и обеспечивает однотактную аналоговую передачу цифровой информации слайса по оптическим каналам со скоростью до 1 ГГц.

На рисунке 86 представлена архитектура скоростного порта ввода-вывода многоканальной оптической информации.

С качественным улучшением структурных схем 3D М ФЭФ М Si с вводом в состав функциональных кристаллов схем АЦП – ЦАП необходимость в скоростном порте ввода-вывода может отпасть

Преобразование бит-последовательных и бит-параллельных потоков информации

При использовании 3D М ФЭФ М АЦ в качестве оптоэлектронного интерфейса возникает потребность в дополнительной обработке передаваемых через интерфейс данных для согласования форматов передачи информации через шины Serial RapidIO или Ethernet, реализующие электрический интерфейс с внешними устройствами, и EMIFA, связывающую процессор TMS320C6455 с кристаллом 3D М ФЭ СБИС А/Ц, который реализует оптический интерфейс модуля 3D М ФЭФ М АЦ.

Рассмотрим процесс передачи данных через модуль в направлении оптического интерфейса. Для того чтобы передать некоторые данные через кристалл (причём нет принципиальной разницы, в аналоговом или в цифровом виде производится передача), необходимо загрузить 8-разрядные регистры пикселей (каналов) кристалла. Кристалл обеспечивает одновременную передачу данных по 64 каналам, следовательно, для передачи одной порции данных потребуется подготовить 64 8-битных слова, т.е. 64 байта.

Данные, поступающие с интерфейсов RapidIO или Ethernet, должны приниматься процессором в виде пакетов, каждый байт которых (без учёта служебной информации пакета) должен хранить информацию, предназначенную для одного канала кристалла (бит-последовательный поток информации). Это связано с тем, что регистры пикселей кристалла имеют 8 разрядов и, соответственно, количество бит, передаваемое через один канал, должно быть кратно 8.

Байты данных каналов в пакете не обязательно должны быть расположены по порядку. Например, данные для каналов могут быть сгруппированы по 16 или 32 бита, но для упрощения дальнейшей обработки их стоит сгруппировать по 8 бит и расположить друг за другом в порядке возрастания номеров каналов, т.е. сформировать описанные выше порции данных. Для решения этой задачи имеет смысл использовать контроллер прямого доступа к памяти (EDMA3), который позволяет переставить байты в нужном порядке. При использовании этого механизма данные в пакете должны иметь регулярную структуру.

Контроллер прямого доступа к памяти позволяет выполнять операции по копированию/перестановке данных параллельно с выполнением других задач, решаемых на процессоре, и его производительность ограничивается только производительностью памяти, с которой он работает. Поскольку время, затрачиваемое на обработку порции данных, превышает время копирования этой порции данных, перестановка байт в нужном порядке не скажется на производительности.

Для того чтобы передать 8 бит в каждый из 64 регистров пикселей кристалла, необходимо сформировать 8 64-битных слов (слайсов), каждый бит которых соответствует одному каналу (бит-параллельный поток информации). Иными словами, в нулевом слайсе передаются нулевые биты всех каналов, в первом – первые и т. д. Нулевой бит в каждом слайсе соответствует нулевому каналу, первый – первому и т. д. После этого достаточно будет последовательно выдать эти слайсы через шину EMIFA. С точки зрения программирования это означает просто скопировать их в область памяти, в которой отображается адресное пространство EMIFA, что может быть сделано с помощью контроллера EDMA3 параллельно с обработкой без дополнительных затрат вычислительных ресурсов.

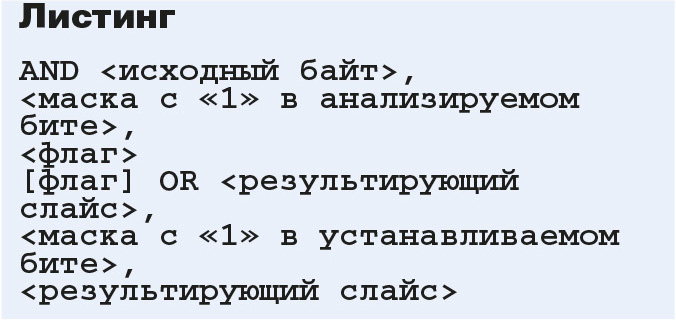

Таким образом, задача обработки сводится к преобразованию 64-байтной порции данных, полученной из пакетов RapidIO или Ethernet, в слайсы. Рассмотрим код на ассемблере TMS320C64x+, позволяющий эффективно решить эту задачу.

Данный процессор имеет 64 32-битных регистра (2 банка по 32 регистра), что является достаточным для того, чтобы при обработке одной порции данных не требовалось выгружать и загружать промежуточные результаты в память: они целиком могут умещаться в регистрах.

Вся суть обработки данных сводится к двум операциям:

- Анализ бита в одном из исходных байтов.

- Запись аналогичного значения в соответствующее место одного из 64-битных слайсов.

Для того чтобы проанализировать один бит и установить один бит со значением, аналогичным значению проанализированного бита, достаточно двух последовательных ассемблерных инструкций (при условии, что регистры результирующих слайсов были предварительно обнулены) (см. листинг).

Архитектура процессора позволяет выполнять до 6 таких проверок одновременно (на различных исполнительных устройствах).

Маски, используемые в инструкциях AND и OR, имеет смысл предварительно загрузить в свободные регистры. При этом нет возможности (недостаточно регистров) подготовить заранее все возможные маски. Если учесть, что маски не используются одновременно, становится ясно, что в этом нет необходимости. Нужные маски можно получить из масок, подготовленных заранее, с помощью ассемблерной инструкции ROTL, которая может выполняться на умножителях. Поскольку умножители непригодны для осуществления логических операций, выполнение ROTL никак не скажется на производительности описанного ранее решения.

Помимо возможности одновременной обработки 6 бит данных для одного канала, существует возможность считывать из памяти во внутренние регистры процессора данные сразу для 8 каналов (8 последовательных байт вместо одного) с помощью команды LDDW. Использование данной команды эффективнее, чем использование 8 отдельных команд чтения байта, т.к. выработка адреса для памяти производится только один раз.

Оценим производительность описанного преобразования бит-после-довательного потока информации в бит-параллельный. С учётом возможности параллельной обработки 6 бит для преобразования одной порции данных (64 байта) процессору необходимо выполнить 176 инструкций (с учётом чтения исходных данных). Также дополнительно требуется выполнить 8 инструкций записи сгенерированных слайсов в память, которые не могут выполняться параллельно. Всего получается 184 инструкции на порцию данных.

Если для хранения данных используется быстродействующая внутренняя память (L1D или L2), то можно избежать дополнительных задержек, связанных с ожиданием ответа от внешнего ОЗУ. В частности, при использовании L1D время выполнения одной инструкции равно одному такту тактового генератора процессора (0,83 нс при частоте 1,2 ГГц), что обеспечивает производительность алгоритма обработки в 3,3 Гбит/с.

Преобразование бит-параллельного потока информации, полученного от кристалла, в бит-последовательный может выполняться аналогичным образом с такой же производительностью, как и преобразование битпоследовательного потока информации в бит-параллельный.

Вычислительная архитектура 3D М ФЭФ М ПСЦ

Вычислительная архитектура 3D М ФЭФ М ПСЦ позволяет создавать различные вычислительные структуры и реализовывать конвейерную или векторную формы параллелизма вычислений.

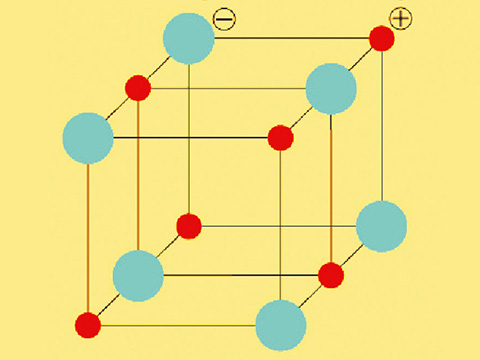

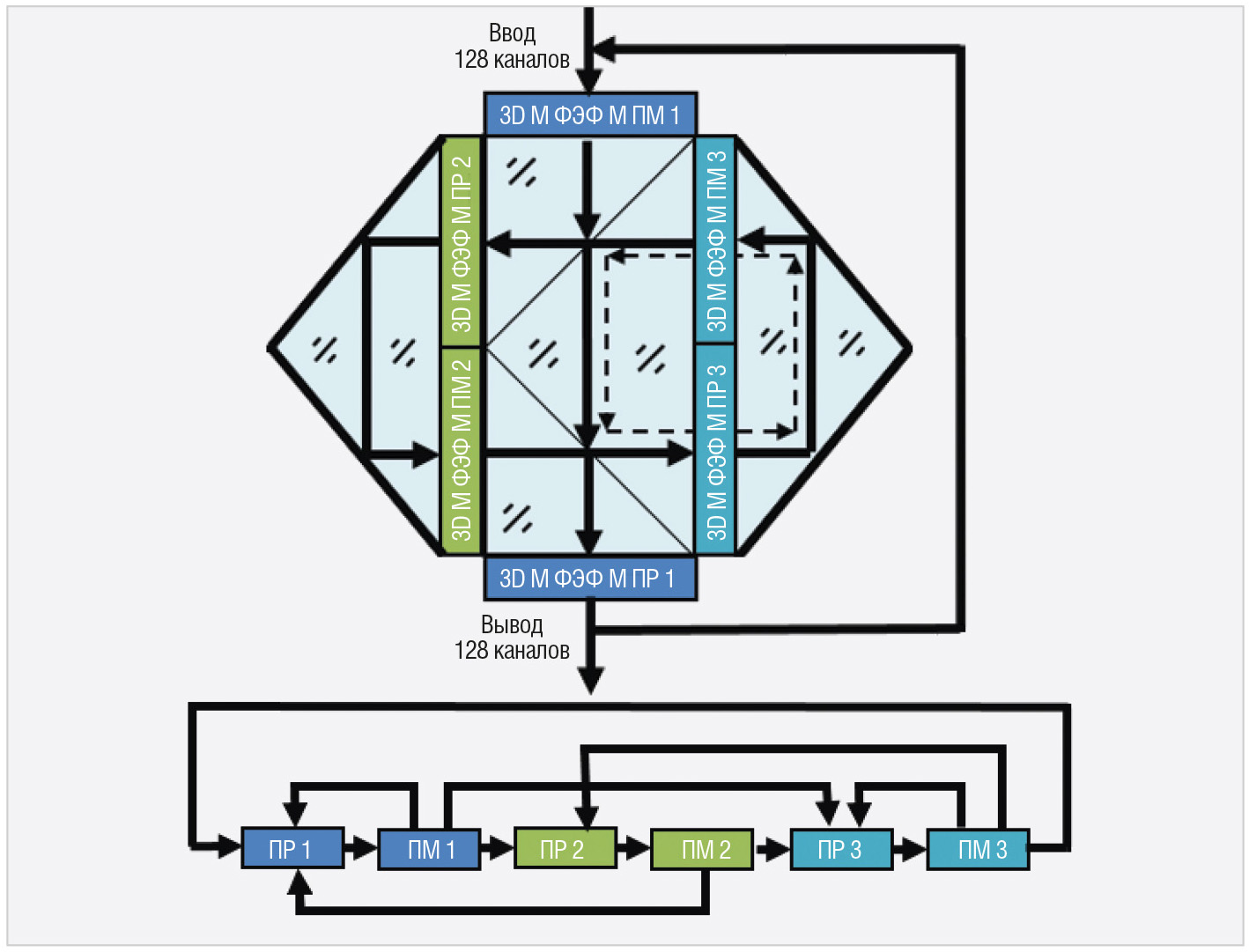

Цифровые векторно-матричные потоковые вычислители – 3D М ФЭФ М ПСЦ – строятся на основе вычислительного ядра с параллельной обработкой данных на базе 3D М ФЭФ М ПФ, 3D М ФЭФ М ПП с АЦП – ЦАП разрядностью 28 и оптического многоканального призменного мультиплексора с многоканальной обратной связью и обеспечивают однотактную аналоговую передачу цифровой информации слайса по оптическим каналам со скоростью до 1 ГГц (см. рис. 87).

В вычислительном ядре процессорные пиксели 3D М ФЭФ М ПФ одновременно обращаются к пикселям общей внешней памяти 3D М ФЭФ М ПП по оптическому интерфейсу.

3D М ФЭФ М ПП имеет возможность перестановки содержимого регистра данных в пикселях матрицы.

Управление операционными процессами в 3D М ФЭФ М ПФ и 3D М ФЭФ М ПП производится электронным процессором TMS320C6455 по шине EMIFA.

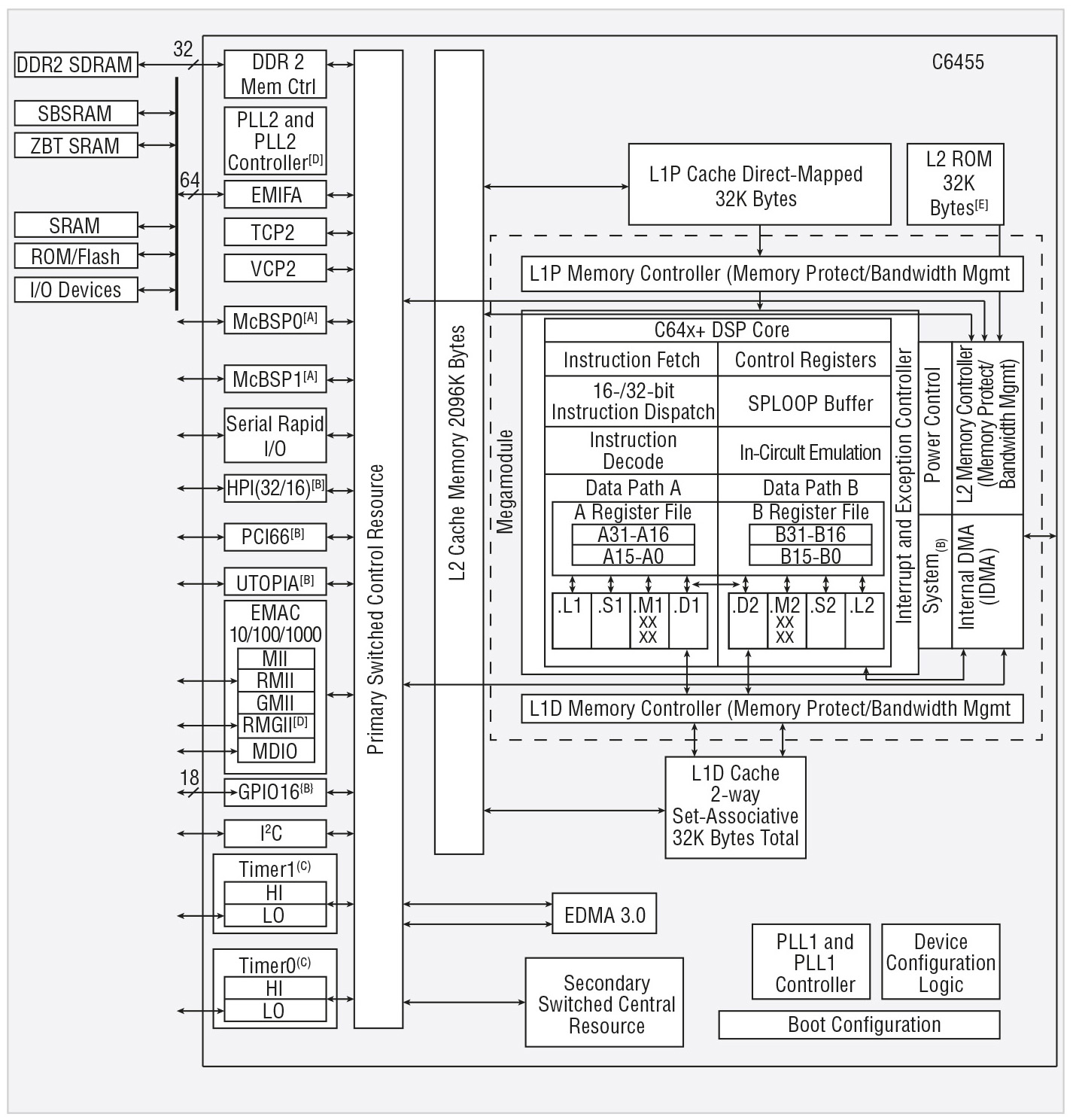

Технические характеристики ПЦОС ТМS320C6455

Процессор цифровой обработки сигналов TMS320C6455, выпускаемый компанией Texas Instruments, предназначен для высокопроизводительной обработки информации и интенсивного обмена данными с внешними устройствами по высокоскоростным интерфейсам. Поколение процессоров C64x+, в которое входит TMS320C6455, включает в себя самые производительные из всех ПЦОС с фиксированной точкой, выпускаемых компанией Texas Instruments.

TMS320C6455 обладает следующими отличительными особенностями:

- время одного цикла процессора – 1,39; 1,17; 1; 0,83 нс;

- тактовая частота – 720, 850 МГц, 1,0; 1,2 ГГц;

- максимальная производительность – 9600 MIPS;

- температурный диапазон – 0…+90°C (-40…+105°C в расширенном температурном исполнении);

- вычислительное ядро C64x+;

- обработка данных с фиксированной точкой;

- расширенная VLIW-архитектура;

- выполнение до 8 инструкций за такт;

- специализированные SPLOOP-коман-ды (эффективная реализация циклов);

- компактные коды инструкций (16 бит вместо 32);

- расширенная система команд (по сравнению с C64x);

- поддержка обработки исключений;

- внутренняя память;

- кэш-память программ первого уровня (L1P) – 32 Кбайт;

- кэш-память данных первого уровня (L1D) – 32 Кбайт;

- кэш-память второго уровня (L2) – 2048 Кбайт;

- возможность использования части кэш-памяти данных в качестве быстродействующего ОЗУ;

- ПЗУ – 32 Кбайт;

- аппаратные расширенные декодеры VCP2 и TCP2;

- счётчик тактовых импульсов, не зависящий от работы вычислительного ядра;

- возможность поддержки как прямого (Little Endian), так и обратного (Big Endian) порядка байт в слове;

- 64-битный интерфейс с внешней памятью (EMIFA);

- подключение как асинхронной, так и синхронной памяти;

- поддержка интерфейсов логических устройств (ПЛИС и др.);

- тактовая частота шины – 166 МГц;

- общий объём адресуемой памяти – 32 Мбайт;

- Serial Rapid IO v1.2;

- четыре 1x канала, которые могут быть сконфигурированы как один 4x канал;

- скорость передачи – 1,25; 2,5; 3,125 Гбит/с;

- поддержка передачи сообщений и Direct IO;

- расширенный контроль ошибок и управление трафиком;

- совместимость с IEEE 1149.6;

- контроллер внешнего ОЗУ;

- интерфейс к памяти типа DDR2 SDRAM;

- 16/32-битная шина;

- тактовая частота шины – 533 МГц;

- общий объём адресуемой памяти – 512 Мбайт;

- контроллер прямого доступа к памяти (EDMA3), поддерживающий 64 независимых канала;

- 16/32-битный Host-Port Interface (HPI);

- 32-битный 33/66 МГц 3,3 В Peripheral Component Interconnect (PCI) v2.3;

- шина I2C;

- 2 многоканальных буферизованных последовательных порта (McBSPs);

- Ethernet MAC (EMAC);

- совместимость с IEEE 802.3;

- скорость передачи – 10/100/1000 Мбит/с;

- поддержка MII, GMII, RMII и RGMII;

- 8 независимых каналов передачи (TX) и 8 независимых каналов приёма (RX);

- 2 64-битных таймера общего назначения, которые могут быть сконфигурированы как 4 32-битных таймера;

- UTOPIA;

- Slave ATM контроллер второго уровня;

- 8-битные независимые операции приёма и передачи с частотой 50 МГц;

- определяемый пользователем формат ячейки (до 64 байт);

- 16 выводов общего назначения (GPIO);

- контроллер ФАПЧ;

- дополнительный контроллер ФАПЧ для EMAC и DDR2;

- расширенное управление событиями (AET);

- пошаговая отладка программ, исполняемых на процессоре;

- JTAG-интерфейс, совместимый с IEEE-1149.1;

- поддержка Boundary-Scan режима JTAG;

- корпус BGA, имеющий 697 выводов (расстояние между выводами – 0,8 мм);

- КМОП-технология 90 нм с 7-уровневой металлизацией;

- напряжение питания цепей ввода-вывода – 3,3/1,8/1,5/1,2 В;

- напряжение питания ядра – 1,25/1,2 В.

Параллельно работающие матричные вычислительные ядра с топологией «кольцо» внешней и внутренней многоканальной оптической связи обеспечивают повышение производительности архитектур вычислительных систем с параллельной обработкой данных.

В потоковой вычислительной архитектуре 3D М ФЭФ М ПСЦ процессоров имеются две независимые магистрали обмена данными и сигналами управления: матричная оптическая и регистровая электрическая с интерфейсом EMIFA.

Минимальная скорость обмена данными между 3D М ФЭФ М ПФ и 3D М ФЭФ М ПП при тактовой частоте 133 Мгц составляет 133 МГц × 8 бит = =1,064 Гбит/с.

Общий поток между 3D М ФЭФ М ПФ и 3D М ФЭФ М ПП составляет 133 МГц × 8 бит × 128×2 (одновременный приём, обработка и передача данных) = =272,384 Гбит/с.

Вычислительная архитектура 3D М ФЭФ М ПСЦ с наращиваемой 3D-платформой вычислительных ядер имеет ограничения на количество их подключений по шине EMIFA. В 3D-наращиваемой платформе может стоять до 10 вычислительных ядер с 3D М ФЭФ М.

Двунаправленные электрические драйверы кристаллов 3D М ФЭФ М устроены так, что при таком количестве абонентов на шине они не могут обеспечивать приемлемые времена установки (setup time) для процессора TMS320C6455 при требуемой тактовой частоте. При частоте 166 МГц такт занимает 6,25 нс, время установки TMS320C6455 – 2 нс. Остаётся 4,25 нс на формирование данных. Драйверы с этим не справятся.

Предлагается решение с использованием буферного регистра. Рассмотрим конфигурацию, когда на шину данных TMS320C6455 подключаются 5 ПЛИС (например, EMP570). К каждой ПЛИС подключены шины данных двух кристаллов 3D М ФЭФ М. Внутри ПЛИС реализован 64-битный регистр, когда в зависимости от направления передачи данных каждый такт запоминает данные либо с ПЛИС, либо с шины TMS320C6455, т.е., с точки зрения логики работы шины, в шину данных вносится задержка в 1 такт относительно других сигналов. Эту задержку можно учесть программно в TMS320C6455. При записи в кристалл 3D М ФЭФ М нужно будет выдавать на шину EMIFA данные на один такт раньше.

Например, при записи (расшифровка обозначения: в паре (0:Х) 0 – адрес, Х – данные): (0:Х), (0:Y), (1:Z), (2:*). NOP – несуществующий адрес, * – что угодно. При чтении достаточно прочитать на 1 слово больше и учесть, что первое считанное слово является мусором.

Существует ещё один вариант решения проблемы с использованием регистра. Можно задержать все сигналы шины EMIFA (кроме SOE: он используется для определения направления передачи данных), а не только шину данных.

Возможен вариант, когда кристалл 3D М ФЭФ М подключается к разным выводам одной ПЛИС, что, возможно, сделает достижимыми более высокие тактовые частоты, но тогда придётся ставить ПЛИС на мезонинную плату рядом с кристаллом 3D М ФЭФ М.

С точки зрения электрических параметров имеем:

- уменьшенную ёмкостную нагрузку на кристалл 3D М ФЭФ М;

- время установления ПЛИС – 1,7 нс;

- более короткие линии связи кристалла 3D М ФЭФ с ПЛИС и ПЛИС с TMS320C6455.

- В итоге на шине EMIFA процессора TMS320C6455 будет 5 абонентов вместо 10.

- Для этого приемлемы следующие параметры ПЛИС:

- Setup Time ≤ 1,2 нс;

- Hold Time = 0 нс;

- Cio ≤ 8 пФ – ёмкость пина общего назначения;

- Tpd ≤ 5,4 нс – время распространения сигнала от входа до выхода (без регистра).

Управляющий микропроцессор TMS320C6455 имеет тактовую частоту до 1,2 ГГц и производительность 2,9 МIPS/мВт.

Вычислительный микропроцессор TMS320C6475 имеет тактовую частоту до 1,2 ГГц и производительность

4 МIPS/мВт.

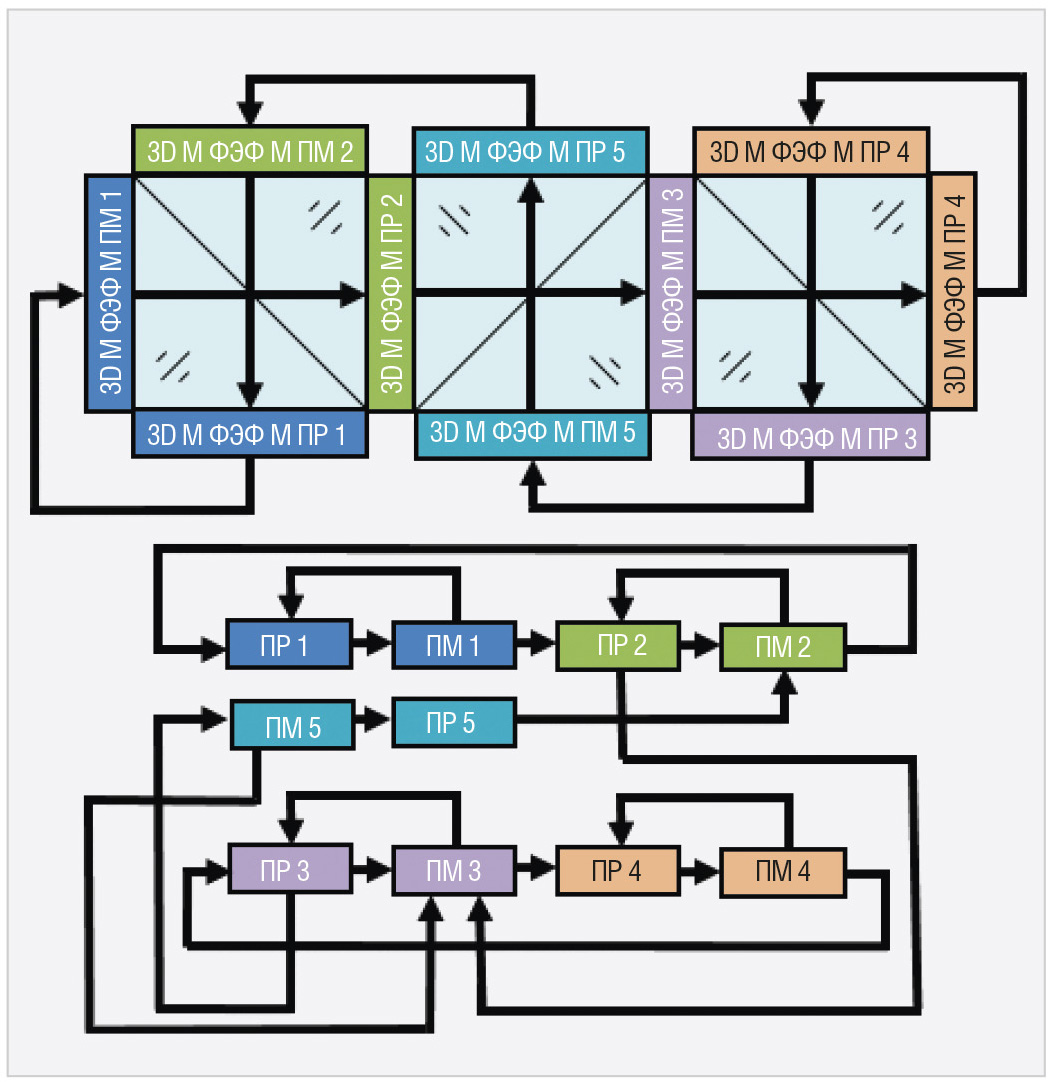

Варианты архитектур матричных потоковых вычислительных систем (МП ВС) с наращиваемыми параллельно работающими вычислительными ядрами с топологией «кольцо» внешней и внутренней связей представлены на рисунках 88–91.

В данных архитектурных решениях 3D М ФЭФ М ПСЦ могут быть успешно применены системные вычислительные алгоритмы, разработанные для процессорной системы «Мультиклет» с матричной пиксельной процессорной организацией вычислителей.

Аналого-цифровой векторно-матричный потоковый вычислитель 3D М ФЭФ ПСАЦ

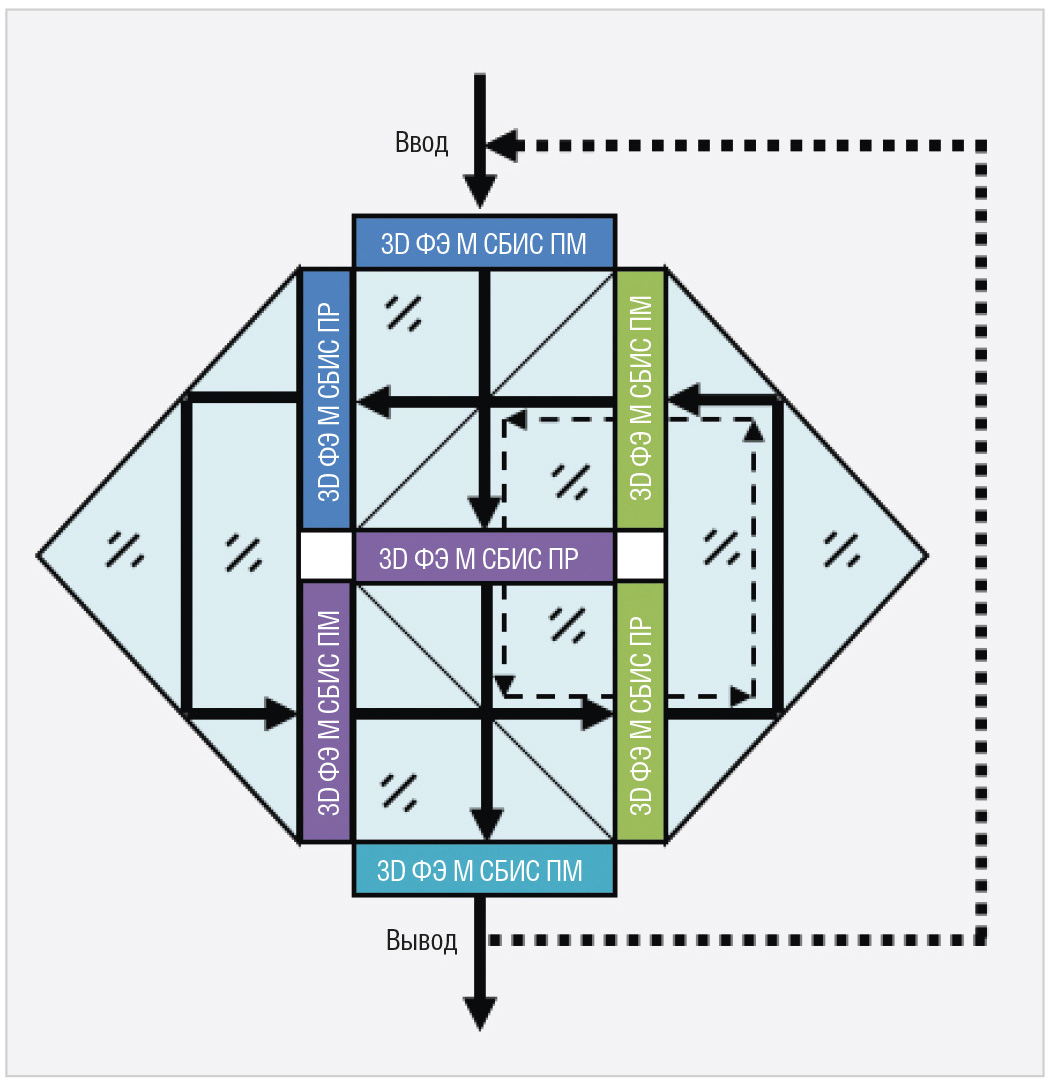

Достоинством аналоговых и цифровых векторно-матричных вычислителей, разработанных на базе 3D М ФЭФ М, является возможность реализации гибридной архитектуры – аналого-цифровых векторно-матричных потоковых вычислителей (см. рис. 92).

Состав алого-цифрового векторно-матричного потокового вычислителя:

- 6 модулей аналоговых векторно-матричных потоковых умножителей;

- 2 модуля цифровых векторно-матричных потоковых 3D М ФЭФ М ПФ.

Алгоритм обработки информации аналого-цифрового векторно-матричного потокового вычислителя позволяет вести обработку цифровой информации с помощью модуля 3D М ФЭФ М ПФ. Результаты соответствующих 3-модульных аналоговых векторно-матричных потоковых умножителей передаются последовательно в виде операндов «А» и «Б» на цифровые модули 3D М ФЭФ М ПФ.

Матричная пространственно-временна¢я потоковая вычислительная среда с 16 функциональными 3D М ФЭФ М

Матричная пространственно-временна¢я потоковая вычислительная система по принципу функционирования представляет собой вычислительный акселератор, управляемый скоррелированным потоком команд и потоком векторных данных, подключённый на правах внешнего устройства к управляющему процессору TMS320C6455 или TMS320C6475 через процессорную шину EMIFA.

Наличие системной команды ввода-вывода «транзит» переводит данную матричную потоковую вычислительную ситему в категорию архитектуры «вычислительная среда» с произвольным конвейерным временны¢м трафиком доступа к соответствующим функциональным 3D М ФЭФ М. Это позволяет реализовывать гибкие последовательные циклические и линейные цепочки вычислительных алгоритмов, используя возможность реконфигурации аппаратных средств. Все 3D М ФЭФ М в данной вычислительной системе работают синхронно и одновременно по конвейерному принципу. В 3D М ФЭФ М реализован ввод-вывод информации по многоканальным электрическим и оптическим линиям связи. Для данной конструкции матричной пространственно-временно¢й по-токовой вычислительной системы реализованы 3D М ФЭФ М с 4 функциональными 3D М ФЭФ СБИС и организована матрица размерностью 8×32 – 256-пиксельный слайс. В вычислительной системе постоянно циркулирует информация по 4096 оптическим каналам.

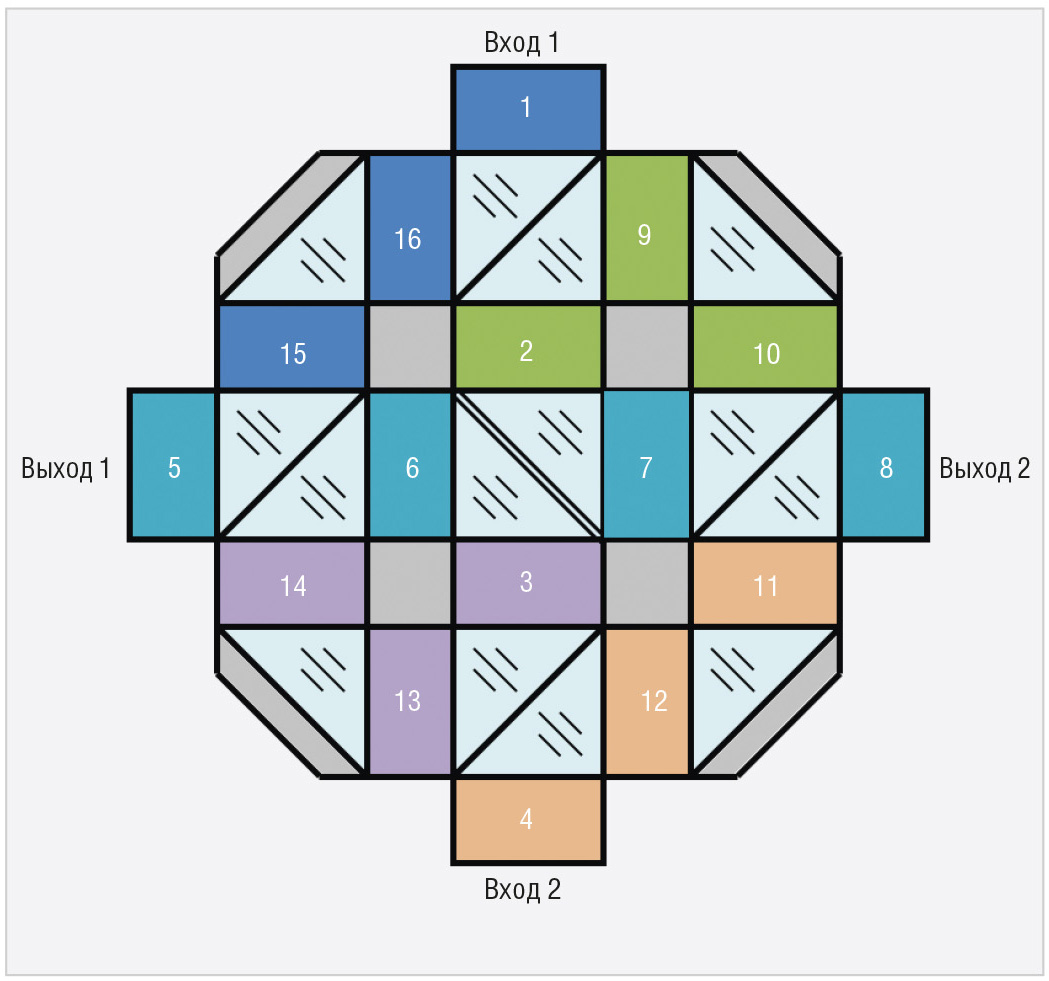

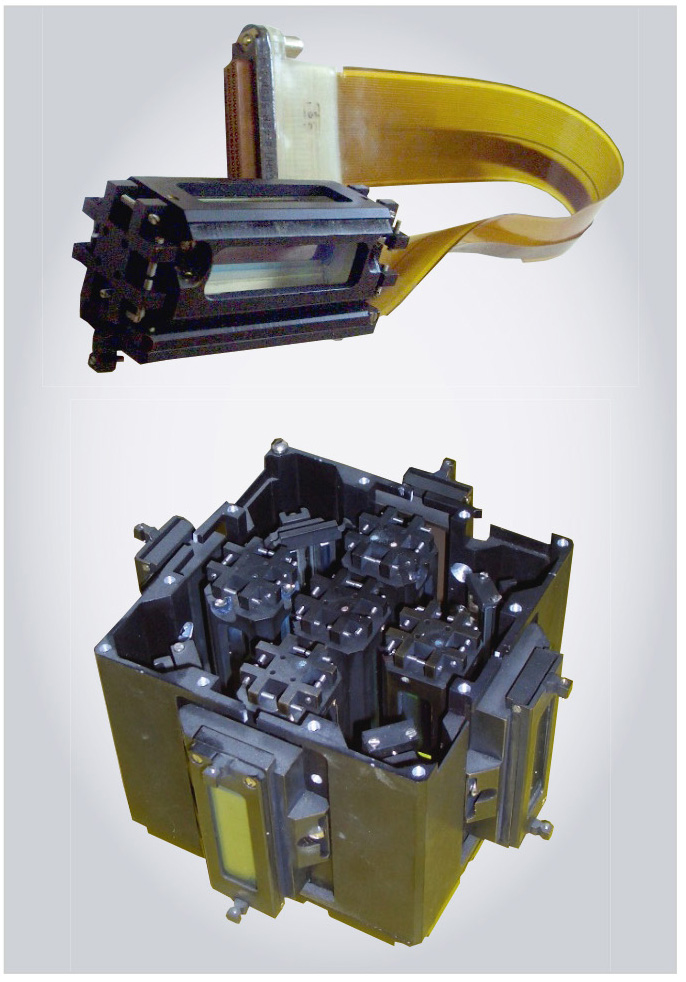

На рисунке 93 представлена схема макетного образца матричной пространственно-временно¢й потоковой вычислительной системы (МП-В ВС) с 16 функциональными 3D М ФЭФ М базового ряда с оптическими пространственными связями и оптическими мультиплексными элементами – призмами, реализующими многоуровневую транспортную многоканальную связь.

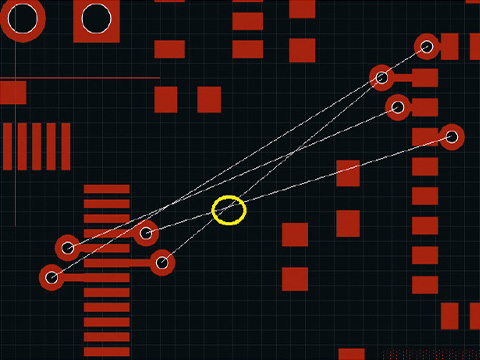

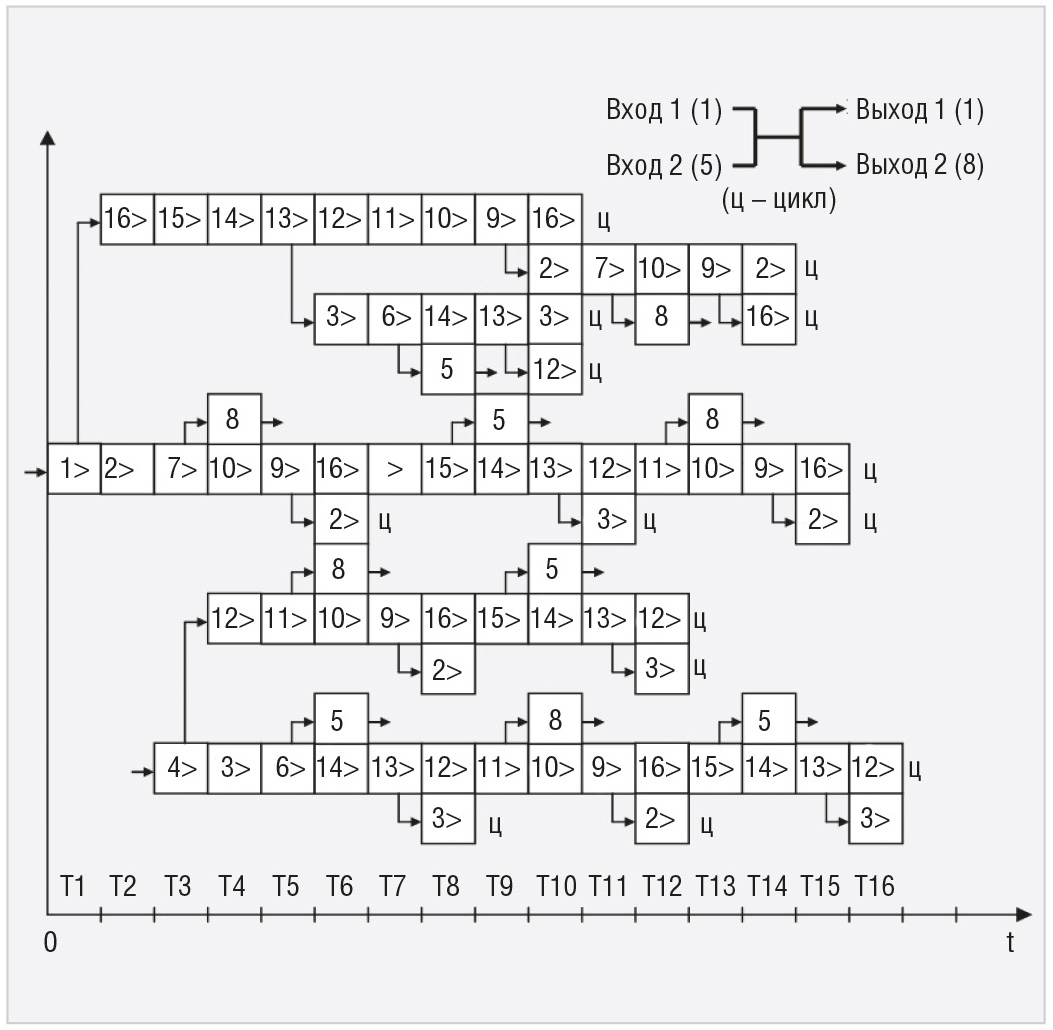

На рисунке 94 показан трафик неблокируемого потока многоканальной оптической информации.

Конструкция МП-В ВС представляет собой оптико-механический блок с двумя многоканальными оптическими входами и двумя многоканальными выходами и содержит 16 функциональных 3D М ФЭФ М, 5 оптических мультипрексных призм, 3 прямоугольные зеркальные призмы и одну пространственно сдвигающую зеркальную призму. Оптические мультиплексные призмы предназначены для мультиплицирования оптического информационного потока. Прямоугольные зеркальные призмы предназначены для передачи многоканальной информации с зеркальной инверсией данных многоканальных пикселей, а пространственно сдвигающая зеркальная призма осуществляет пространственный сдвиг столбцов с инверсией данных многоканальных пикселей. Каждый функциональный 3D М ФЭФ М имеет электрический 16-разрядный порт с АЦП для связи с внешними сигнальными источниками и порт связи по интерфейсу EMIFA с управляющим процессором TMS320C6455.

Масштабируемые системы с DSP TMS320C6455

Архитектура DSP процессора TMS320C6455 позволяет реализовывать масштабируемые системы на уровне различных шин, в том числе с помощью шины EMIFA для подключения фотонных массивно-параллельных вычислительных систем, а шины PCI – для подключения персональных компьютеров. На рисунке 95 представлена функциональная схема TMS320C645.

Архитектурные решения на базе масштабируемой системы DSP TMS320C6455 и фотон-электронных векторно-матричных массивно-параллельных потоковых вычислительных систем позволяют реализовать любые вычислительные функции аналого-цифровой и цифровой сигнальной информации, в том числе функцию диаграммообразования для многоканальных ЦИФАР.

Архитектурные решения, заложенные в матричной пространственно-временно¢й потоковой вычислительной системе, позволяют реализовать вычислительную функцию диаграммообразования для многоканальной ЦИФАР (см. рис. 96), где входные (1, 4) и выходные (5, 8) оптические скоростные порты – 3D М ФЭФ М АЦ с 512 оптическими каналами связи.

На рисунке 97 представлена схема управляющих процессоров TMS320С6455 и вычислительного процессора TMS320С6474 в матричной пространственно-временно¢й потоковой вычислительной среде с 16 функциональными 3D М ФЭФ М; формат матрицы – 8×32 – 256 пикселей.

Архитектура вычислителя с МП-В ВС позволяет выполнять непрерывный поток системных вычислительных алгоритмов одновременно с выполнением локальных алгоритмов в функциональных 3D М ФЭФ М с матрично-пиксельной процессорной организацией вычислителей.

В следующей части будут представлены оптоэлектронный многоканальный коммутатор стандарта SpaceWire и концепция ФЭ информационно-вычислительной системы для ЦИФАР с цифровым диаграммообразованием, а также разработка ЦИФАР для радиотехнических систем с учётом современных достижений науки и техники на базе технологии радиофотоники и построение оптоэлектронной цифровой интеллектуальной 3D М ФЭФ М ЦИФАР.

Если вам понравился материал, кликните значок — вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал —не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!