Базовый ряд

Базовый ряд оптоэлектронных элементов с матричной организацией функциональных пикселей, разработанный предприятием ООО «ОЭС» состоит из шести основных 3D М СБИС, где 3D M ФЭ (ЭФ) – трёхмерный модуль преобразования фотонных сигналов в электронные и наоборот:

- 3D М ЭФ СБИС VCSEL – матрица лазеров вертикального излучения;

- 3D М ФЭ СБИС ПФ – матрица процессоров с потоковой обработкой функции расщеплённого алгоритма БПФ;

- 3D М ФЭ СБИС ПП – матрица пиксельной памяти с функцией перестановки;

- 3D М ФЭ СБИС А/Ц – матрица АЦП/ЦАП амплитудно-модулированных фотонных сигналов для удалённой связи по многоканальным оптическим и локальным электрическим каналам связи;

- 3D М ФЭ СБИС НП – матрица нейропроцессоров с коммутацией каналов для выполнения основной нейрооперации – умножение с аккумулированием;

- 3D М ФЭ СБИС SW – матрица коммутации каналов для удалённой связи по многоканальным оптическим и локальным электрическим каналам связи аэрокосмического стандарта SPACE WIRE.

3D М ЭФ СБИС базового ряда являются операционными устройствами с матрицей функциональных пикселей и контроллером управления с шиной EMIFA.

Матрицы лазеров вертикального излучения – 3D М ЭФ СБИС VCSEL

В предыдущей статье (см. №5, 2017) было представлено описание технологии получения структур вертикально-излучающих лазерных диодов – VCSEL (Vertical-Cavity Surface-Emitting Laser) с диапазоном длин волн 850 и 980 нм. Данные диоды являются элементами для создания матриц лазеров вертикального излучения – 3D М ЭФ СБИС VCSEL.

Технологический процесс изготовления матричных излучателей

Технологический процесс изготовления матричных излучателей основан на процессах сухого травления пучком Ar под маской фоторезиста и селективного окисления апертурных слоёв AlGaAs.

Изготовление кристалла начинается с формирования металлизации p-контактов. После травления мезоструктуры до активной области и селективного окисления апертурных слоёв производится второе сухое травление для вскрытия контактного слоя n-GaAs и формирования металлизации n-контактов. После этого осуществляется пассивация приборной структуры слоем SiO2, вскрытие контактных окон, формирование металлизации контактных площадок, защита поверхности структуры полиимидом и формирование контактных столбиков.

При создании матричных излучателей дополнительно приходится принимать во внимание возможность обеспечения группового монтажа индивидуально излучающих элементов. Кроме того, массив лазерных излучателей требует специальных условий по решению проблемы тепловыделения при работе большого количества излучателей. Так массив из 64 быстродействующих лазеров вертикального излучения с диаметром токовой апертуры 18 мкм обеспечивает суммарную выходную мощность 275 мВт при частоте токовой модуляции 7,5 ГГц.

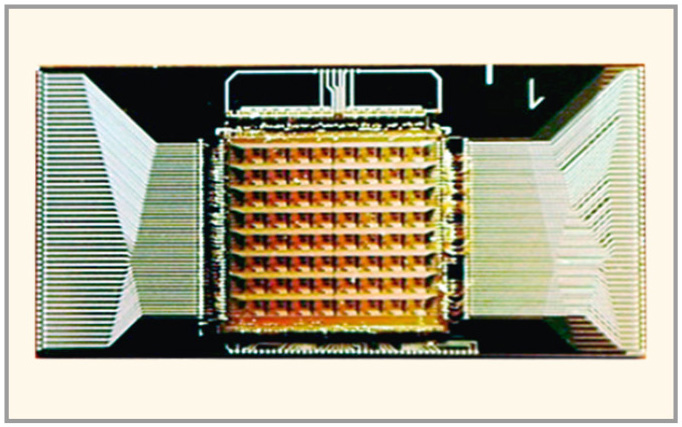

На рисунке 20а представлена фотография кристалла матрицы VCSEL, а на рисунке 20б показан фрагмент кристалла со стороны контактных площадок.

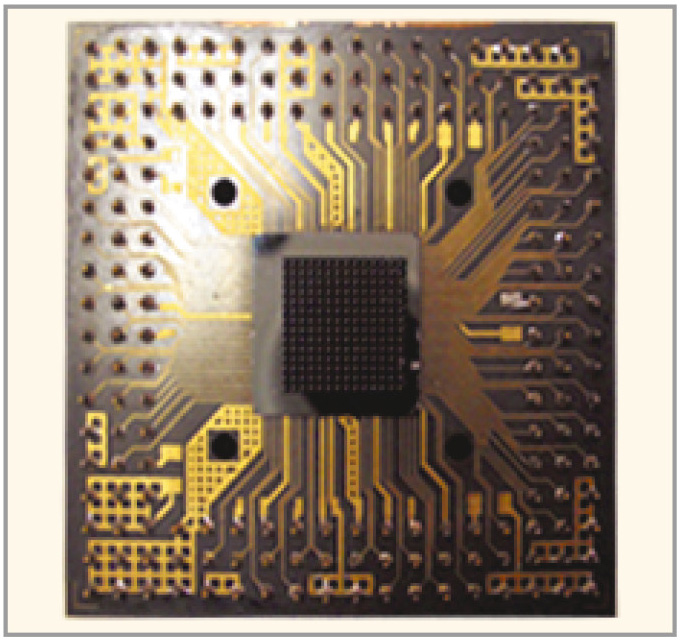

На рисунке 21 представлена фотография монтажной платы для установки 3D М ЭФ СБИС VCSEL.

Технические характеристики 3D М ЭФ СБИС VCSEL

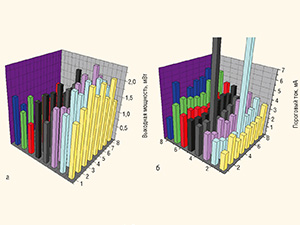

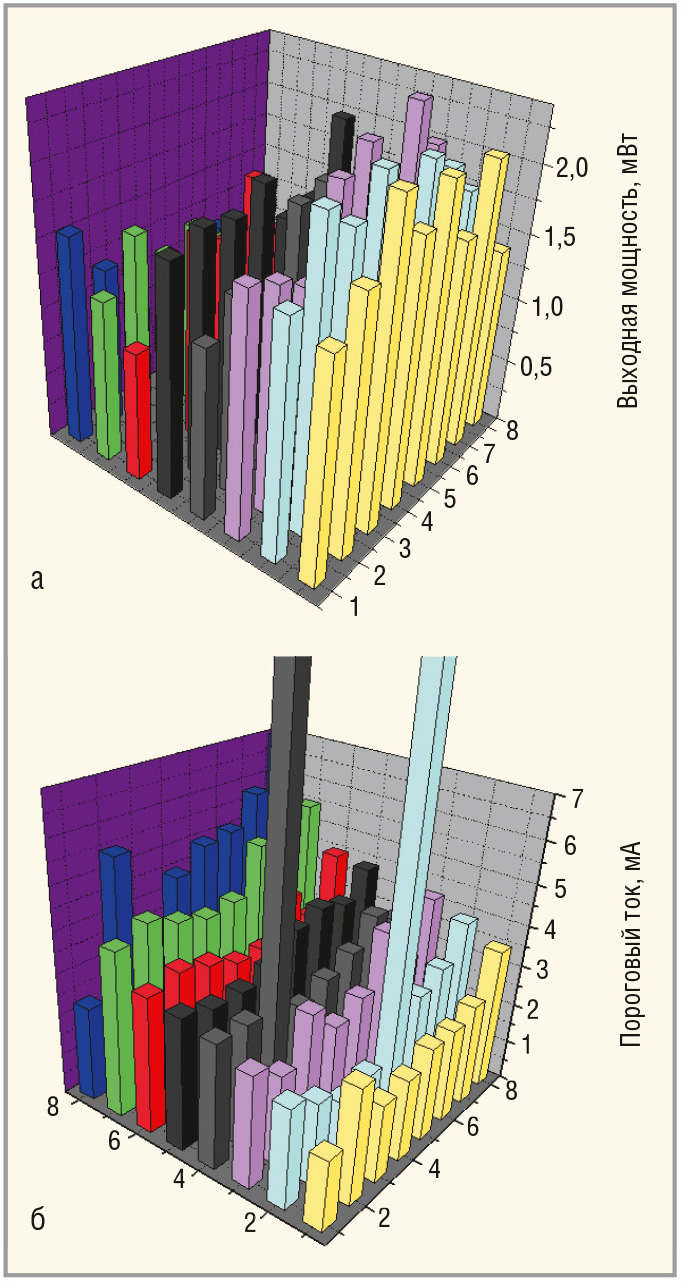

Технические характеристики 3D М ЭФ СБИС VCSEL соответствуют параметрам вертикально излучающих диодов, которые были описаны в части 3 (см. №5, 2017). На рисунке 22 приведены результаты измерения распределения порогового тока и максимальной выходной мощности индивидуальных ВИЛ по площади одного из изготовленных матричных излучателей (в непрерывном режиме при комнатной температуре).

Таким образом, М ЭФ СБИС VCSEL реализует передачу дискретных бинарных или многоуровневых амплитудно-модулированных информационных сигналов и предназначена для скоростного обмена информацией по многоканальным оптическим линиям связи.

Матрица АЦП/ЦАП амплитудно-модулированных фотонных сигналов – 3D М ФЭ СБИС А/Ц

Матрица АЦП/ЦАП – амплитудно-модулированных фотонных сигналов, 3D М ФЭ СБИС А/Ц, – предназначена для выполнения функций аналого-цифровой и цифроаналоговой обработки входной информации и для реализации импульсного аналого-цифрового и (или) цифроаналогового интерфейса параллельного преобразования входной информации, передаваемой по 64 оптическим каналам в электрический цифровой код, а также обратного преобразования электрического цифрового кода в токовый сигнал для генерации лазерными диодами цифрового или аналогового сигналов по 64 оптическим каналам.

В соответствии с концепцией кремниево-фотонной технологии в матрице аналого-цифровых/цифроаналоговых преобразователей сформирован двумерный массив (2D) кремниевых фотодиодов по мембранной технологии и совмещён с фотоусилителями и аналого-цифровыми функциональными устройствами в едином объёме интегрального кремниевого кристалла.

Сам кристалл 3D М ФЭ СБИС А/Ц представляет собой матрицу оптоэлектронных преобразователей размером 8 × 8 пикселей с шагом 1 мм, функциональная схема которого была приведена в уже упомянутой 3-й части.

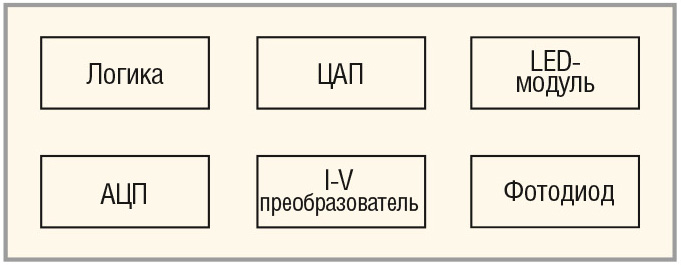

Каждый пиксель 3D М ФЭ СБИС А/Ц включает в себя: приёмный фотодиод, преобразователь ток-напряжение, 8-разрядный ЦАП, 8-разрядный АЦП, площадку для монтажа анода внешнего VCSEL, регистры и логику управления.

Функции кристалла 3D М ФЭ СБИС А/Ц

Матрица АЦП/ЦАП амплитудно-модулированных импульсных фотонных сигналов выполняет следующие функции:

- приём оптической информации в цифровом или аналоговом режимах и преобразование её в токовый сигнал;

- преобразование токового сигнала в напряжение и его индивидуальная калибровка для устранения ошибок, связанных с разбросом оптических и электрических характеристик излучателей;

- аналого-цифровые преобразования калиброванного напряжения;

- формирование нормированного тока лазерного диода для передачи оптической информации в цифровом или аналоговом режимах;

- чтение/запись данных с/на внутреннюю шину;

- управление режимами ЦАП и АЦП – аналоговый/цифровой;

- сдвиг для преобразования параллельного кода в последовательный и обратно.

Все эти функции позволяют кристаллу 3D М ФЭ СБИС А/Ц вести параллельную обработку и передачу сигналов по многоканальным оптическим и локальным электрическим каналам связи.

Особенности аналоговых схем кристалла 3D М ФЭ СБИС А/Ц

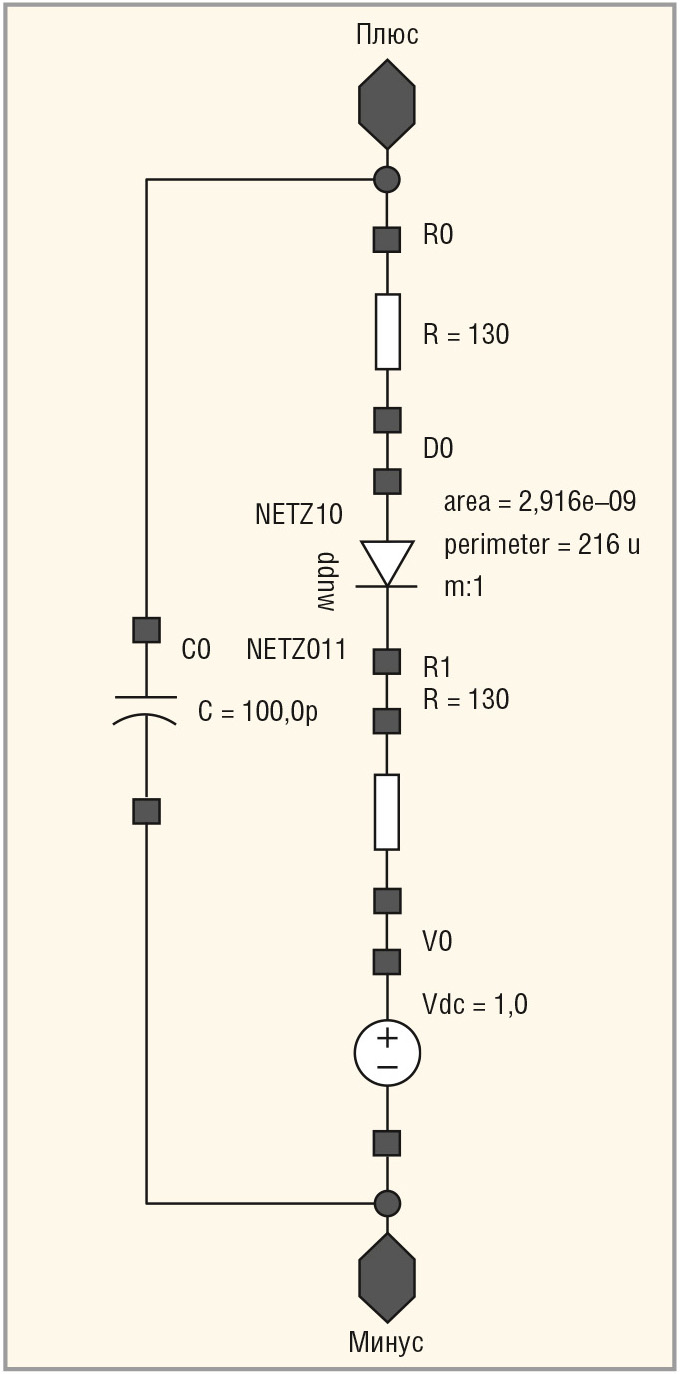

Цифроаналоговый преобразователь (ЦАП) 3D М ФЭ СБИС А/Ц является 8-разрядным с токовым выходом и предназначен для формирования тока лазерного диода. Токовой нагрузкой ЦАП является лазерный диод (ЛД) с током начала линейной зоны излучения 1,7 мА. Принимая этот ток за ток смещения нуля ЦАП (ток при нулевом входном коде ЦАП) и задавая типовой ток единицы младшего разряда 10 мкА, получаем типовой ток полной шкалы ЦАП 1,7 мА + 255 × 10 мкА = 4,25 мА. На рисунке 23 представлена электрическая схема модели VCSEL.

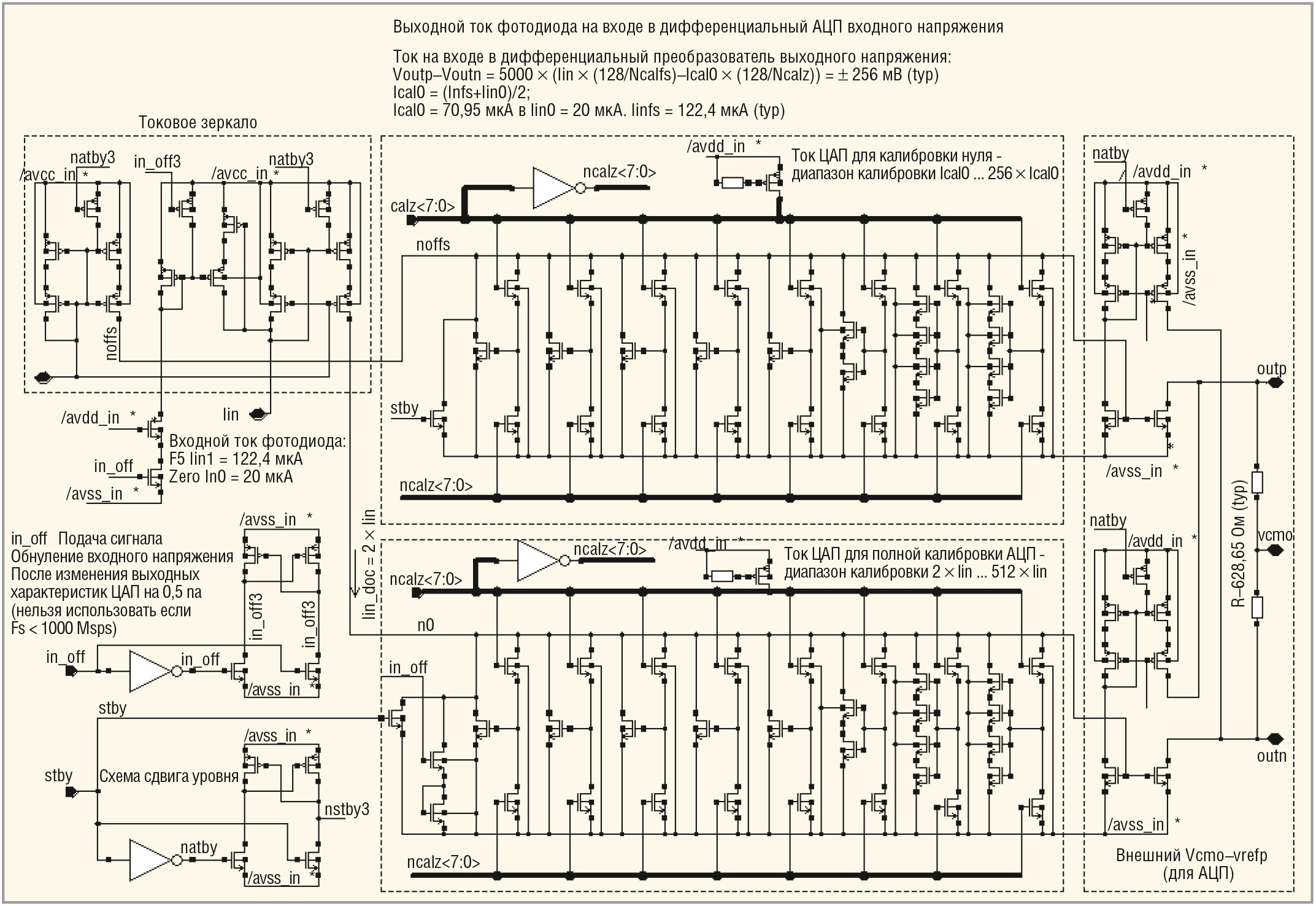

С учётом требований, предъявляемых к фотодиодам, разработана схема in_scale преобразователя тока фотодиода в дифференциальное выходное напряжение, представленная на рисунке 24.

Схема преобразователя тока фотодиода в дифференциальное напряжение имеет два 8-разрядных токовых ЦАП для подстройки (калибровки) нуля и полной шкалы дифференциального напряжения V(outp-outn) на выходах преобразователя. ЦАП калибровки выполнены на n-МОП токовых зеркалах. С учётом неопределённой величины тока смещения нуля лазерного диода, каждый пиксель имеет токовые выводы Iph_exc(схема pixel) и Ical0.

Ток, задаваемый через выводы Iph_exc в каждый пиксель, одинаковый и должен отводить с выхода фотодиода излишний ток, обеспечивая оптимальный для преобразователя ток нуля 20…40 мкА, равный разности тока фотодиода при приёме нулевого сигнала (Iin0) и тока вывода Iph_exc.

Подстройка выходного напряжения полной шкалы преобразователя, равного положительной разности опорных напряжений АЦП V(refp-refn), обеспечивается индивидуально для каждого пикселя заданием калибровочного кода calfs<7:0>.

Входной каскад преобразователя питается от источника повышенного напряжения Vcc = 3,3 В для обеспечения на фотодиоде напряжения не менее 2 В. Выходной каскад преобразователя и ЦАП калибровки питаются от источника напряжения Vdd = 1,8 В для уменьшения площади кристалла и потребляемой мощности.

Таким образом, каждый пиксель в составе ГИМС осуществляет до 160 млн А/Ц- или Ц/А-преобразований в секунду. Общая производительность 3D М ФЭ СБИС А/Ц составляет более 20 млрд А/Ц- или Ц/А-преобразований в секунду при тактовой частоте 160 МГц. Кристалл 3D М ФЭ СБИС А/Ц работает под управлением микропроцессора TMS320C6455 по шине EMIFA с максимальной тактовой частотой до 166 МГц.

Устройство управления организует работу матрицы пикселей. Для этого формируется набор управляющих сигналов. Часть из них являются общими для всех пикселей, другая часть служит для выбора пикселей. Особенностями управления являются:

- выполнение потока команд, поступающих с внешней шины данных;

- механизм отложенной команды, позволяющий синхронизировать действия нескольких оптически связанных кристаллов;

- микропрограммирование команд загружаемым микрокодом;

- общая шина данных для загрузки микрокода, потока команд, загрузки и выгрузки информационных и калибровочных регистров пикселей;

- выбор пикселей, участвующих в операциях: отдельный пиксель – строка – столбец – вся матрица;

- внешняя шина данных совместима с TMS320.

Технология изготовления кристалла и элементной базы

Как уже говорилось, кристалл 3D М ФЭ СБИС А/Ц изготавливается по технологии 180 нм КМОП SOI фирмы XFAB с технологическими нормами XT018. Выбор этой технологии обусловлен введением в данный технологический процесс опции фотодиодов, то есть она имеет необходимые особенности изготовления:

- базовый технологический модуль: стандартный 1,8 В КМОП с 3,3 В периферией (MOS3ST);

- наличие в разрабатываемом кристалле быстродействующих аналоговых схем АЦП, ЦАП и преобразователя тока в напряжение требует использования технологических модулей изолированных транзисторов (ISOMOS) для изоляции аналоговых схем от цифровых шумов логической части кристалла, высокоомных поликремниевых резисторов (HRPOLY), металлических конденсаторов (MIM);

- сложность разводки большого количества аналоговых схем с раздельным питанием и большой ток потребления обусловил выбор модуля разводки с пятью металлами и шестым толстым металлом (5М + THKMET).

Структура логической части кристалла

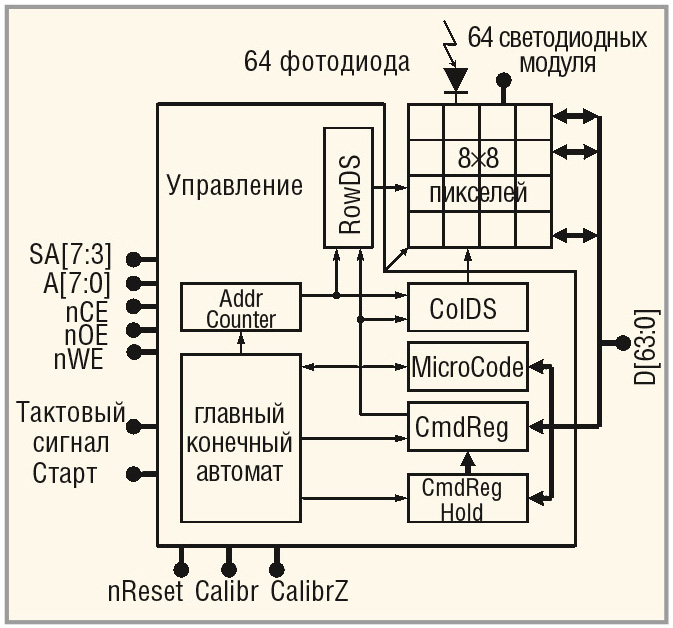

В структуру логической части кристалла 3D М ФЭ СБИС А/Ц входят функциональные блоки, представленные на рисунке 25.

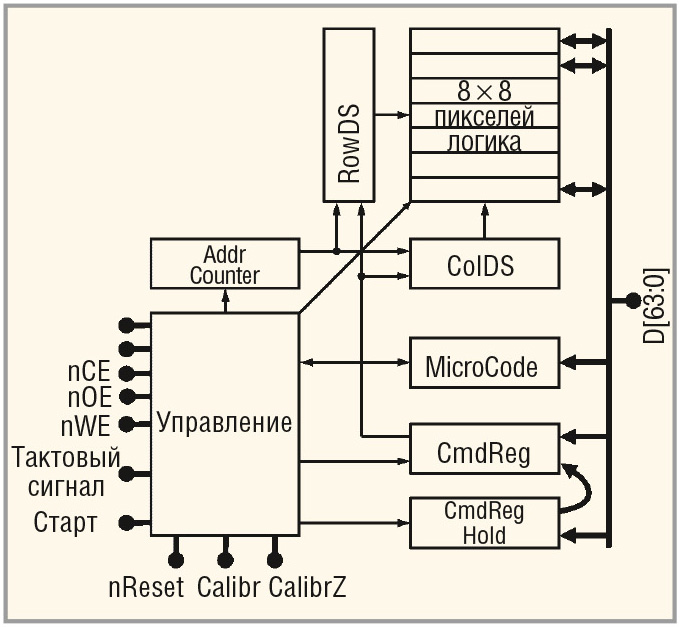

Основные функциональные блоки логической части, присутствующие в кристалле: устройство управления – «Control», регистр команды – «CmdReg», регистр отложенной команды – «CmdRegHold», регистровый файл микрокода – «MicroCode», счётчик адреса – «AddrCounter», дешифратор строк – «RowDS», дешифратор столбцов – «ColDS», логика пикселей – «PixelLog».

Взаимодействие функциональных блоков изображено на рисунке 26.

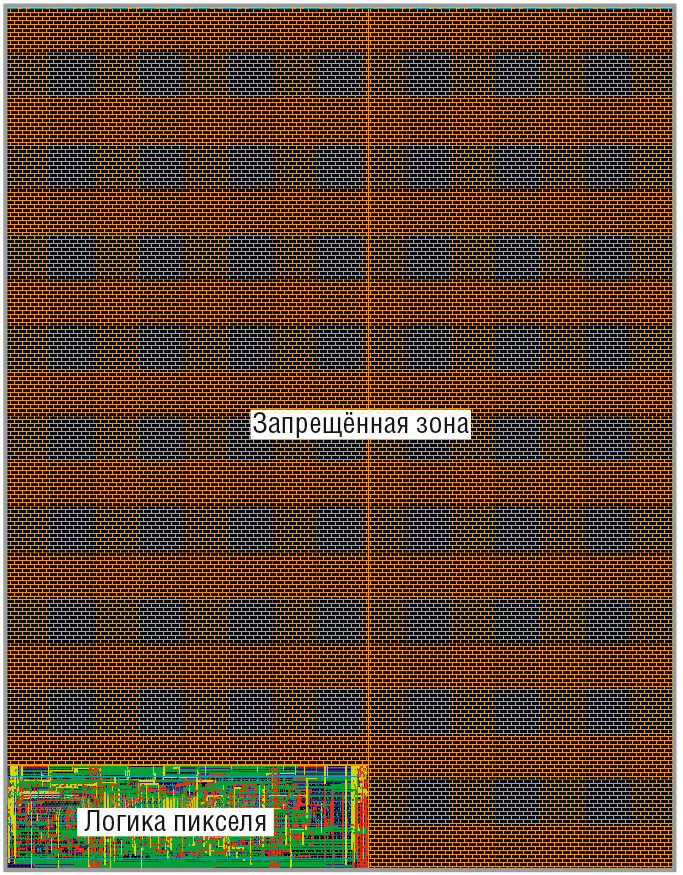

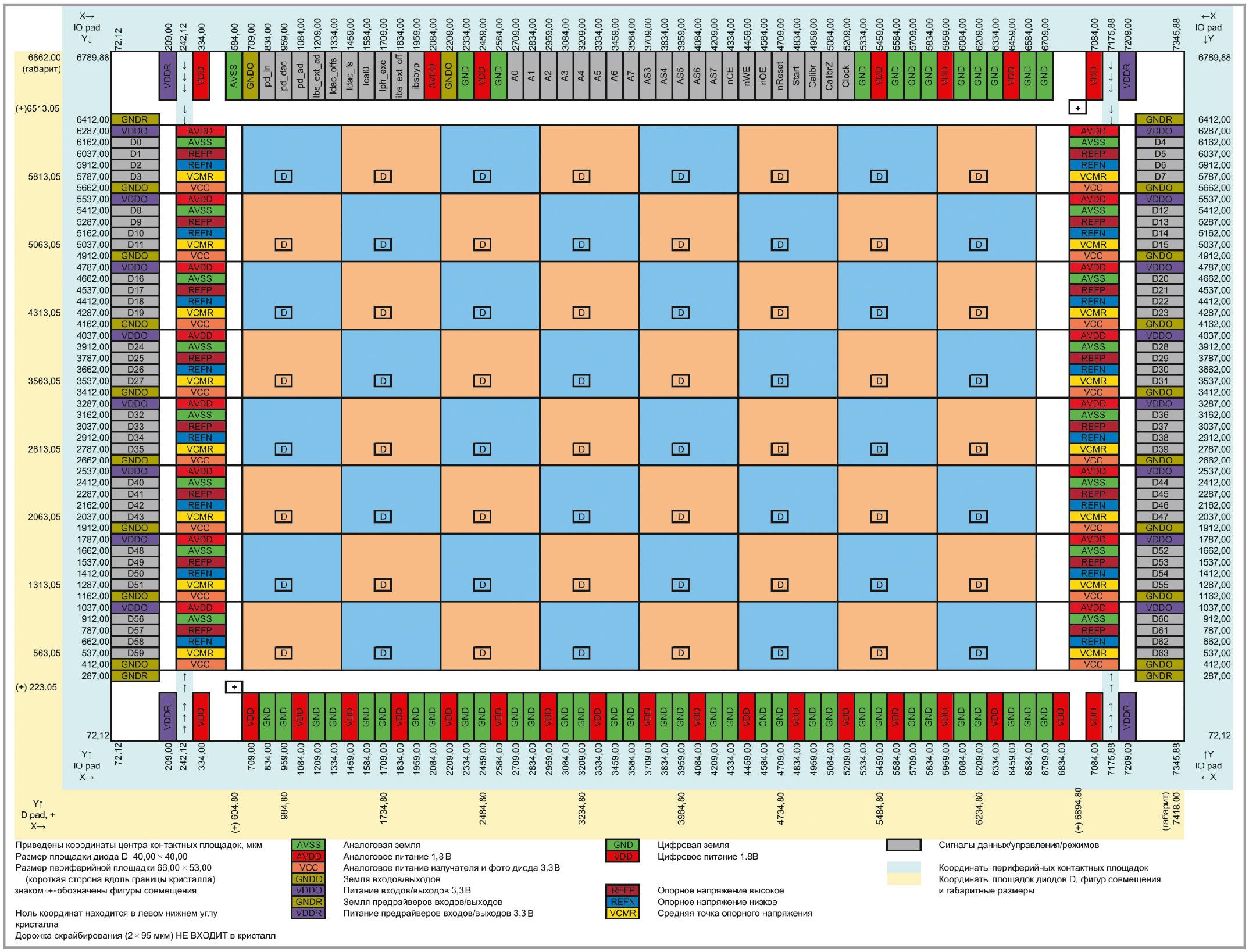

Топология кристалла А/Ц и взаимодействие функциональных блоков

Топология кристалла представляет собой матрицу пикселей 8 × 8 и кольцо периферийных ячеек (см. рис. 27). Между рядами пикселей находятся горизонтальные и вертикальные каналы, используемые для трассировки и размещения вентилей верхнего уровня. В каналах также размещаются элементы структуры тактирования и буферы оптимизации временны¢х параметров. Верхний горизонтальный канал содержит логические элементы устройства управления Control.

Каждый пиксель содержит блок логики (северо-западный угол), все схемы аналоговой части пикселя и площадку подключения VCSEL. Пиксель представляет собой квадрат размером 750 × 750 мкм. Внутри пикселя расположена зона для логических элементов управления пикселем. Размер отведённой области 306 × 87 мкм. Вся остальная площадь предназначена для аналоговых схем пикселя. Общий вид пикселя приведён на рисунке 28.

Расположение портов пикселя по сторонам:

- сверху и справа – сигналы из/в аналоговый мир;

- слева – сигналы, трассируемые в вертикальном канале, – это общие сигналы пикселей, выбор столбца, сброс, тактирование, а также «земля» и питание;

- снизу – сигналы, трассируемые в горизонтальном канале, – это шина данных и выбор строки.

Кольцо периферийных ячеек содержит ячейки ввода/вывода всех сигналов и ячейки для подачи «земли», питания и опоры. В горизонтальных сегментах кольца ячейки расположены в один ряд, в вертикальных – в два ряда. Функциональная схема включения кристалла 3D М ФЭ СБИС А/Ц представлена на рисунке 29.

С целью уменьшения влияния цифровых помех на работу аналоговых схем кристалла необходимо обеспечить питание аналогового (3,3 и 1,8 В) и цифрового (3,3 и 1,8 В) доменов от отдельных вторичных источников и ввести для каждого домена с каждой стороны кристалла фильтрующие конденсаторы 10 мкФ + 100 нФ (керамический с малым ESR) максимально ближе к местам подключения выводов.

Технические характеристики 3D М ФЭ СБИС А/Ц

Как и матрица излучателей, кристалл 3D М ФЭ СБИС А/Ц содержит матрицу из 64 (8 × 8) интеллектуальных пикселей:

- формат матрицы – 8 × 8;

- количество оптических каналов ввода/вывода 64/64;

- электрический интерфейс – 64 бит;

- скорость электрического ввода/вывода – до 166 МГц;

- скорость оптического многоканального ввода/вывода – до 166 МГц;

- вид многоканальных связей – фотон-фотонный (транзит), фотон-электронный, электронно-фотонный;

- модуляция – импульсно-кодовая с непосредственной демодуляцией мощности оптического излучения;

- управление – слайсовое, с последовательной выборкой цифровых данных матрицы.

Каждый интеллектуальный пиксель включает: приёмный ИК-фотодиод, усилитель-преобразователь фототока в напряжение, 8-разрядный АЦП выходного напряжения усилителя-преобразователя, 8-разрядный ЦАП с токовым выходом на излучающие лазеры, 8-разрядный регистр данных с интерфейсом ввода/вывода, контактные площадки токового выхода и общего катода для монтажа лазерного излучателя.

Электрический интерфейс обеспечивает обмен цифровыми данными с управляющим процессором TMS320C6455 фирмы Texas Instruments по интерфейсу External Memory Interface (EMIFA).

Данная конфигурация обеспечивает параллельный обмен сигналами между базовыми модулями 3D М ФЭФ СБИС.

Особенности функциональных пикселей 3D М ФЭ СБИС А/Ц

Каждый пиксель кристалла 3D М ФЭ СБИС А/Ц включает в себя приёмный фотодиод, преобразователь ток–напряжение, функциональную схему, площадку для монтажа анода внешнего лазера вертикального излучения, основные функции пикселей, приём оптической информации в цифровом или аналоговом режимах и преобразование её в токовый сигнал, функциональную обработку, формирование нормированного тока лазера для передачи оптической информации в цифровом или аналоговом режимах.

На рисунке 30 представлена фотография кремниевого кристалла 3D М ФЭ СБИС А/Ц, выполненного по кремниевой КМОП-технологии.

Режимы эксплуатации 3D М ФЭ СБИС А/Ц

Режимы эксплуатации (ток потребления и мощность) всего кристалла 3D М ФЭ СБИС А/Ц представлены при нормальных условиях (Т = +40°С, Vcc = 3,3 В, Vdd = 1,8 В):

- ток потребления аналоговый: Iccа = 64 × 4 мА = 256 мА (типичное);

- ток потребления аналоговый: Iddа = 64 × 8 мА = 512 мА (типичное);

- ток потребления по опорным источникам: Iref = 64 × 0,5 мА = 32 мА (типичное);

- ток потребления логики (при Fclk= = 166 МГц): Iddd = 64 × 2 мА = 128 мА (типичное);

- ток потребления выходов (при Fclk = =166 МГц): Iddo = 64 × 2 мА = 128 мА (типичное).

Суммарная мощность потребления от всех источников составляет Р = 3,3 × (256 + 128) + 1,8 × (512 + 128) +0,256 × 32 = 1267 + 1152 + 8 = 2430 мВт.

Прогнозируемая максимальная мощность потребления всего кристалла WP-модели (Т = +85°С, Vcc = 3,4 В, Vdd = =1,9 В) может достигать 3,5 Вт, что ограничивает максимальную рабочую температуру среды на уровне +85°С и требует специальных мер для охлаждения кристалла, чтобы максимальная температура поверхности кристалла составляла не более +125°С.

Системный подход применения 3D М ФЭ СБИС А/Ц

Для оценки возможностей межкристаллического обмена информации кристаллов 3D М ФЭ СБИС А/Ц рассчитаем информационный поток при использовании аналоговых и цифровых интерфейсов.

При использовании электрической шины EMIFA для приёма, обработки и передачи 64-разрядных битовых слов по 64-разрядной шине EMIFA кристалла 3D М ФЭ СБИС А/Ц с тактовой частотой 150 МГц получим общий поток информации 150 МГц × 64 бит » » 9,6 Гбит/с. При этом для связи с другими 3D М СБИС используется электрический многоканальный интерфейс EMIFA.

При использовании 64-канального оптического цифрового интерфейса с побитовым выводом информации с 64 пикселей с тактовой частотой 150 МГц имеем информационный поток на кристалле 3D М ФЭ СБИС А/Ц, равный 150 МГц × 64 бит ≈ 9,6 Гбит/с.

При использовании 64-канального оптического аналогового интерфейса имеем на каждом пикселе 8(16)-разрядный АЦП/ЦАП с тактовой частотой 150 МГц информационный поток 150 МГц × 8 = 1,2 Гбит/с. При одномоментной передаче массива из 64 пикселей имеем общий информационный поток 1,2 Гбит/с × 64 канала = = 76,8 Гбит/с. При 16-разрядном АЦП/ЦАП на каждом пикселе информационный поток будет равен 2,4 Гбит/с, а общий – 153,6 Гбит/с.

Таким образом, применение фотонных интерфейсов с аналого-цифровой и цифроаналоговой импульсно-кодовой модуляцией имеет перспективное развитие для межкристаллического обмена данными.

В следующей статье будет представлено техническое описание с конструктивными решениями и электрическими характеристиками остальных 3D М СБИС базового ряда, таких как: матрица процессоров с потоковой обработкой функции расщепленного алгоритма БПФ (3D М ФЭ СБИС ПФ), матрица пикселей памяти с функцией перестановки (3D М ФЭ СБИС ПП), кристалл коммутации каналов (3D М ФЭ СБИС КК) и кристалл маршрутизатора SPACE WIRE (3D М ФЭ СБИС SW).

Если вам понравился материал, кликните значок - вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал - не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!