Требования, задачи, пути решения

В настоящее время наблюдается неуклонный рост потребности в высокопроизводительных малогабаритных цифровых вычислительных комплексах (ЦВК), способных обеспечить обработку данных от большого числа источников информации в «жёстком» реальном времени. В первую очередь это относится к многоканальным системам обработки гидролокационной и радиолокационной информации, видеосигналов, к ультразвуковым и рентгеновским сканерам и др. Для создания таких комплексов в нашей стране используются многопроцессорные вычислительные системы или многомашинные вычислительные комплексы, построенные на основе одноплатных высокопроизводительных многопроцессорных ЭВМ (например «Эльбрус-90микро» или «Багет»).

Многомашинные вычислительные комплексы имеют ряд неоспоримых преимуществ:

-

относительная простота реализации;

-

возможность практически неограниченного увеличения производительности путём подключения дополнительных ЭВМ;

-

относительная простота организации резервирования.

Однако достаточно эффективно эти комплексы функционируют только при реализации относительно малосвязанных задач, требующих процессоров универсального типа. При решении задач многоканальной сигнальной обработки и схожих с ними по организации вычислительного процесса, в которых задействуется большое число процессоров с интенсивным межпроцессорным информационным обменом, использование многомашинных вычислительных комплексов нецелесообразно: как показано в [1], их реальная производительность составляет здесь лишь 5-10% от потенциально возможной.

Для обеспечения высокой производительности систем массового параллелизма, как правило, используются многопроцессорные векторно-конвейерные и массово-параллельные системы, включая системы кластерного типа [2]. Отдельным подклассом таких систем являются вычислительные системы, предназначенные для работы в «жёстком» реальном времени.

Организация вычислений в режиме «жёсткого» реального времени влечёт целый ряд специфических особенностей. В первую очередь это касается вопросов, от которых непосредственно зависит эффективность многопроцессорного вычислительного комплекса, — вопросов выбора способа построения систем межпроцессорного и внешнего обмена [1].

При построении системы межпроцессорного обмена должны быть обеспечены:

-

равнодоступность и полносвязность процессоров;

-

возможность простого и эффективного распараллеливания задач между процессорами;

-

детерминированность задержек передачи данных;

-

синхронизация параллельных процессов;

-

выполнение групповых (синхронных) команд и многоадресной рассылки данных;

-

исключение конфликтов и независимость работы процессоров от коммуникационной среды;

-

возможность наращивания производительности;

-

возможность реконфигурации в зависимости от характера решаемых задач.

Использование современных универсальных интерфейсов типа HyperTransport, RapidIO, PCI Express, Fibre Channel не в полной мере позволяет удовлетворить перечисленным требованиям, поэтому построение коммуникационных систем «жёсткого» реального времени, как правило, является специализированной задачей, обеспечивающей заданную эффективность межпроцессорного обмена в зависимости от решаемого класса задач, числа процессоров, выбранной архитектуры построения ЦВК и способа построения системы внешнего информационного обмена.

К основным требованиям, которые предъявляются к системам внешнего информационного взаимодействия, функционирующим в режиме «жёсткого» реального времени, следует отнести:

-

обеспечение высокой скорости, помехоустойчивости и надёжности информационного обмена;

-

обеспечение детерминизма времени доставки данных и передачи сигналов синхронизации и управления для большого числа источников информации;

-

объединение в единый поток данных и команд управления для различных источников информации;

-

наличие эффективных систем распределённого контроля, диагностики и резервирования.

Наиболее перспективным решением задач, связанных с выполнением перечисленных требований, является применение Ethernet-технологий. Одновременно использование сетевых технологий позволяет решить такие задачи, как

-

возможность подключения к ЦВК разнообразного стандартного оборудования;

-

значительное сокращение числа используемых каналов и количества используемых типов интерфейсов;

-

простота реализации резервирования на основе использования стандартного коммутационного оборудования;

-

полная гальваническая развязка взаимодействующих систем.

В качестве примера рассмотрим многопроцессорный вычислительный комплекс (МПВК), разработанный ЗАО НПП «Авиационная и Морская Электроника» для корабельных систем обработки информации.

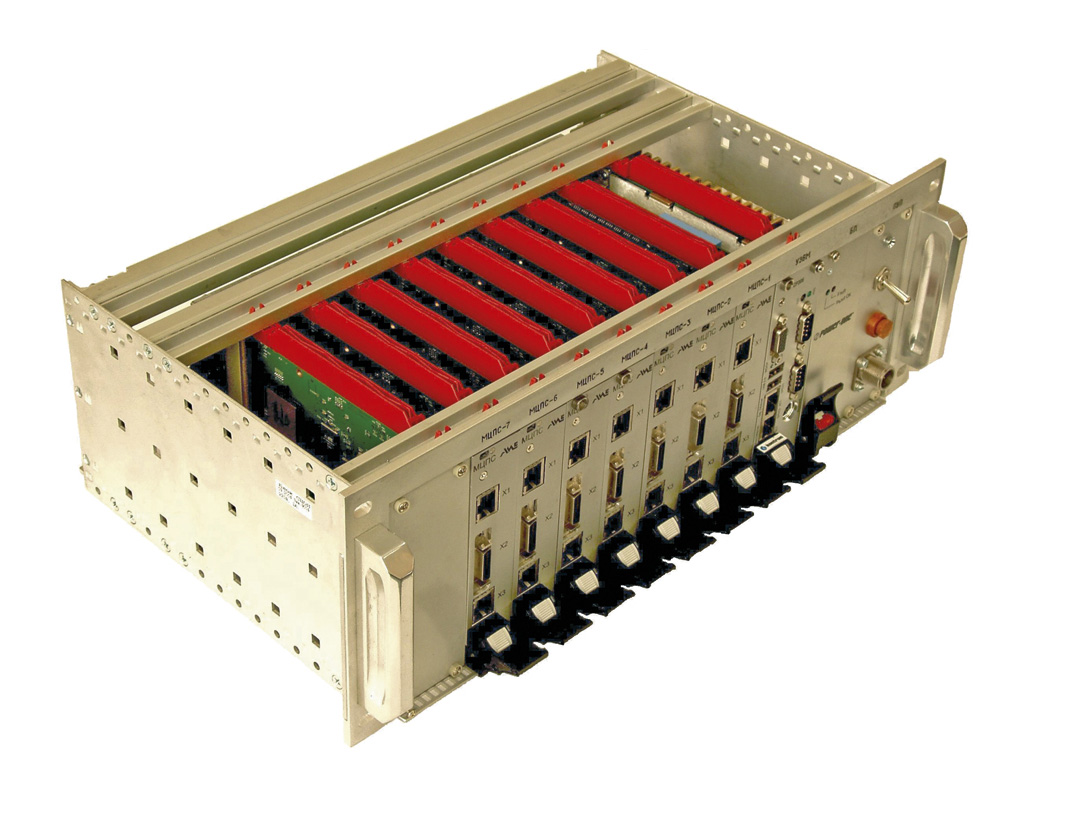

МПВК является многопроцессорной суперЭВМ, обладающей производительностью более 25 GFLOPS и предназначенной для многоканальной цифровой обработки больших потоков информации в «жёстком» реальном масштабе времени. МПВК может быть использован как в качестве автономной вычислительной системы, так и для построения кластерных суперЭВМ с широким диапазоном производительности.

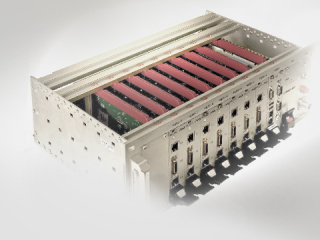

Внешний вид вычислительного блока МПВК показан на рис. 1.

Состав, особенности конструкции и параметры надёжности МПВК

В состав разработанного вычислительного комплекса входят:

-

до 7-8 модулей цифровых процессоров сигналов (МЦПС);

-

модуль центрального процессора (МЦП) на базе одноплатного универсального компьютера CPС-502;

-

объединительная кросс-плата межмодульных соединений (КПМС-1);

-

модуль блока питания (МБП).

Каждый МЦПС представляет собой двухпроцессорную систему. Один процессор установлен на основной плате, а второй — на дополнительном мезонинном модуле (ДЦПС). Для реализации в МПВК возможности непосредственного ввода композитного сигнала или радиолокационного видеосигнала с соответствующими сигналами синхронизации и их цифровой обработки в модули МЦПС вместо ДЦПС можно устанавливать модули ввода специальных сигналов, в том числе с высокоскоростными и многоканальными АЦП, модули цифрового ввода-вывода и др.

В основу архитектуры МПВК заложен принцип мультимодульности, что позволяет в зависимости от требований по производительности использовать от 1 до 8 (если не используется МЦП, в противном случае — до 7) вычислительных модулей МЦПС. В случае если МПВК не требует использования МЦП, вместо него устанавливается дополнительный МЦПС.

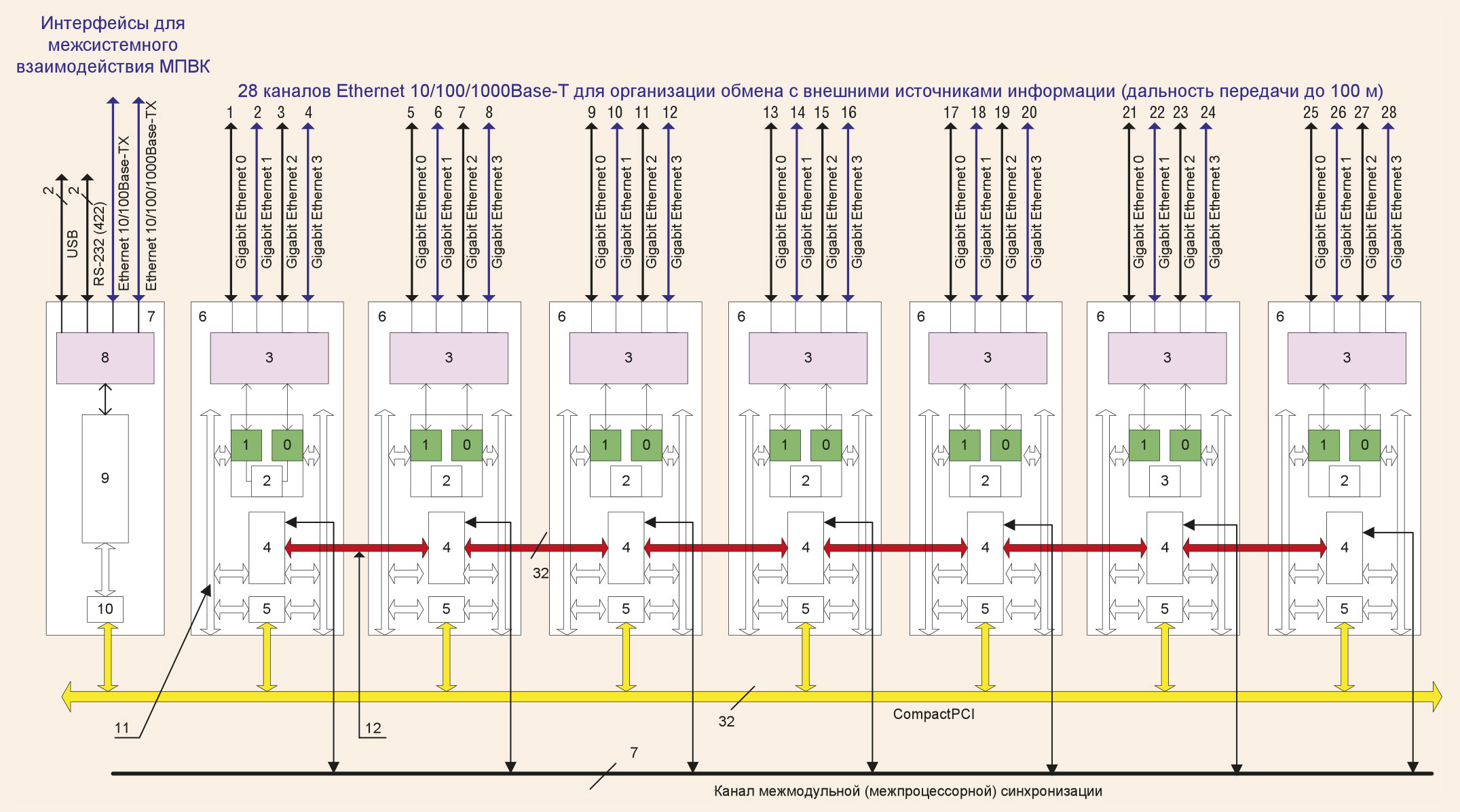

Для организации внешнего взаимодействия в МПВК применяются следующие интерфейсы:

-

Ethernet 10/100/1000Base-T — до 28 плюс 2 канала модуля МЦП (Ethernet 10/100Base-T и 10/100/1000Base-T) для межсистемного взаимодействия или 4 канала восьмого модуля МЦПС (Ethernet 10/100/1000Base-T);

-

RS-232, RS-422 (МЦП) — 2;

-

USB 2.0 (МЦП) — 2.

Для организации внутрисистемного взаимодействия используются следующие интерфейсы:

-

стандартный — системная шина CompactPCI (PICMG 2.0 D3.0) с пропускной способностью до 133 Мбайт/с;

-

специализированные (собственной разработки):

-

магистраль транспортировки данных (МТД) с пропускной способностью от 400 до 1200 Мбайт/с,

-

канал межпроцессорного обмена (в каждом МЦПС) с пропускной способностью до 400 Мбайт/с,

-

канал глобальной синхронизации работы модулей МЦПС (7 линий, в случае установки 8 модулей МЦПС — 8 линий) для организации синхронизации многопроцессорных вычислений.

Конструктивное исполнение:

-

блок стандарта Евромеханика (корпус EuropacPRO фирмы Schroff с защитой от ЭМИ [3]) высотой 3U с габаритными размерами 435×253×149,5 мм;

-

модули типоразмера 3U стандарта Евромеханика с габаритными размерами 178×100×11 мм;

-

внешнее охлаждение не требуется;

-

вес не более 8 кг.

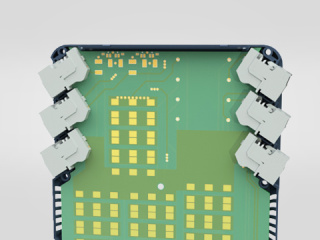

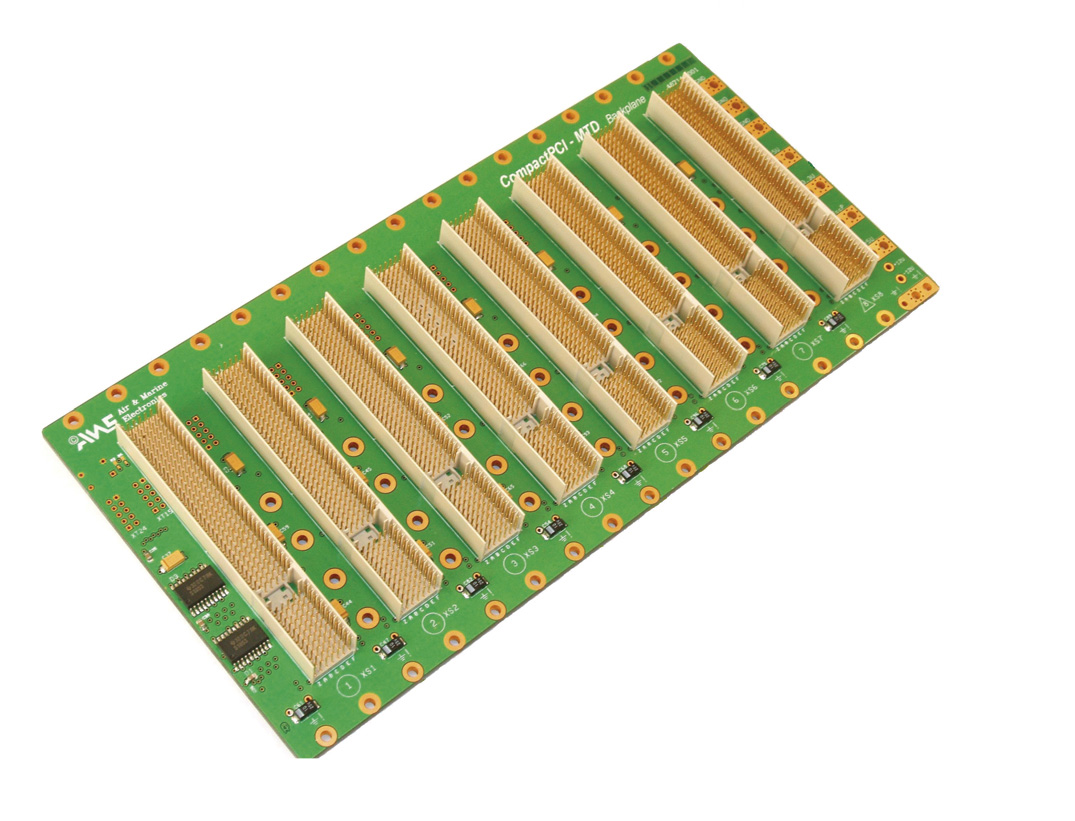

Кросс-плата КПМС-1 (рис. 2) установлена на задней стенке корпуса и обеспечивает электрическую коммутацию модулей МПВК и их механическое крепление.

На кросс-плате реализованы следующие интерфейсы:

-

системная шина CompactPCI (PICMG 2.0 D3.0), занимающая нижнюю часть разъёмов, — Р1;

-

магистраль транспортировки данных, занимающая верхнюю часть разъёмов, — Р2.

Параметры электропитания:

-

220 В (50 Гц) или 19-36 В;

-

потребляемая мощность до 80 Вт.

Комплекс МПВК характеризуется следующими показателями надёжности:

-

среднее время наработки на отказ — 5000 часов;

-

ресурс до заводского ремонта — 40000 часов;

-

назначенный срок службы — 15 лет;

-

назначенный срок сохраняемости — 10 лет;

-

срок действия гарантийных обязательств — 3 года.

МПВК имеет группу исполнения 2.1.2. по ГОСТ РВ 20.39-304-98 и ГОСТ РВ 20.39.305-98. Он полностью отвечает требованиям, предъявляемым к корабельной аппаратуре, в частности, выдерживает одиночный механический удар с пиковым ускорением 5g, имеет защиту от соляного тумана и т.п.

Процессорные модули МЦПС и МЦП

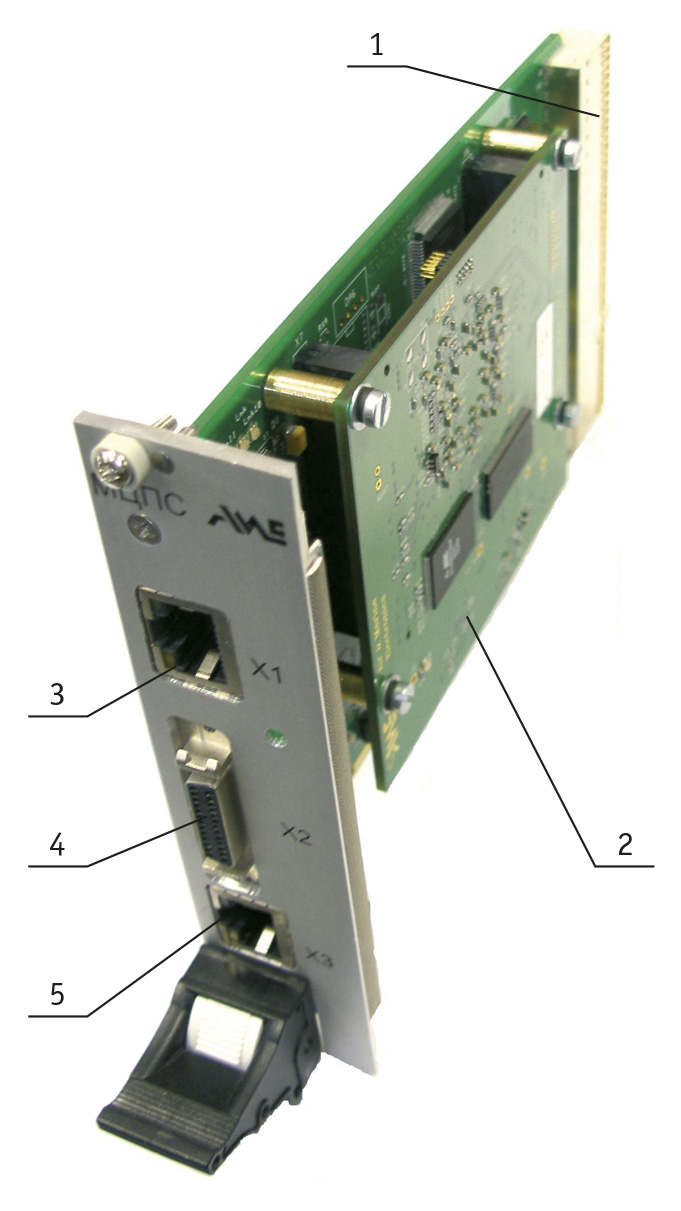

Специализированный модуль МЦПС (рис. 3) представляет собой двухпроцессорную систему, построенную на базе сигнального процессора TMS320C6713.

Условные обозначения:

1 — стандартный соединитель CompactPCI 3U для подключения МЦПС к плате КПМС-1;

2 — съёмный модуль ДЦПС;

3, 4, 5 — соединители Ethernet (Х1, Х2, Х3).

Второй процессор установлен на мезонинном модуле. Общая производительность модуля составляет до 3600 МFLOPS.

Модуль МЦПС имеет стандартные размеры 3U, занимает в каркасе одну позицию (6HP) по ширине.

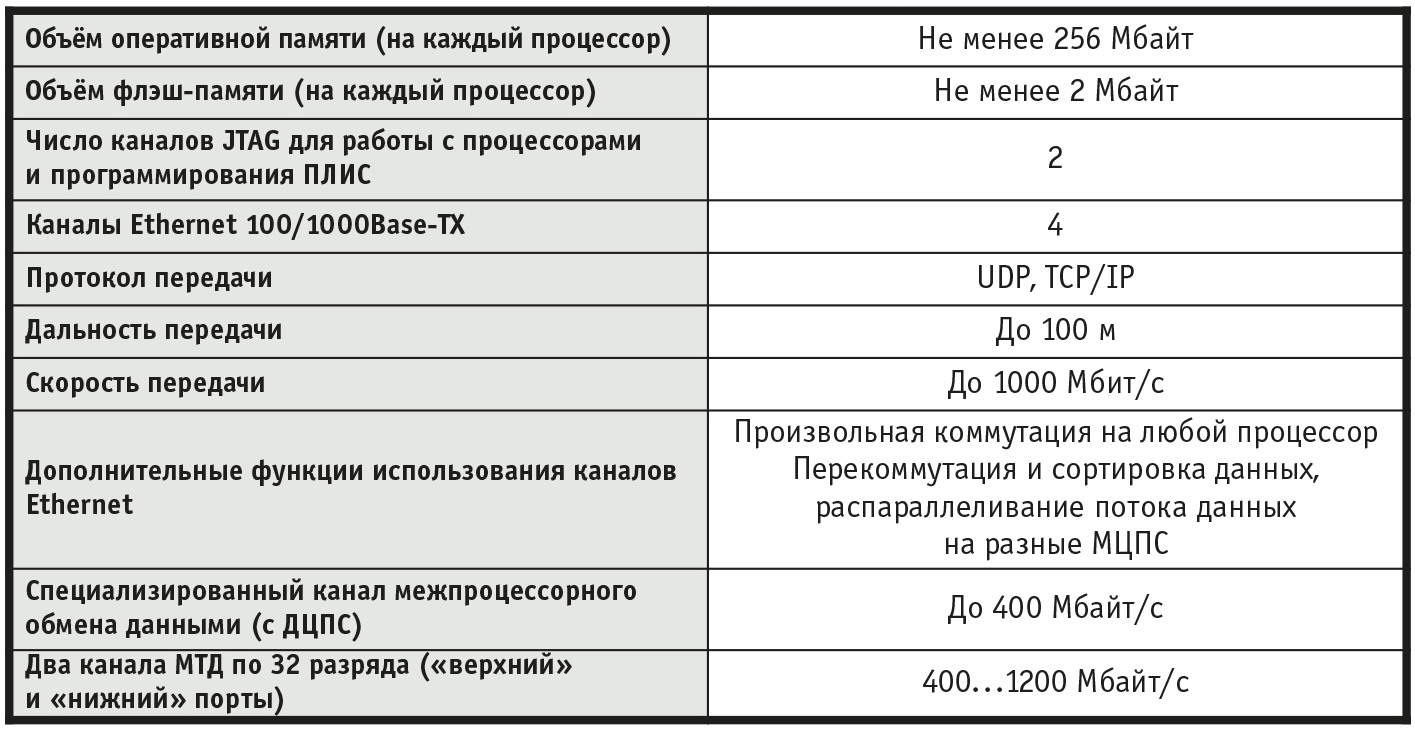

Основные характеристики МЦПС представлены в табл. 1.

В настоящий момент готовится к производству версия МЦПС на базе отечественного микропроцессора 1892ВМ5 производства ГУП НПЦ «Элвис».

Модуль МЦП представляет собой отечественный универсальный одноплатный компьютер CРC502, выпускаемый ЗАО НПФ «Доломант» по документации и под авторским надзором фирмы «Фаствел». Модуль выполнен в формате CompactPCI 3U. В зависимости от решаемых задач в составе МПВК он может выполнять следующие функции:

-

начальная загрузка программы во все процессоры МЦПС;

-

управление вычислительным процессом;

-

приём и обработка итоговых данных от МЦПС;

-

отображение информации;

-

обмен данными с другими вычислителями и т.п.

Одним из наиболее важных преимуществ СРС502 является то, что данный одноплатный компьютер является полностью отечественной разработкой, поставляется с полным комплектом документации и с приёмкой заказчика. Опыт применения СРС502 во многих изделиях, выпускаемых ЗАО НПП «Авиационная и Морская Электроника», показал его высокую надёжность, эффективность в использовании и высокий уровень поддержки со стороны производителя.

Внешний вид модуля МЦП показан на рис. 4.

Более подробную информацию о технических характеристиках СРС502 и других аналогичных по назначению изделий, выпускаемых НПФ «Доломант», можно получить на официальном сайте фирмы www.dolomant.ru.

Общие данные о системной архитектуре МПВК

Архитектура МПВК разработана на основании рассмотренных ранее принципов построения многопроцессорных вычислительных систем «жёсткого» реального времени.

Многоуровневая система организации информационного обмена МПВК, построенная по иерархическому принципу, обеспечивает выполнение требований, предъявляемых к организации внутрисистемного и внешнего информационного обмена.

Уровень внутрисистемного взаимодействия представлен:

-

системным уровнем, который обеспечивает организацию информационного взаимодействия МЦПС с управляющей ЭВМ (модуль МЦП) по стандартному магистрально-шинному интерфейсу CompactPCI;

-

уровнем информационного взаимодействия МЦПС, который обеспечивает высокоскоростной обмен данными между модулями МЦПС по специализированному интерфейсу МТД;

-

уровнем межпроцессорного взаимодействия, который обеспечивает обмен данными между основным и мезонинным процессорами в модуле МЦПС (обмен организован по методу «почтового ящика»).

Структурно-функциональная схема вычислительного блока МПВК приведена на рис. 5.

Условные обозначения:

0 — основной процессор МЦПС; 1 — мезонинный процессор МЦПС (ДЦПС); 2 — контроллер межпроцессорного обмена МЦПС; 3 — контроллер внешних интерфейсов МЦПС; 4 — контроллер МТД МЦПС; 5 — контроллер CompactPCI МЦПС; 6 — модуль МЦПС; 7 — модуль МЦП; 8 — контроллер внешних интерфейсов МЦП; 9 — процессорный блок МЦП; 10 — контроллер CompactPCI МЦП; 11 — шина EMIF процессора; 12 — шина МТД.

Организация информационного обмена по МТД

Для обеспечения требуемой эффективности работы многопроцессорной системы в режиме «жёсткого» реального времени сотрудниками ЗАО НПП «Авиационная и Морская Электроника» была разработана магистраль МТД, отличающаяся высокой скоростью передачи данных, присущей системам, построенным на основе Link-каналов, которая обеспечивает равнодоступность и полносвязность процессоров, а также гибкость в управлении информационным обменом, свойственную системам с архитектурой гиперкуб. Реализация синхронного протокола передачи данных позволила исключить возникновение конфликтных ситуаций и обеспечить детерминированность времени доставки данных. С помощью канала глобальной синхронизации обеспечивается синхронизация параллельных процессов.

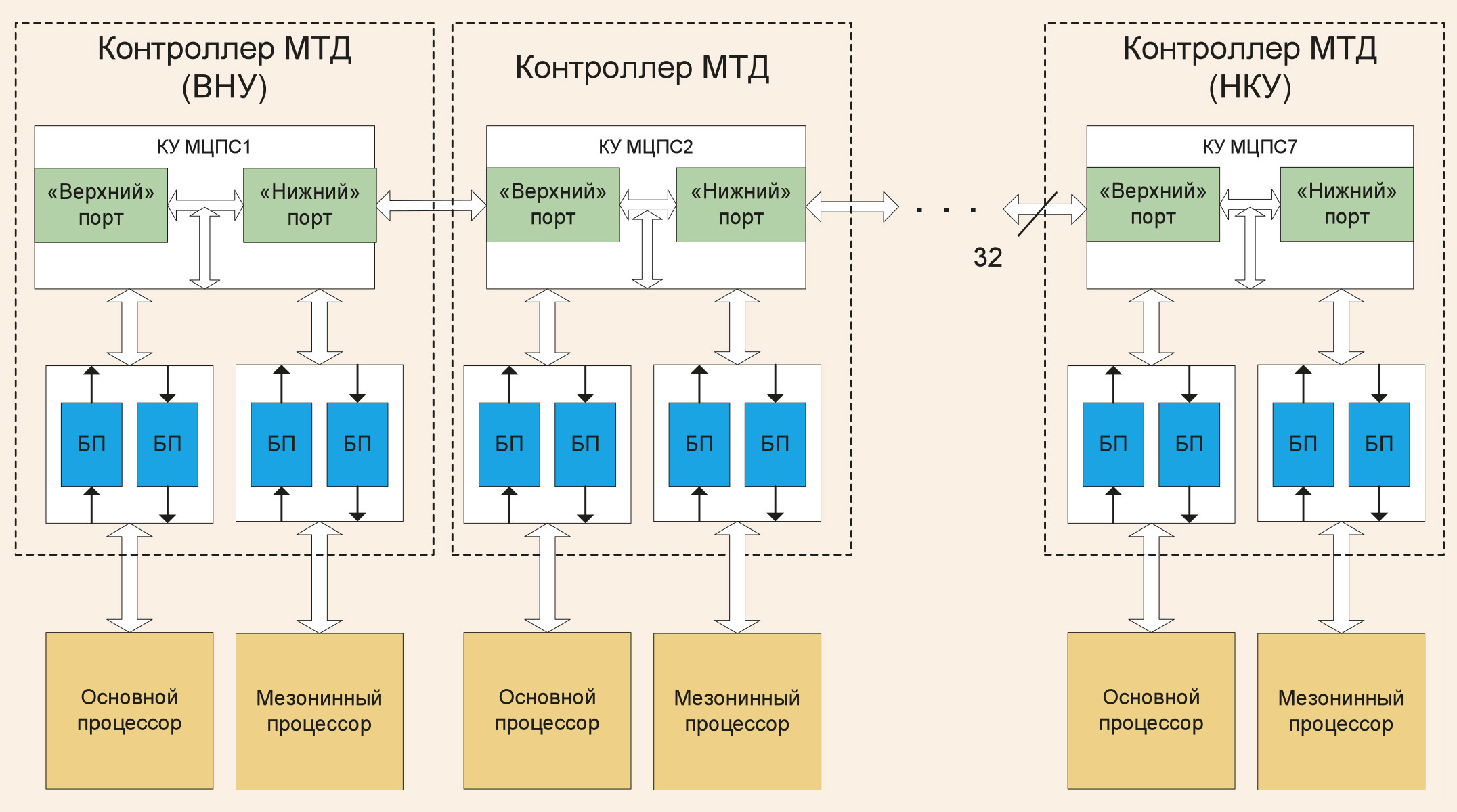

Структурно-функциональная схема МТД приведена на рис. 6.

Условные обозначения:

КУ — коммутационный узел; ВНУ — «верхний» начальный узел; НКУ — «нижний» конечный узел; БП — буферная память.

Каждый МЦПС содержит коммутационный узел, в состав которого входят два независимых двунаправленных

32-разрядных канала, представленных «нижним» портом (НП) и «верхним» портом (ВП). МТД организована так, что все коммутационные узлы МЦПС последовательно соединены друг с другом, причём НП предыдущего узла МЦПС соединён с ВП последующего узла. Первый МЦПС в данном случае содержит верхний начальный узел (ВНУ) МТД, а последний — нижний конечный узел (НКУ) МТД. Определение количества МЦПС и их нумерация осуществляются при начальном включении МПВК. Теоретически количество узлов в МТД может быть произвольным и определяться только требованиями к производительности многопроцессорной вычислительной системы.

Для обеспечения возможности исключения процессоров в ходе информационного обмена передача данных по МТД основана на использовании механизма буферизации. Каждый процессор помещает в буферную память данные с адресом получателя, которые необходимо передать, и считывает поступившие для него данные из другой буферной памяти контроллера МТД. Запись и чтение данных осуществляются с помощью каналов EDMA в режиме Burst Mode со скоростью 400 Мбайт/с. Для организации взаимодействия процессора с контроллером МТД используется механизм прерываний или механизм работы с флагом.

Передача данных по МТД осуществляется пакетами. Пакет состоит из заголовка и блока данных. Заголовок пакета содержит адрес источника, адрес приёмника информации (адреса приёмников при групповой рассылке) и размер передаваемого блока данных. Блок данных должен состоять не менее чем из восьми 32-разрядных слов, но не превышать размер в 1024 (2048) 32-разрядных слова.

Информационный обмен в МТД организован методом циклической передачи прав на передачу данных каждому МЦПС (метод циклического опроса заявок на передачу). Каждый узел МТД имеет возможность передачи данных одному или нескольким (групповая рассылка) МЦПС.

Данные по МТД передаются в оба направления через «верхний» и «нижний» порты. Передача данных может производиться с подтверждением готовности контроллеров МТД к приёму информации или без подтверждения. Считается, что узел не готов к приёму информации, если в данный момент времени занята его приёмная буферная память. В случае получения сигнала неготовности узла к приёму передача пакета прекращается. Права на передачу переходят к следующему узлу, а попытка повторной передачи данного пакета будет осуществлена в следующем цикле. Каждый узел обеспечивает синхронизацию передачи данных до очередного узла.

После окончания передачи данных или при их отсутствии передающий узел МТД уступает права на передачу следующему узлу. Последний узел МТД по окончании передачи данных передаёт права на передачу в начало МТД (первому узлу).

Узлы МТД, не осуществляющие передачу, обеспечивают трансляцию принятых данных следующему узлу. За счёт реализации механизма передачи прав каждый узел МТД знает, где относительно него находится активный узел, и поэтому может однозначно определить направление трансляции данных. При ретрансляции осуществляется регенерация передаваемых сигналов, что обеспечивает возможность высокоскоростной передачи данных без ограничения дальности.

Для обеспечения слаженной работы процессоров по каналу глобальной синхронизации МТД передаются сигналы синхронизации и управления. Для организации синхронизации и управления используется один из процессоров (задаётся программным способом), который является ведущим, а все остальные процессоры — ведомыми.

В зависимости от характера решаемых задач предусмотрена возможность логического разделения МТД на отдельные участки, способные осуществлять независимую передачу данных в своём сегменте, что существенно повышает (до 1200 Мбайт/с) пропускную способность МТД. Сегментирование МТД обеспечивается за счёт создания нескольких «верхних» и «нижних» портов, ограничивающих область сегмента. Реконфигурация МТД может осуществляться многократно без нарушения работоспособности системы.

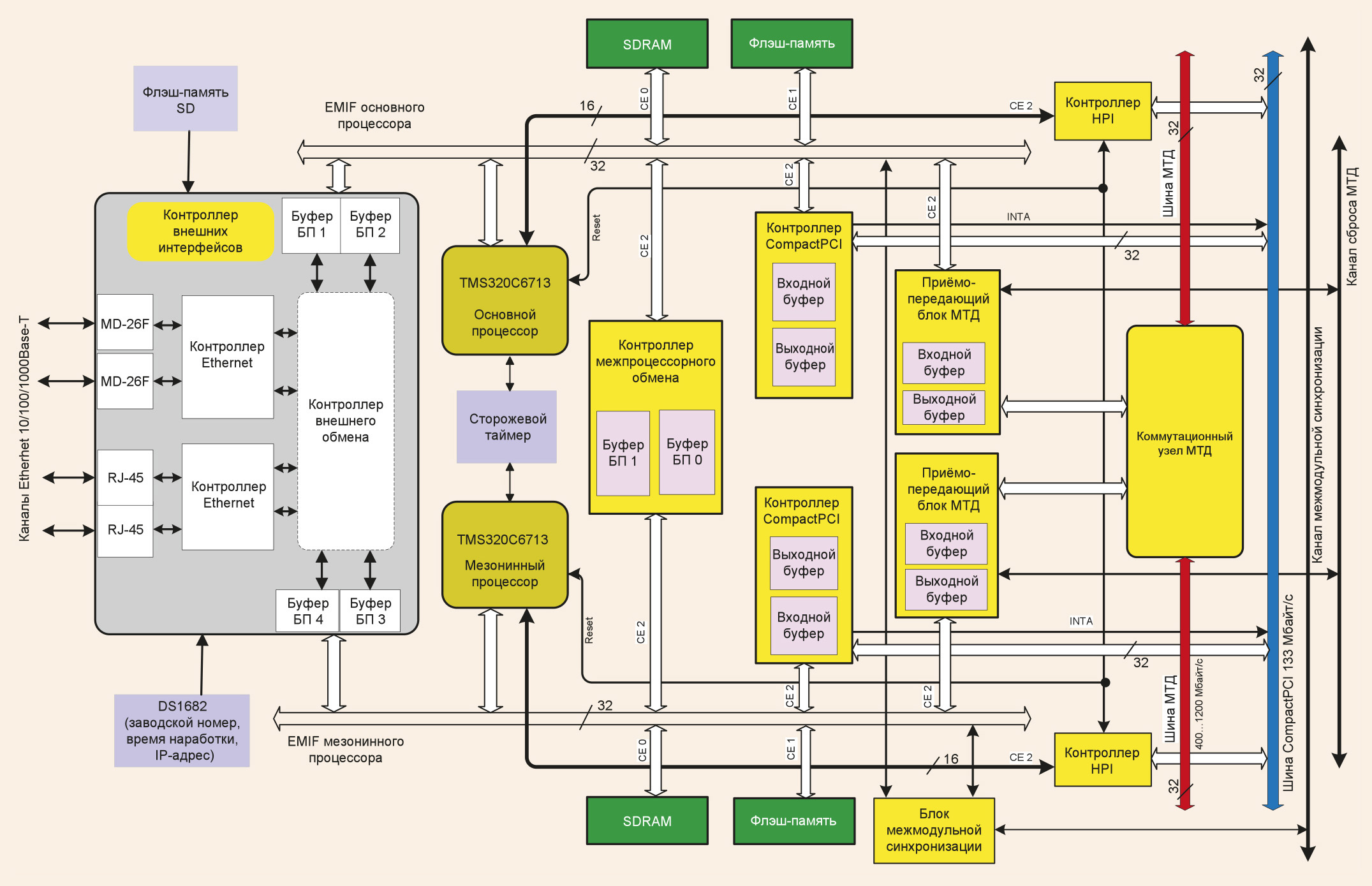

Системная архитектура модуля МЦПС

Функциональная схема модуля МЦПС приведена на рис. 7.

Условные обозначения:

CE 0…2 — области адресного пространства; INTA — прерывание.

Начальная установка и загрузка программы в основной и мезонинный процессоры TMS320C6713 осуществляется от управляющей ЭВМ (МЦП) по каналам CompactPCI через HPI с помощью контроллеров HPI. Возможность доступа МЦП к внутренним ресурсам процессоров (регистры, память) также реализуется по интерфейсу HPI.

Оперативная память SDRAM и флэш-память подключены к процессорам по интерфейсу EMIF в адресном пространстве CE 2.

Для организации межпроцессорного обмена используется соответствующий контроллер, который подключён к каналам EMIF каждого процессора. В состав контроллера межпроцессорного обмена входят два независимых буфера обмена БП 0 (буферная память основного процессора) и БП 1 (буферная память мезонинного процессора) объёмом по 1 кбайт и общедоступные регистры управления. Скорость чтения/записи в буферы обмена — до 400 Мбайт/с. Для управления обменом данными предусмотрены процессорные прерывания или механизм работы с флагом.

Для организации информационного обмена по каналам CompactPCI используются контроллеры CompactPCI, реализующие системный интерфейс CompactPCI (стандарт PICMG 2.0 D3.0). Во входной буфер осуществляется запись данных для процессора, принятых по шине CompactPCI, а в выходной буфер — данных от процессора для передачи по шине CompactPCI. Взаимодействие буферов с процессором осуществляется по каналам EMIF. Объём каждого буфера составляет 1 кбайт, вместе они образуют буферную память контроллера CompactPCI. Скорость чтения/записи в буферную память по шине EMIF составляет до 400 Мбайт/с. Обмен данными с МЦП каждый МЦПС может осуществлять в режимах «Target» или «Master». В контроллере реализована возможность передачи прерываний со стороны процессоров на управляющую ЭВМ (МЦП) или приёма сигналов сброса процессоров со стороны МЦП.

Обмен данными между МЦПС организован с помощью магистрали МТД. Для управления передачей данных используется контроллер МТД, в состав которого входят коммутационный узел, реализующий интерфейс передачи данных по магистрали, и приёмопередающие блоки для каждого процессора. Каждый такой блок имеет в своём составе выходной буфер объёмом 2 кбайт для приёма данных от процессора и входной буфер объёмом 16 кбайт для приёма данных из МТД для соответствующего процессора. Приёмопередающий блок контроллера МТД обеспечивает:

-

приём данных от процессора;

-

передачу данных в коммутационный узел МТД;

-

приём данных для соответствующего процессора от коммутационного узла МТД;

-

передачу данных в память процессора.

Поступающая по четырём каналам Gigabit Ethernet информация с помощью контроллера внешних интерфейсов преобразуется для передачи и записывается в буферную память соответствующего процессора. Считывание данных из буферной памяти осуществляется процессором по каналам EMIF в режиме Burst Mode. В контроллере предусмотрена возможность произвольной коммутации входных потоков на оба процессора.

В качестве дополнительных функций контроллер реализует возможность ретрансляции данных и их переупаковки.

Использование микросхемы типа DS1682 позволяет сделать программно-доступными данные о наработке модуля, получить информацию о наличии определённого класса событий и идентификационный номер модуля.

Наличие флэш-памяти SD делает возможным оперативное изменение состава программного обеспечения модуля.

Блок межмодульной синхронизации обеспечивает синхронизацию работы модулей и параллельных процессов в системе за счёт передачи управляющим процессором сигналов синхронизации и управления.

Наличие канала сброса МТД позволяет осуществить аппаратный принудительный сброс контроллеров МТД при «зависании» магистрали, а наличие сторожевого таймера — произвести «мягкий» сброс процессора в случае его «зависания».

Все контроллеры внутренней архитектуры модуля МЦПС выполнены по технологии ПЛИС, что позволило реализовать возможность адаптации архитектуры МЦПС к характеру решаемых задач за счёт:

-

изменения пространства памяти контроллеров;

-

изменения протоколов обмена контроллеров с внутренними и внешними устройствами;

-

разработки специализированных интерфейсных устройств.

Использование МПВК в качестве кластера позволяет обеспечить решение задачи повышения в широком диапазоне производительности многопроцессорного вычислительного комплекса.

Пример построения высоко производительных вычислительных комплексов на основе МПВК

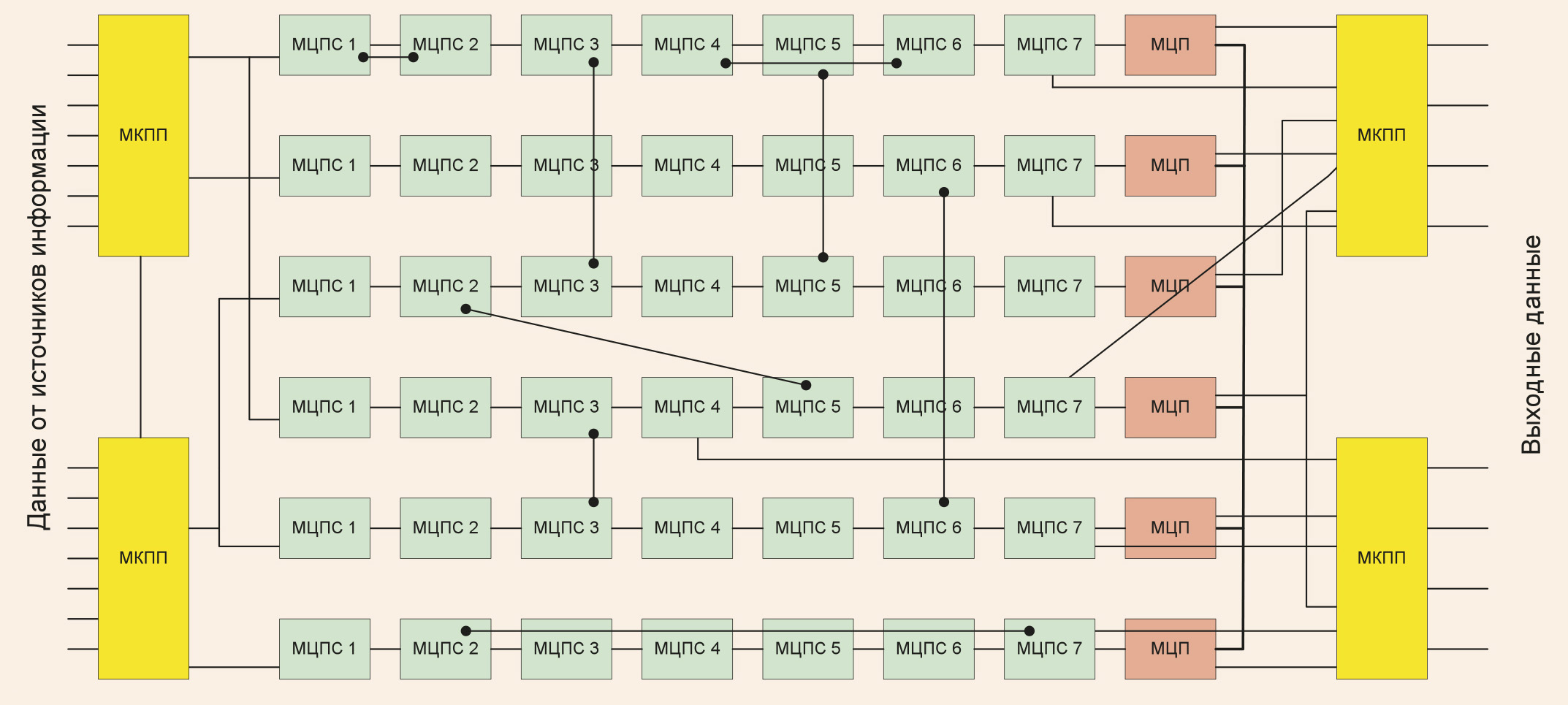

На основе рассматриваемого вычислителя возможно построение кластерной высокопроизводительной вычислительной системы, в которой МПВК используется в качестве вычислительного кластера. Пример организации кластерной вычислительной системы приведён на рис. 8.

Условные обозначения:

МЦПС — модуль цифровых процессоров сигналов; МЦП — модуль центрального процессора; МКПП — модуль коммутации и преобразования пакетов.

С использованием кластерных высокопроизводительных систем обеспечивается решение следующих задач:

-

достижение необходимой производительности вычислительной системы;

-

раздельная реализация различных режимов обработки информации (один режим – один вычислитель);

-

обеспечение высокой надёжности вычислительной системы и оперативности ликвидации последствий сбоев и отказов.

В рассматриваемой системе для организации произвольной коммутации входных и выходных информационных потоков используется специализированный модуль коммутации и преобразования пакетов (МКПП), отличающийся от стандартного коммутатора Gigabit Ethernet наличием «жёсткой» управляемой таблицы коммутации пакетов и возможностью агрегации потоков данных. Наличие данного коммутатора является необходимым условием для обеспечения детерминированности передачи данных. Вопросы организации информационного обмена, синхронизации и управления внешними устройствами более подробно рассмотрены в [4].

Внутрисистемное взаимодействие вычислительных модулей организуется посредством специализированной межкластерной магистрали транспортировки данных или произвольно с помощью каналов Gigabit Ethernet.

Отличительной особенностью рассматриваемой архитектуры является возможность произвольной коммутации входных потоков данных и использования вычислительных модулей МЦПС в едином вычислительном пространстве. Произвольная коммутация информационных потоков обеспечивается за счёт использования внутренних коммутаторов модуля МЦПС (4 канала Gigabit Ethernet), причём в самом модуле предусмотрена возможность обработки, ретрансляции и коммутации данных.

Объединение универсальных вычислительных модулей МЦП в единую сеть Gigabit Ethernet позволяет организовать информационное взаимодействие на уровне вторичной обработки информации.

Применение МКПП для коммутации выходных потоков обеспечивает возможность подключения к высокопроизводительному вычислительному комплексу различных потребителей информации, причём использование МЦП в качестве индикаторной ЭВМ позволяет перейти к сетевой концепции построения автоматизированных рабочих мест (АРМ). В данном случае предполагается, что индикаторные ЭВМ находятся в отдельном помещении, а передача информации на отображение и управление мониторами осуществляются по Ethernet. Это позволяет обеспечить возможность отображения на мониторе индикаторных процессов любого АРМ. Преимуществами такой концепции являются унификация рабочих мест и повышение надёжности.

Заключение

На основании приведённых материалов можно сделать следующие основные выводы:

-

построение высокопроизводительных вычислительных комплексов целесообразно на базе многопроцессорных вычислительных систем с открытой архитектурой;

-

для обеспечения высокой эффективности многопроцессорного вычислительного комплекса целесообразно разрабатывать собственную систему организации межпроцессорного взаимодействия;

-

наиболее рациональным является построение системы внешнего информационного обмена на основе использования Ethernet-технологий.

Рассмотренные в статье решения по построению многопроцессорных вычислительных комплексов были заложены в основу более чем десяти ОКР для систем судового оборудования. Опыт внедрения данных систем показал их высокую эффективность, надёжность в эксплуатации и высокую адаптируемость для решения достаточно широкого класса задач. ●

Литература

-

Митрофанов В., Слуцкин А., Ларионов К., Эйсымонт Л. Направления развития отечественных высокопроизводительных систем // Открытые системы. 2003. № 5.

-

Бурцев В.С. Выбор новой системы организации выполнения высокопараллельных вычислительных процессов, примеры возможных архитектурных решений построения суперЭВМ // Параллелизм вычислительных процессов и развитие архитектуры суперЭВМ : сб. тр. — М. : ИВВС РАН, 1997.

-

Беломытцев В. Приборные корпуса Schroff: смена поколений // Современные технологии автоматизации. 2007. № 2.

-

Севбо В., Орлов А., Лошаков А. Многоканальная распределённая система синхронного сбора данных «жёсткого» реального времени, построенная на основе Ethernet-технологий // Современные технологии автоматизации. 2007. № 3.

Авторы — сотрудники ЗАО НПП «Авиационная и Морская Электроника»

Телефон/факс: (812) 347-8901, 38 347-8903, 327-4667

Если вам понравился материал, кликните значок - вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал - не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!