С установкой САПР Delta Design и модуля SimPCB (версия 4.1.1) появилась возможность:

- рассчитывать электрические параметры для треков и дифференциальных пар в редакторе платы;

- выполнять расчёт задержек при выравнивании длин сигналов с учётом материалов печатной платы.

В САПР Delta Design предусмотрены два варианта расчёта электрических параметров.

1. Автоматический расчёт в редакторе платы, в панели свойств при выборе трека или дифф. пары

Этот метод рассмотрен в данной статье.

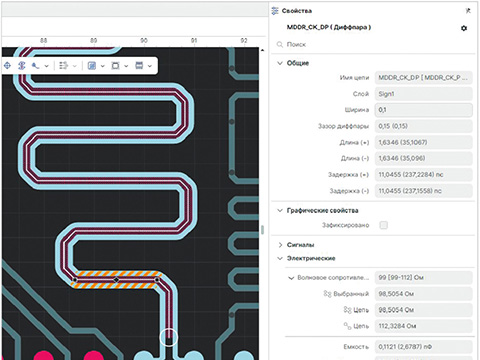

При выборе трека (дифф. пары) в редакторе платы в панели свойств автоматически отображаются и рассчитываются параметры:

- в разделе Общие – задержки (выбранного сегмента и суммы всей цепи);

- в разделе Сигналы – задержки (выбранного сегмента и суммы всей цепи);

- в разделе Электрические – волновое сопротивление, ёмкость, индуктивность.

В этом режиме используются стек, материалы и опорные слои по умолчанию из конфигуратора слоёв вне зависимости от того, на каких слоях проложен трек.

Если опорный слой в стеке не определён, программа автоматически назначает ближайший слой в качестве опорного.

2. Предварительный расчёт в калькуляторе импеданса и создания профиля импеданса

Этот метод будет рассмотрен во второй части статьи.

Расчёт электрических параметров выполняется в конфигураторе слоёв во вкладке калькулятора импеданса. Создаётся профиль импеданса, где задаётся: тип линии передачи, целевой импеданс, параметры материалов, опорные и сигнальные слои.

На основе введённых параметров в профиле импеданса рассчитывается ширина проводника(ов) (для одиночного трека и дифф. пары) и зазор (для дифф. пары). Профиль назначается конкретному треку, дифференциальной паре или классу в редакторе правил.

При трассировке в редакторе платы автоматически применяются:

- расчётная ширина проводника(ов) (для одиночного трека и дифференциальной пары);

- зазор между проводниками (для дифференциальной пары).

Контроль осуществляется через DRC-проверку.

Важно:

- Расчёты первого и второго методов могут различаться из-за разных параметров материалов и опорных слоёв.

- Второй вариант имеет приоритет. Если для трека назначен профиль импеданса, то все расчёты выполняются исходя из его настроек.

При установке Delta Design возможно добавить примеры готовых печатных плат (ПП). Для анализа, приведённого в данной статье, использовался проект FPGA_IGLOO2 DevKit_ver2.0.

На данной плате реализован интерфейс DDR между:

- ПЛИС M2GL010T-1FG484I;

- микросхемой памяти MT46H32M16LFBF.

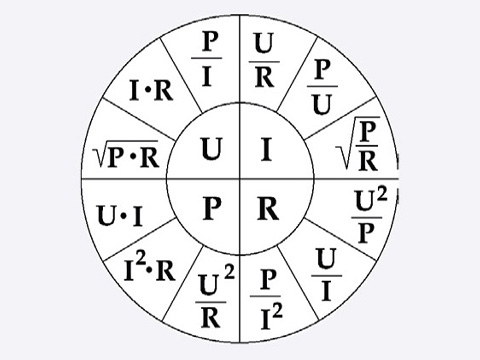

Интерфейс работает на сравнительно невысоких скоростях (до 512 Мбит/с), однако, как известно, даже на более низких частотах качество сигнала может значительно ухудшаться при отсутствии контроля:

- волнового сопротивления;

- ёмкости;

- индуктивности;

- задержек при выравнивании сигналов [1].

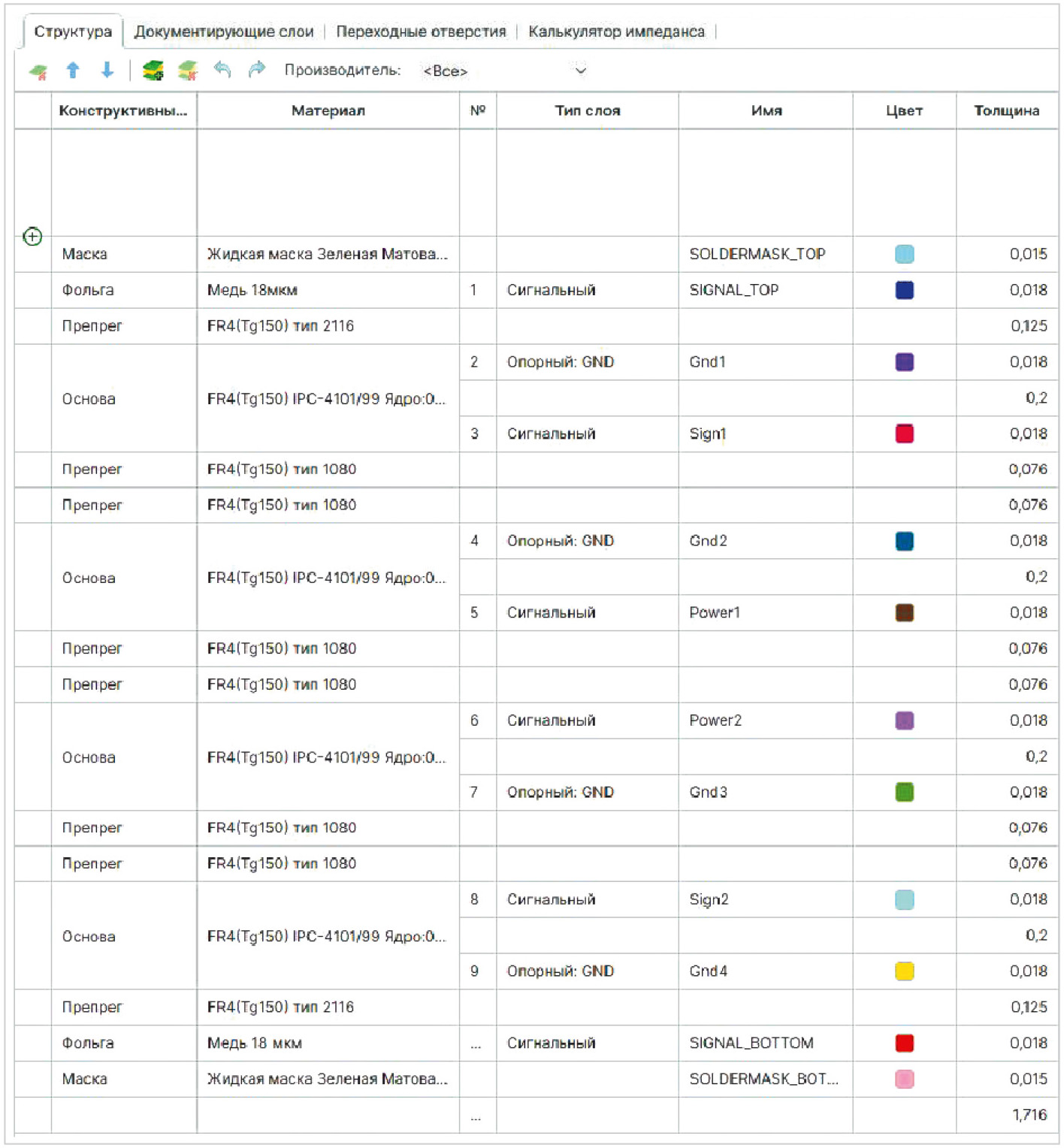

Конфигурация печатной платы

- Стек платы состоит из 10 слоёв.

- Слои 5 и 6 используются для питания.

- Часть трассировки расположена на внешних слоях (1 и 10).

- Основная высокоскоростная трассировка выполнена на 3-м и 8-м слое.

- Остальные слои используются в качестве опорных (рис. 1).

- Материал платы – стандартный FR4 (Er = 4,1).

Структура интерфейса DDR

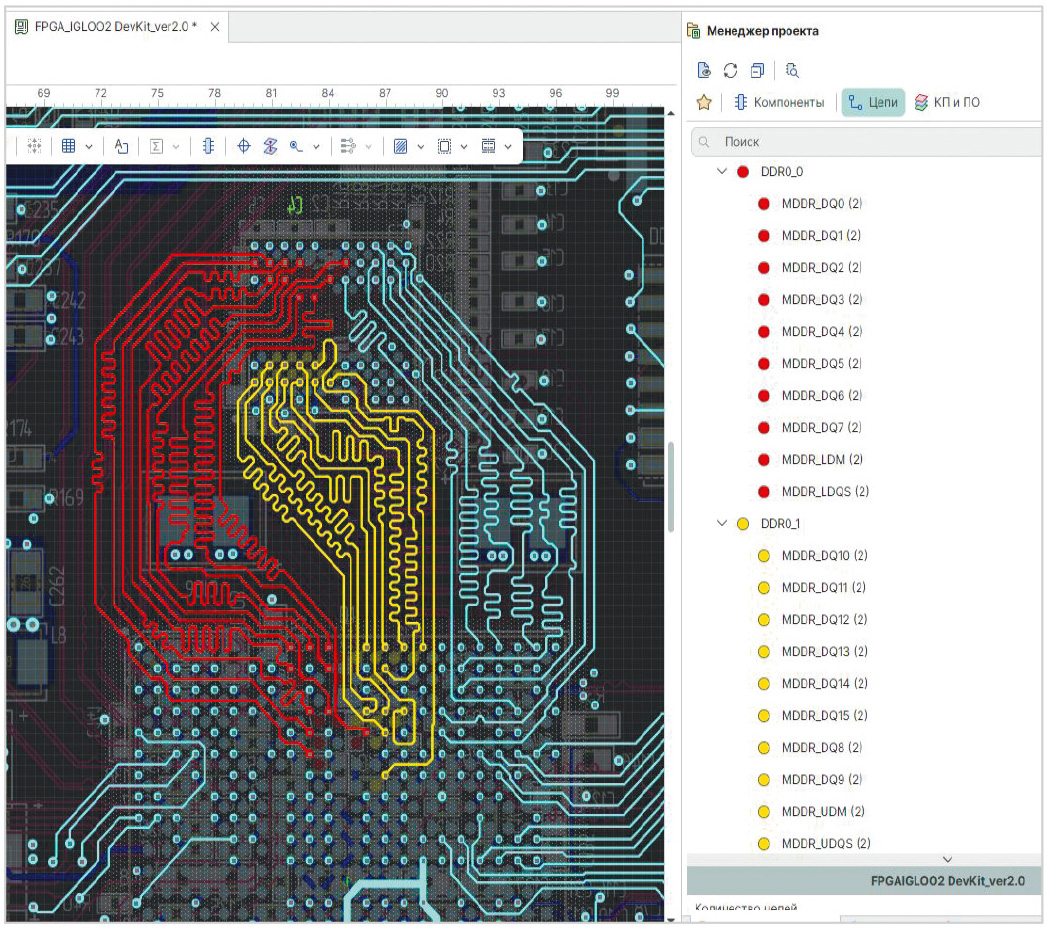

Рассматриваемый интерфейс состоит из нескольких групп сигналов.

- Одиночные сигналы (данные, маска и стробовый сигнал), 2 группы (рис. 2):

- группа DDR0_0;

- группа DDR0_1.

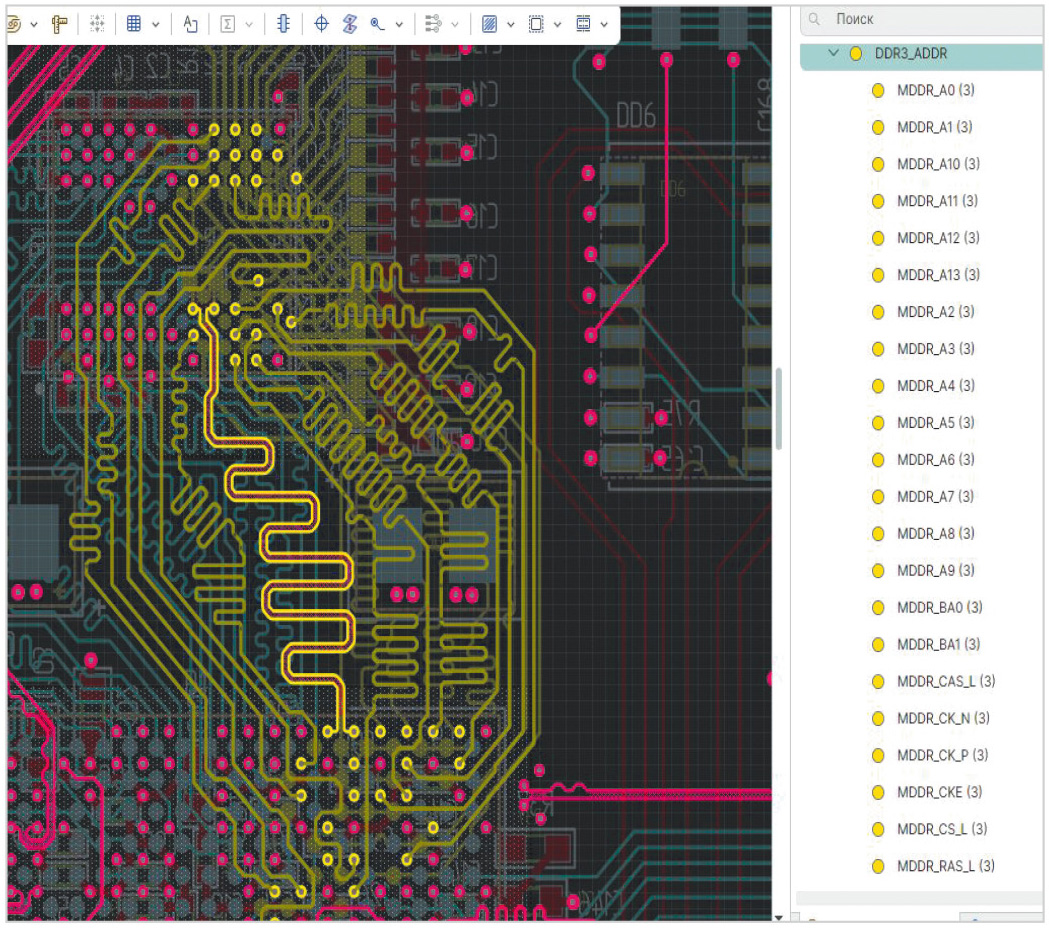

- Сигналы, объединённые в одну группу DDR3_ADDR:

- адресные;

- управляющие;

- синхросигнал в виде дифференциальной пары (рис. 3).

Подробный разбор первого варианта расчёта

Согласно рекомендациям производителя, проводники интерфейса DDR на печатной плате должны иметь следующие значения волнового сопротивления:

- для одиночных сигналов – 50 Ом;

- для дифференциальных пар – 100 Ом.

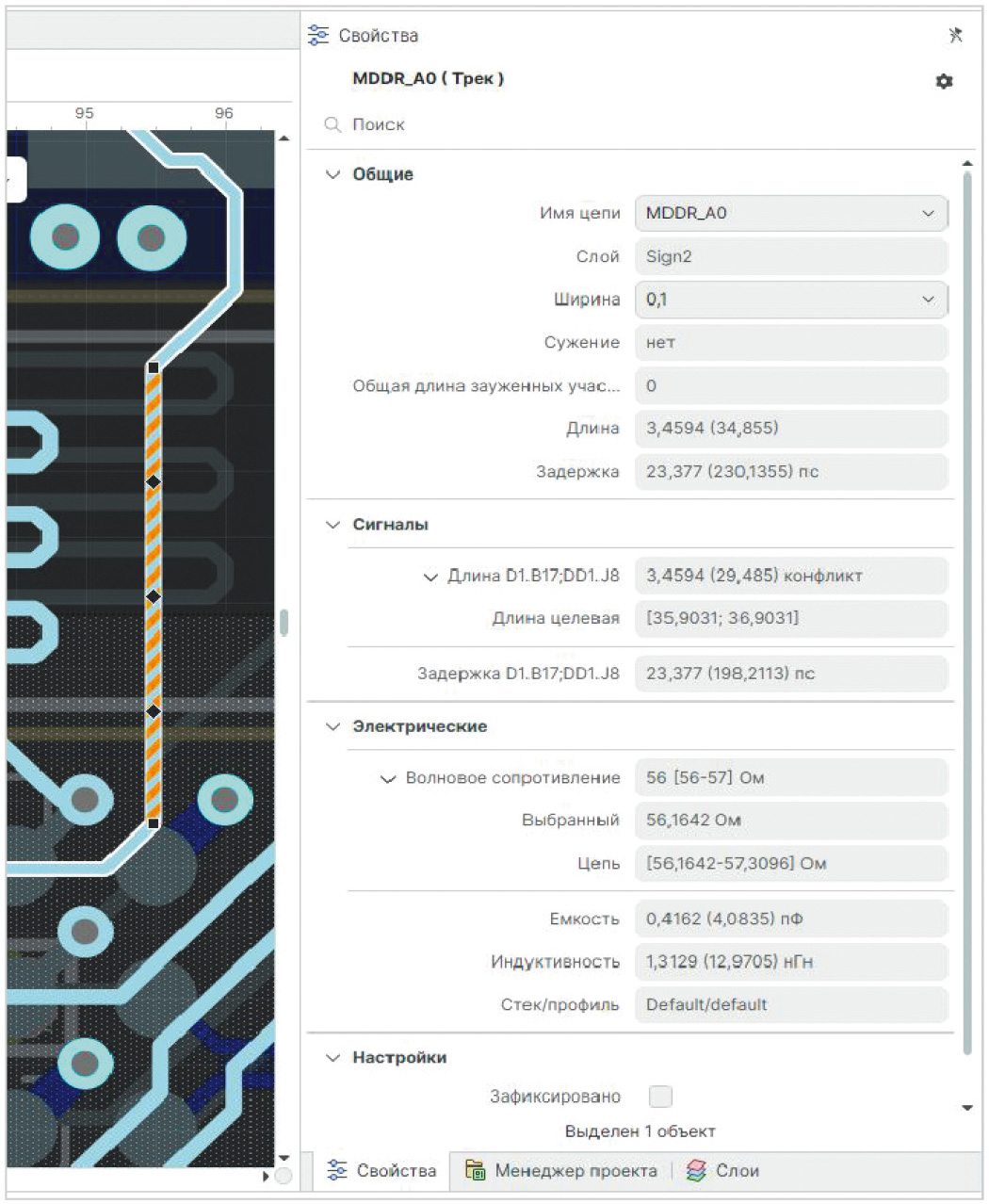

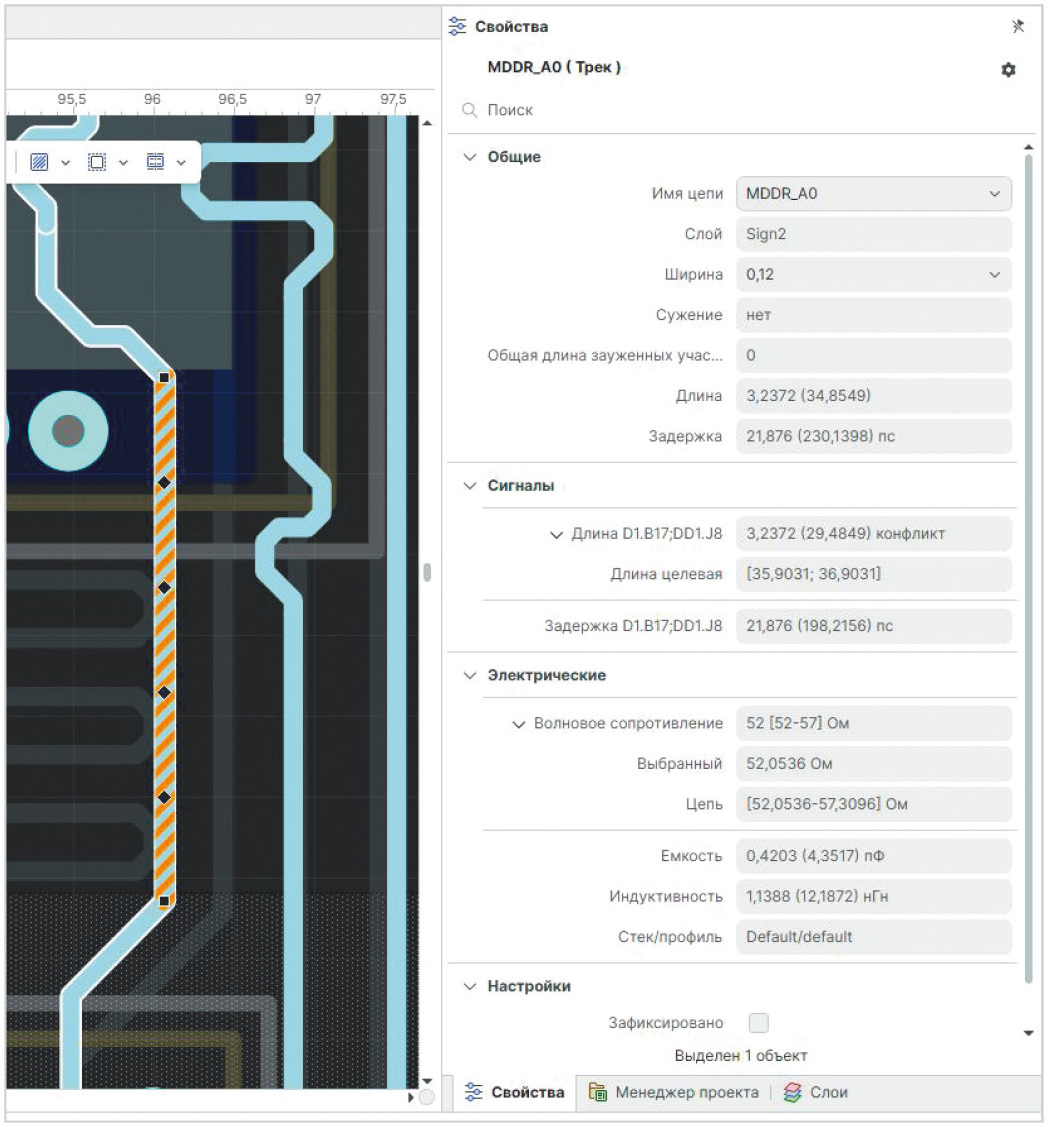

Пример: сигнал MDDR_A0

Рассмотрим в редакторе платы трек MDDR_A0 (рис. 4):

- расположение: 3-й слой (Sign2);

- ширина трека: 0,1 мм.

Раздел Общие

- Длина:

- выбранный сегмент – 3,45 мм;

- вся цепь – 34,85 мм.

- Задержка:

- выбранный сегмент – 23,37 пс;

- вся цепь – 230,13 пс (с учётом задержки в контактных площадках или выводах компонентов).

Раздел Сигналы

- Длина и задержка для всего сигнала.

- Ограничения, заданные в правилах для данного сигнала.

Раздел Электрические

- Волновое сопротивление:

- выбранный сегмент – 56 Ом;

- вся цепь – 56–57 Ом (диапазон мин.–макс.).

- Ёмкость:

- выбранный сегмент – 0,41 пФ;

- вся цепь – 4,08 пФ.

- Индуктивность:

- выбранный сегмент – 1,31 нГн;

- вся цепь – 12,97 нГн.

- Стек/Профиль: используются по умолчанию из конфигуратора слоёв.

Из результатов видно, что волновое сопротивление одиночного сигнала составляет 56 Ом, что не соответствует требуемым 50 Ом для DDR-интерфейса.

Для корректировки параметров возможны различные варианты, которые влияют на изменение волнового сопротивления.

В данном примере:

- материал и опорный слой (слой 2) – не менялся;

- изменилась только ширина проводника на 3-м слое с 0,1 мм до 0,12 мм (рис. 5).

Результаты после изменения ширины трека

После увеличения ширины проводника на 3-м слое с 0,1 мм до 0,12 мм наблюдаются изменения практически всех параметров.

Однако ключевым для нас является волновое сопротивление:

- выбранный сегмент: 52 Ом;

- вся цепь: 57 Ом.

Значение 52 Ом соответствует рекомендациям производителя (допускается отклонение не более ±10%).

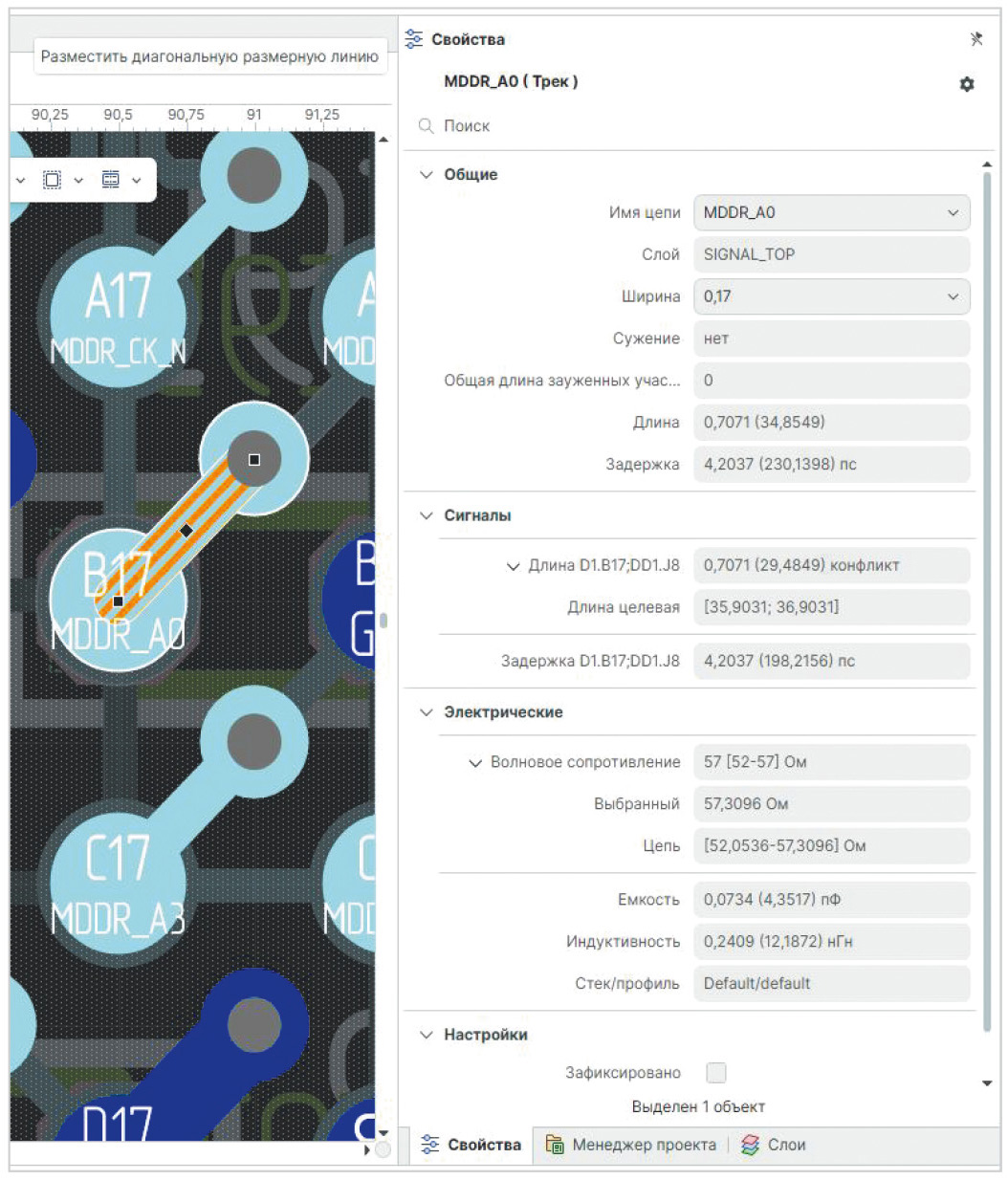

Причина отклонений по всей цепи

Небольшое отклонение диапазона до 57 Ом связано с наличием коротких отрезков треков на внешних слоях:

- отрезок трека на 1-м слое (B17, вывод D1);

- отрезок трека на 10-м слое (J8, вывод DD1).

Характеристики этих отрезков:

- ширина – 0,17 мм;

- длина – не более 0,7 мм.

Так как данные отрезки существенно короче минимальной допустимой электрической длины на рассматриваемой частоте, отклонение волнового сопротивления можно игнорировать (рис. 6).

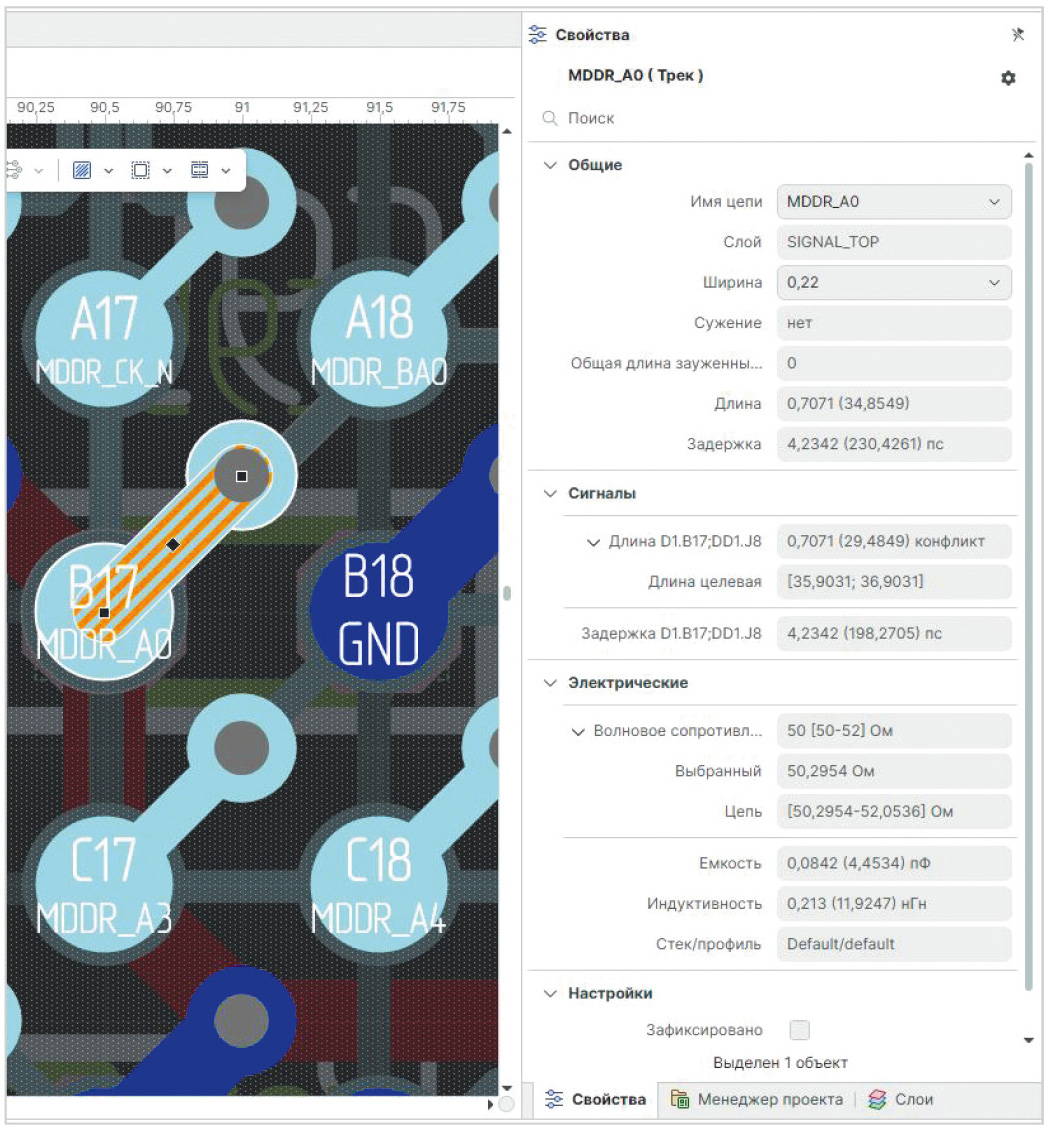

Доведение параметров всей цепи до требований

Чтобы получить значение волнового сопротивления всей цепи, максимально близкое к рекомендациям производителя, увеличим ширину коротких отрезков на внешних слоях до 0,22 мм (рис. 7).

Результат:

- выбранный сегмент: 50 Ом;

- вся цепь: 52 Ом, что полностью соответствует допускам производителя.

Аналогично можно рассчитать волновое сопротивление для всех одиночных треков под заданное волновое сопротивление 50 Ом интерфейса DDR.

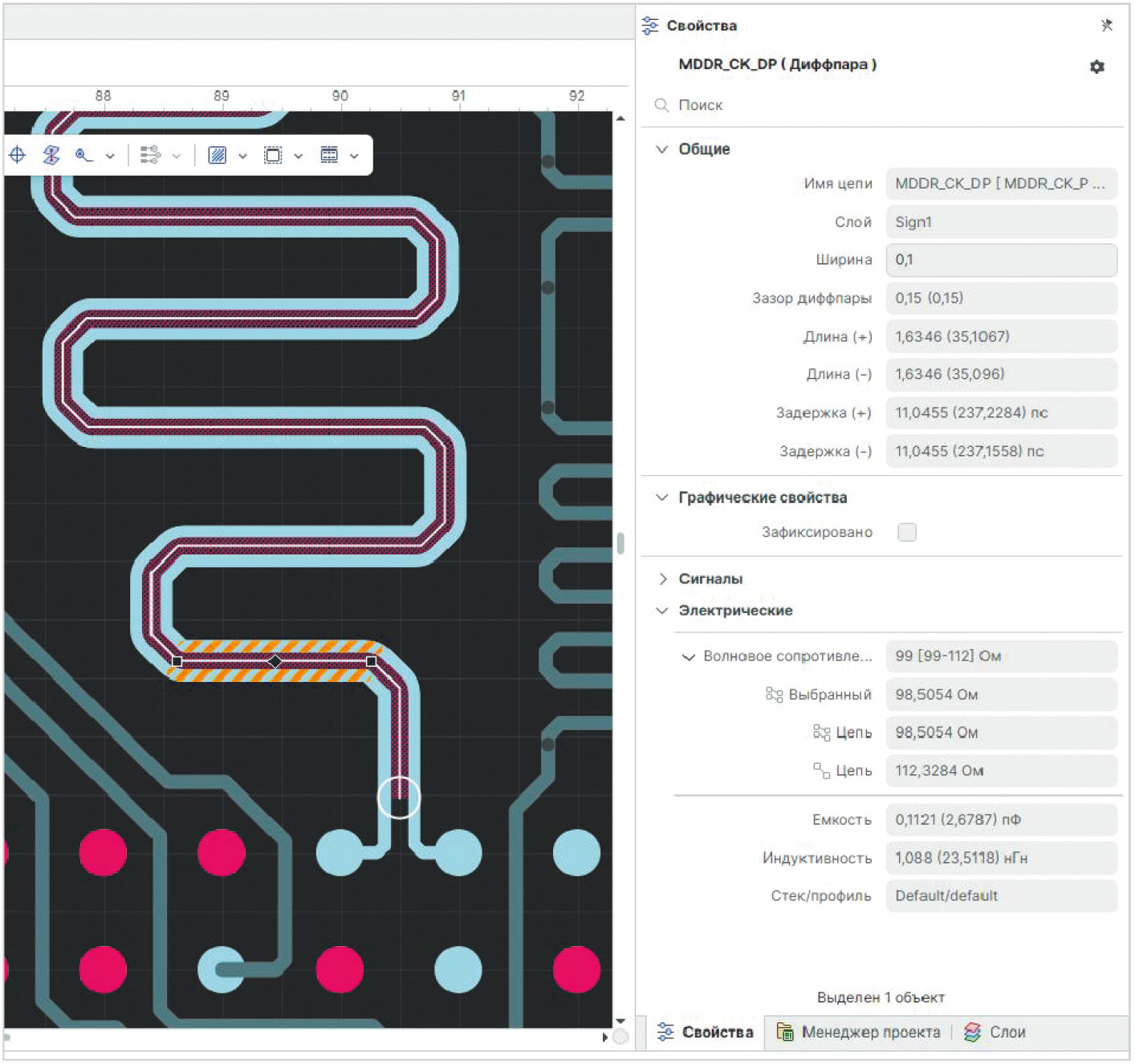

Расчёт параметров для дифференциальных пар

Поведение дифференциальных пар при изменении ширины проводников или зазора между ними аналогично одиночным трекам. При изменении параметров трассировки программа автоматически пересчитывает электрические характеристики в панели свойств.

В разделах Общие и Сигналы параметры рассчитываются отдельно для позитивного и негативного треков, входящих в состав дифф. пары.

В разделе Электрические отображаются значения волнового сопротивления:

- выбранный сегмент (застегнутая цепь) – 99 Ом;

- диапазон всех сегментов застегнутой цепи – 99 Ом;

- сумма всех сегментов расстёгнутой цепи – 112 Ом.

Анализ результатов для дифф. пары

Значение 99 Ом для застегнутой цепи соответствует целевым рекомендациям производителя (100 Ом ±10%).

Для расстёгнутой цепи диапазон значений (112 Ом) может значительно отличаться от целевого импеданса. Это связано с тем, что при увеличении зазора между проводниками уменьшается ёмкость, и, как следствие, увеличивается волновое сопротивление. Однако на низких частотах такое отклонение (на коротких отрезках) не оказывает значительного влияния на качество сигнала (рис. 8).

Аналогично можно рассчитать волновое сопротивление для всех дифф. пар под заданное волновое сопротивление 100 Ом интерфейса DDR.

В данной статье рассмотрен первый вариант расчёта электрических параметров линий передачи на печатной плате с использованием САПР Delta Design и модуля SimPCB на примере интерфейса DDR.

Основные выводы

1. Возможности автоматического расчёта.

- Программа позволяет получать параметры для одиночных треков и дифференциальных пар прямо в редакторе платы, включая длину, задержку, волновое сопротивление, ёмкость и индуктивность.

- Все расчёты учитывают стек и опорные слои из конфигуратора слоёв.

2. Изменение параметров для соответствия требованиям.

- Для одиночных треков и дифф. пар целевые значения расчётных параметров достигаются путём изменения ширины проводника или ширины и зазора для дифф. пары, изменением в структуре конфигурации слоёв параметров материалов и порядком опорных слоёв.

3. Практическая применимость.

- Даже на низких частотах контроль волнового сопротивления, ёмкости и индуктивности критически влияет на качество сигналов интерфейса DDR и других похожих интерфейсов.

4. Вывод по методике.

- Автоматический расчёт в редакторе платы позволяет быстро оценить и скорректировать параметры трасс без предварительного создания профиля импеданса или использования стороннего САПР.

- Этот подход удобен для первичного анализа, однако для полного контроля (проверки DRC) и точного соблюдения всех требований к высокоскоростным сигналам, расположенным в разных слоях, рекомендуется использовать профиль импеданса (второй вариант расчёта), который будет рассмотрен в следующих статьях.

Литература

- Кечиев Л.Н. Печатные платы и узлы гигабитной электроники. М.: Грифон, 2017. 424 с.

© СТА-ПРЕСС, 2025

Если вам понравился материал, кликните значок — вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал —не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!