Введение

В предыдущих двух статьях мы знакомились с системой цифрового моделирования Delta Design Simtera с точки зрения разработчика САПР. В первой статье [1] оценивается сложность создания библиотек тестов для верификации программного пакета Simtera. Приводятся примеры простых и сложных тестов на языке Verilog. Во второй статье [2] рассматриваются результаты сравнения параметров промежуточной версии 3.6 Delta Design Simtera с аналогичными зарубежными системами: скорость моделирования, компиляции, времени запуска, поддерживаемых семейств ПЛИС (программируемых логических интегральных схем). Что касается темы данной статьи, то она представляется интересной не только пользователям САПР, применяющим языки описания аппаратуры (HDL) типа VHDL и Verilog, но и разработчикам-схемотехникам РЭА, использующим графические редакторы для ввода описаний проектируемых объектов. Рассматривается наполнение базы библиотек компонентов САПР DeltaDesign Simtera цифровыми моделями, их параметризация и использование.

Схемотехнические редакторы и их применение

Как известно, схемотехнические (BD) графические редакторы имеются практически во всех системах автоматизации проектирования РЭА. Они используются не только при проектировании принципиальных электрических схем радиоэлектронных устройств, но и при разработке проектов БИС и ПЛИС. В некоторых САПР ПЛИС вендоры предлагают схемотехнический редактор как основной инструмент разработки. В нём разработчик формирует соединения шин и проводников проектируемой системы с IP-ядрами, PLL и прочими компонентами чипа. Такое решение, например, предлагают пользователям компания АМD в САПР ПЛИС Vivado [3], компания Microchip в IDE (интегрированной среде разработки) Libero [4] и другие. Проблема автоматического перевода HDL-описаний блоков в блок-диаграммные также решена в большинстве САПР. Особенно просто это делается в САПР Active-HDL.

К плюсам блок-диаграммного способа описаний проектов можно отнести наглядность, которая падает при увеличении количества блоков (пара дюжин- предел). К минусам отнесём ухудшение переносимости проектов из-за несовместимости файлов BD.

В САПР Delta Design Simtera используется общий для аналогового и для цифрового моделирования графический редактор, в основном ориентированный на проектирование печатных плат по нормативам ЕСКД. САПР Delta Design [5] обеспечивает:

- формирование базы данных радиоэлектронных компонентов и поддержание её в актуальном состоянии;

- разработку схем электрических принципиальных;

- проведение моделирования аналоговых и цифровых схем, анализ результатов моделирования;

- разработку конструкции печатных плат;

- расстановку компонентов и проведение полуавтоматической и автоматической трассировки печатных плат;

- выпуск конструкторской документации в соответствии со стандартами;

- выпуск производственной документации, в том числе для автоматизированных производственных линий;

- подготовку данных для составления перечня закупаемых изделий и материалов, необходимых для реализации проекта.

Знакомство с Delta Design Simtera. Графический интерфейс пользователя

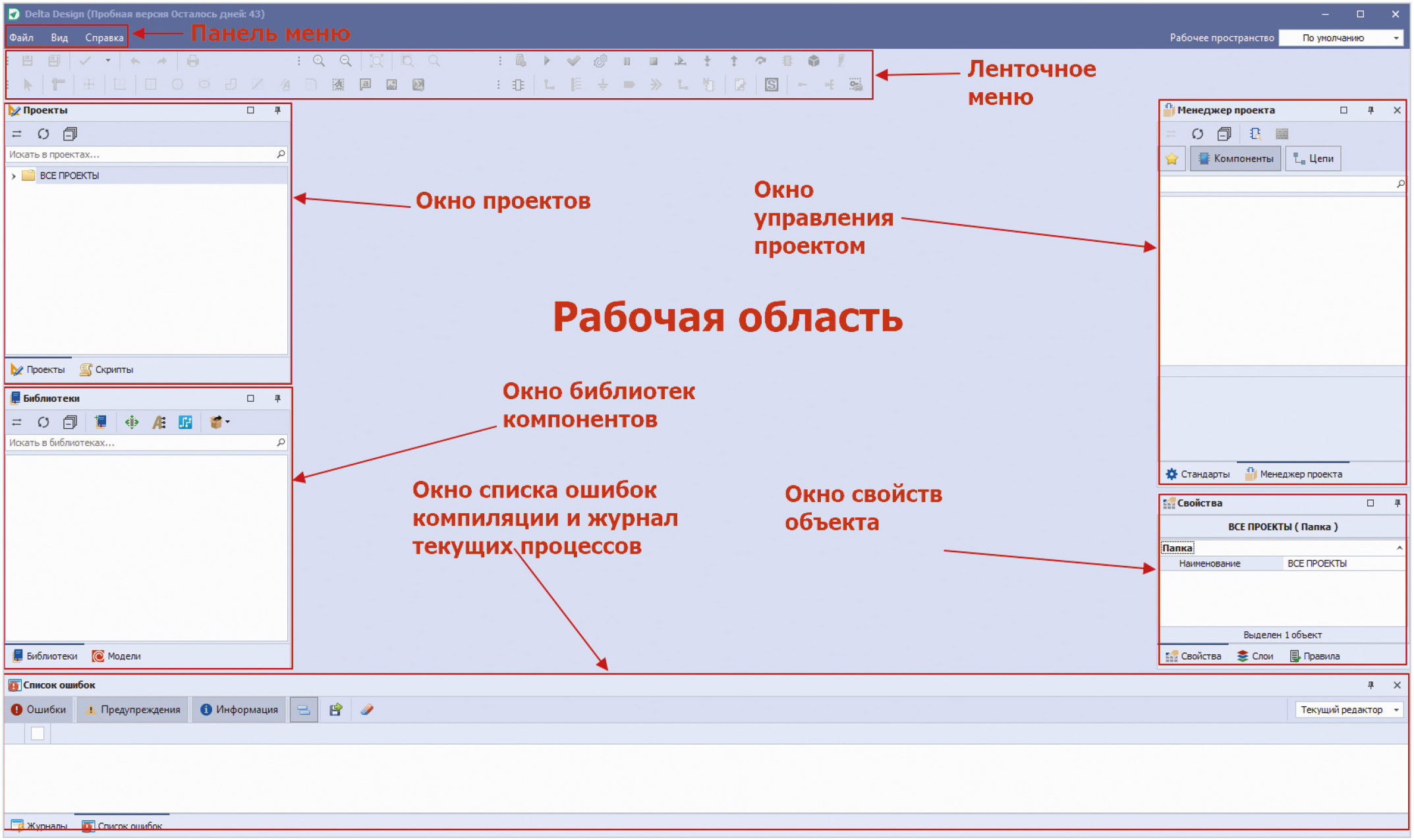

Delta Design Simtera – единая среда работы с модулями цифрового проектирования и моделирования. Графический интерфейс пользователя состоит из подокон, которые изменяются в зависимости от выбранного в данный момент объекта для работы (контекста). Общий вид интерфейса приведён на рис. 1. Этот интерфейс используется и для системы аналогового моделирования SimOne [6].

Панель меню содержит в себе все меню, необходимые для выполнения действий с проектами, схемами, компонентами и т.д.

Ленточное меню содержит вынесенные пункты из меню панели для удобства быстрого доступа.

Окно проектов отображает древовидную структуру проектов. Каждый проект представляет из себя либо блок-диаграмму – схему с компонентами, либо её описание на языках описания аппаратуры. В проекте имеются дополнительные части. Например, если необходимо провести моделирование схемы, то в проекте будут располагаться файлы временны́х диаграмм – осциллографов. Если необходимо создать на основе схемы печатную плату, будет располагаться проект печатной платы и т.д.

Окно библиотек компонентов содержит в своём составе библиотеки компонентов. Каждый компонент в системе цифрового моделирования Simtera – это цифровое представление реального схемотехнического или электротехнического элемента на языке описания цифровой аппаратуры VHDL или Verilog (в подсистеме аналогового моделирования SimOne – это аналоговая модель в формате P-Spice). Каждый компонент должен иметь УГО (условно-графическое обозначение).

Окно управления проектом частично дублирует функционал окна проектов, но отображает структуру конкретного проекта.

Окно свойств – это окно отображения свойств выделенного объекта. Например, компонента, файла, схемы, печатной платы и т.д.

В окне списка ошибок и журнала в разделе «Ошибки» можно просмотреть сообщения об ошибках, обнаруженных системой при сборке проекта или компиляции кода компонента, а также предупреждения. В разделе «Журнал» можно посмотреть протокол работы системы с проектом.

Рабочая область – зона, расположенная в центре окна программы и содержащая дополнительные подокна, с которыми мы будем непосредственно работать. В рабочей области могут быть окна редактирования УГО компонента, схемы и т.д.

Создание компонента библиотеки цифровых моделей компонентов

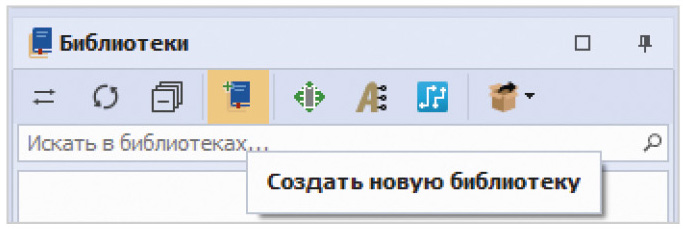

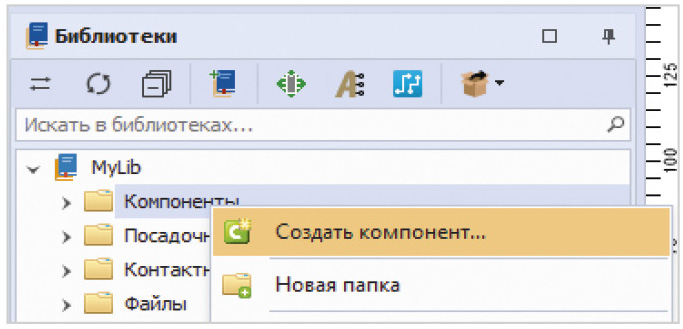

Как уже было сказано ранее, компонент – это модель некоторого физического элемента или модуля. При схемотехническом цифровом моделировании пользователь, в основном, использует готовые компоненты из библиотеки цифровых моделей. Собственные компоненты – блоки пользователя создаются редко. Тем не менее иногда это приходится делать, для чего придётся освоить основы HDL. В качестве примера рассмотрим компонент – генератор (источник) непериодического сигнала. Создание пользователем собственного блока (компонента) начинается с создания новой библиотеки компонентов (рис. 2). Назовём нашу новую библиотеку MyLib.

На рис. 3 можно увидеть структуру создаваемой библиотеки MyLib. Нас интересует папка Компоненты. В ней будет находиться наш новый компонент, который можно создать путём нажатия правой кнопки мыши на папке Компоненты и выбора пункта «Создать компонент».

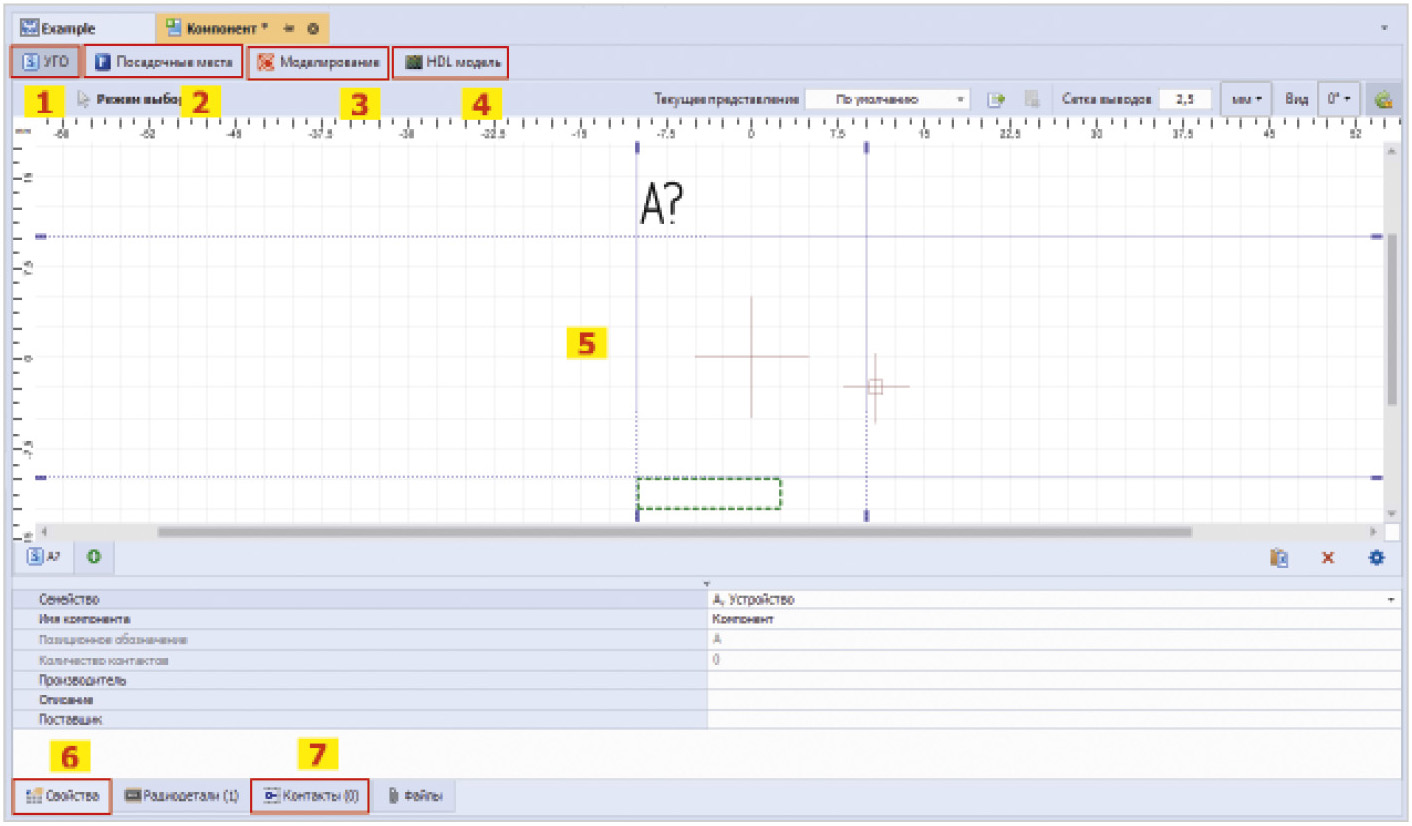

В рабочей области появится вкладка окна создания компонента (рис. 4).

Рабочая область инструмента редактирования компонентов представлена следующими разделами.

1) УГО – область задания условно-графического обозначения компонента, описываются входы и выходы сигналов.

2) Посадочные места – для задания посадочных мест компонента на печатной плате.

3) HDL – в нём описывается цифровая модель на языках VHDL или Verilog. Её мы и будем использовать.

4) Рабочая область раздела УГО, в которой можно создавать графические обозначения компонентов.

5) Свойства – тут описываются свойства компонента, такие как семейство, имя и пр.

6) Контакты – в данном разделе описываются соотношения контактов компонентов с обозначениями на УГО.

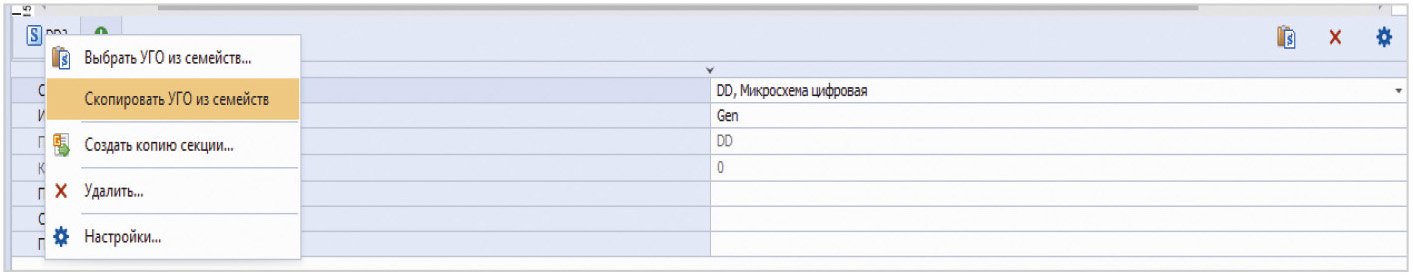

Приступим к созданию нашего пользовательского блока – генератора непериодического сигнала. Первое, что необходимо сделать, – изменить стандартное название Компонент на предлагаемое пользователем (в нашем примере Gen) и выбрать семейство (например, DD – микросхема цифровая). Далее необходимо добавить УГО. Воспользуемся моделью из библиотеки стандартных обозначений. Для этого нажмём правой кнопкой на вкладку внутреннего УГО-компонента и выберем «Скопировать УГО из семейства» (рис. 5).

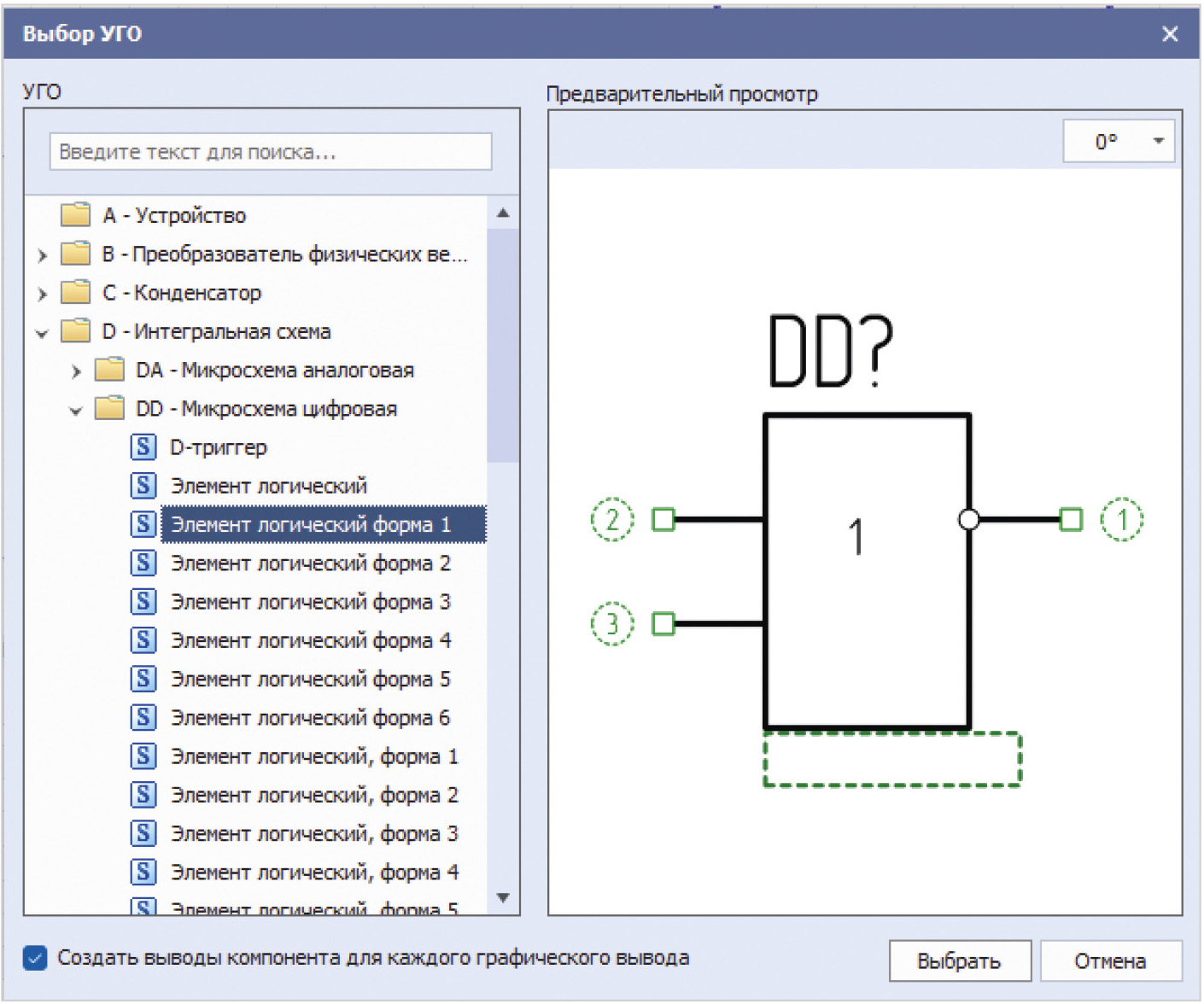

Выберем логический элемент 1 из раздела DD (рис. 6).

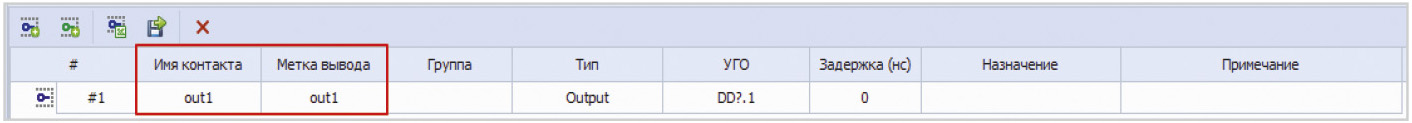

Теперь необходимо ненужные в нашем случае входные контакты удалить и изменить имена контактов согласно требованиям по именованию стандартов Verilog (IEEE 1800-2005) и VHDL (IEEE 1076-2008) (рис. 7).

Приступим к описанию модели нашего компонента. Для этого перейдём в раздел «HDL модель» и добавим новую модель. Сгенерируем базовый код компонента с помощью кнопки «Генерировать». Работать будем на VHDL. В полученный код необходимо добавить процесс следующего содержания, задающий временну́ю диаграмму сигнала с начальным значением 0, значением 1 в момент 20 наносекунд и т.д.:

out1 <= transport '0' after 0 ns, '1' after 20 ns, '0' after 70 ns, '1' after 300 ns;

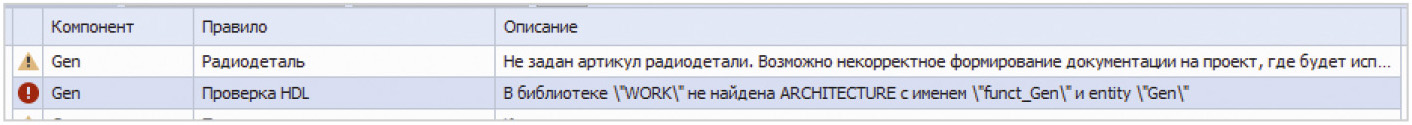

При сохранении компонента произойдёт автоматическая проверка УГО и HDL-кода компонента. При наличии ошибок, например, в VHDL-коде, в панели «Список ошибок» появятся сообщения c указанием типов ошибок и их расположения – номер строки кода и позиция в строке (рис. 8).

Создание проекта и добавление HDL-проекта

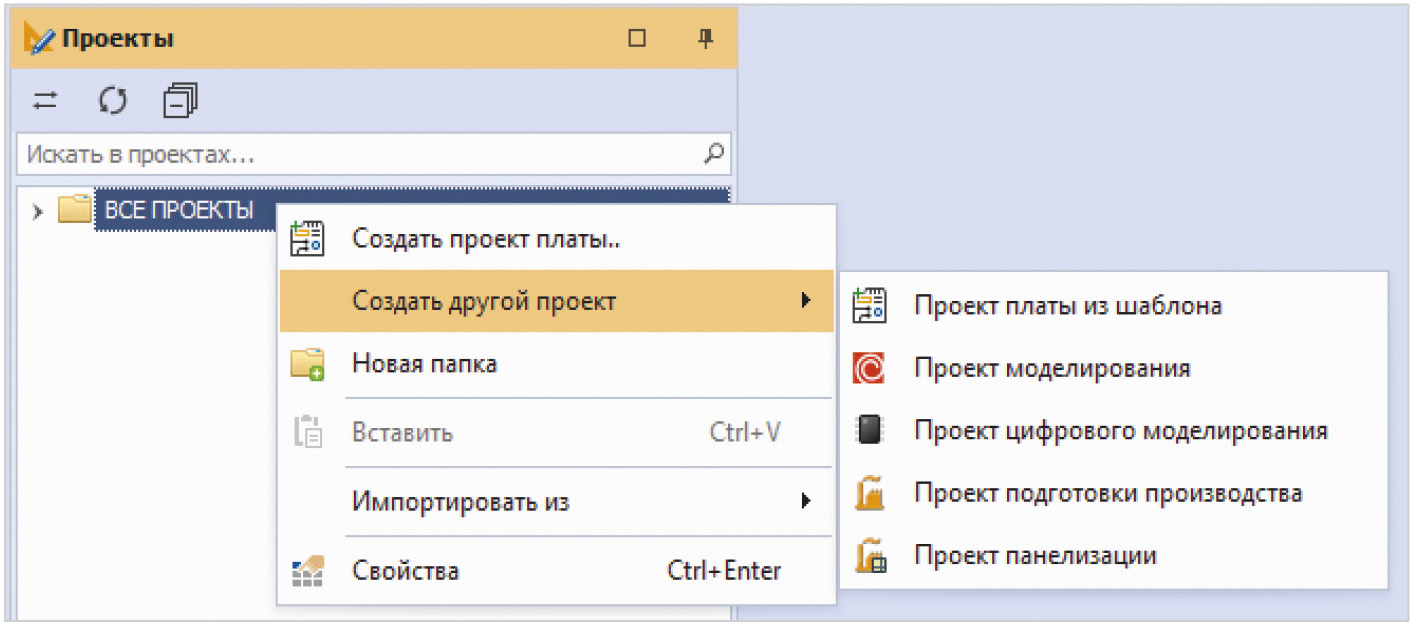

Для создания проекта необходимо кликнуть правой клавишей мышки по папке «Все проекты» панели «Проекты» и выбрать интересующий нас тип проекта или создать подпапку (рис. 9).

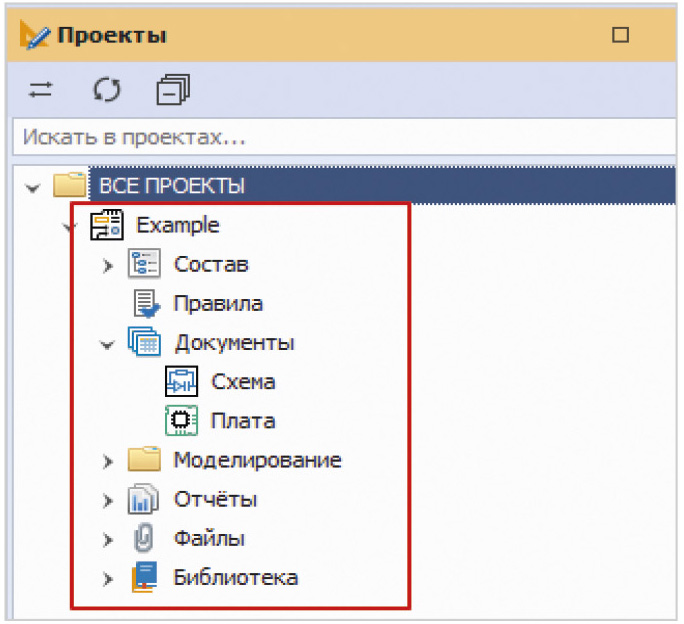

Проект платы включает все файлы модулей Delta Design от файла схемы до файлов документации. Также имеются проекты более узкого профиля – цифрового и аналогового моделирования. При создании проекта печатной платы необходимо ввести имя проекта с использованием латиницы, иначе в дальнейшем могут возникнуть проблемы компиляции. После создания проекта мы получим структуру, приведённую на рис. 10.

Здесь раздел «Документы» содержит принципиальную схему и макет печатной платы. В папке «Моделирование» могут располагаться файлы моделирования схемы. «Отчёты» содержат файлы документации. «Библиотека» – это локальное хранилище компонентов, доступных только в данном проекте. «Файлы» – может содержать любые дополнительные файлы. Остальные разделы пока нас не интересуют.

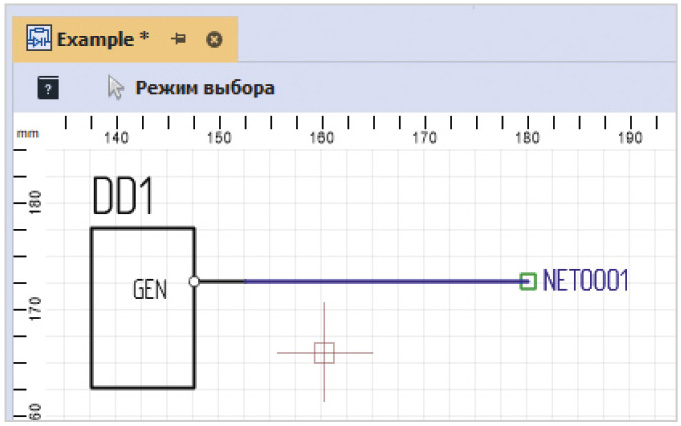

Создадим нашу схему путём перетаскивания нового компонента на рабочую область и добавления проводника к выходу компонента (рис. 11).

Теперь к нашему проекту необходимо добавить HDL-проект, в котором будут находиться все файлы, описывающие схему. В данном случае будет всего два файла: один, содержащий код компонента Gen, который должен быть получен на основе кода, описанного нами в свойствах блока, и второй – файл описания связей компонентов схемы, который описывал бы связь линии (цепи NET0001) с выходом компонента Gen.

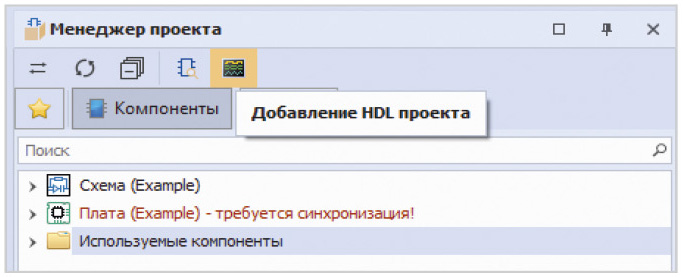

Для добавления проекта необходимо нажать на кнопку «Добавление HDL проекта» в окне Менеджера проекта (рис. 12).

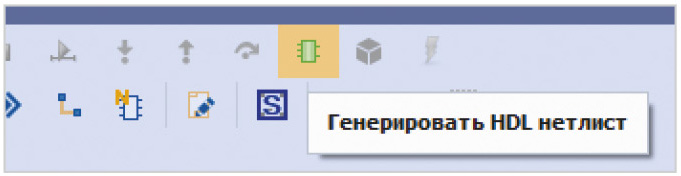

Нетлист – это совокупность HDL-файлов, которые полностью описывают нашу схему. По сути, мы создаём графическую схему из блоков, соединяем их связями для того, чтобы получить корректное описание данной модели на языках описания аппаратуры. Для генерации нетлиста необходимо нажать на кнопку «Генерировать HDL нетлист» в ленточном меню (рис. 13).

Программа предложит выбрать HDL-проект, в который будут сгенерированы файлы, описывающие схему. Выбираем наш проект Example и нажимаем «ОК».

Сборка проекта и проведение симуляции

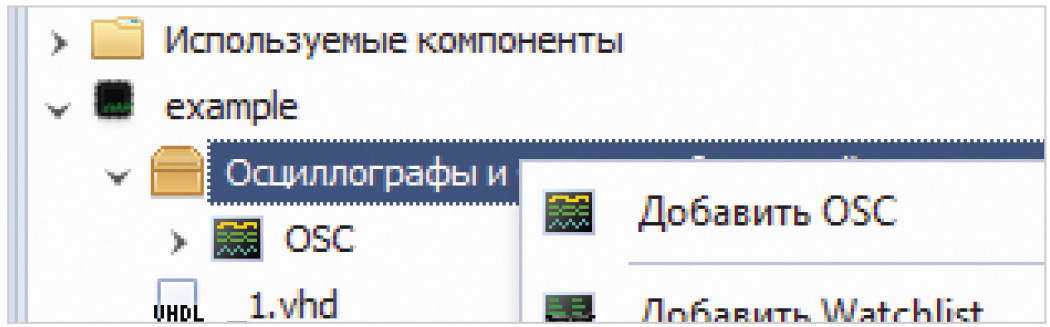

Для накопления и просмотра временно́й диаграммы – результата симуляции нам потребуется виртуальный осциллограф, который можно добавить в Менеджере проекта кликом правой кнопки по папке «Осциллографы и списки наблюдений» – «добавить OSC» (рис. 14).

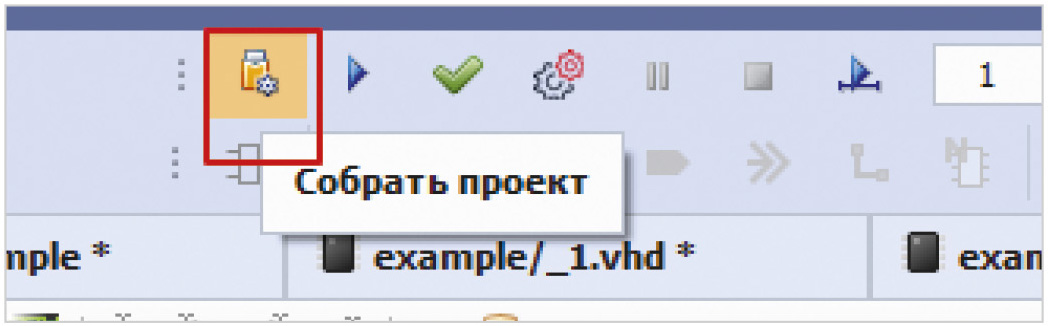

Для сборки проекта в ленточном меню выбираем соответствующий пункт (рис. 15).

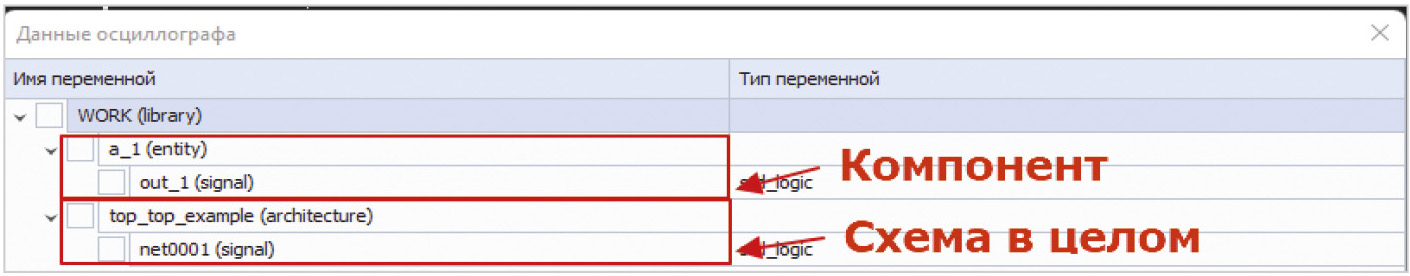

Далее откроем осциллограф и нажмём на кнопку добавления данных для отслеживания. Нам доступны входы и выходы каждого блока по отдельности, а также значения на проводниках – соединителях компонентов. За блоки отвечают названия файлов блоков, а за соединения – главный файл с префиксом top (рис. 16).

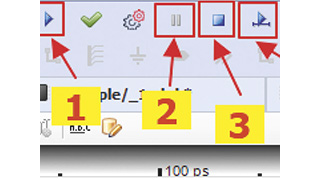

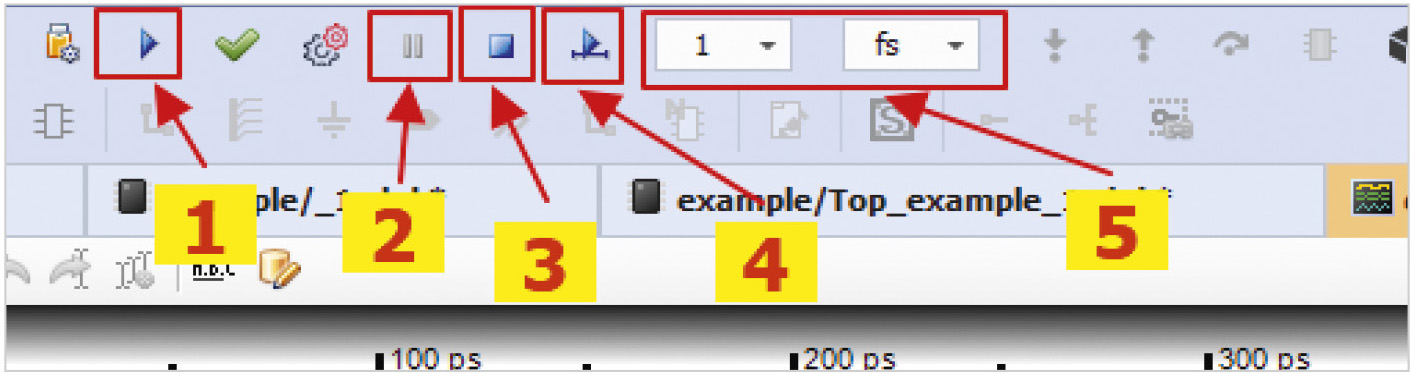

Запуск моделирования осуществляется из ленточного меню (рис. 17):

1) запуск моделирования на неограниченное время;

2) приостановка моделирования;

3) остановка моделирования;

3) моделирование промежутка времени;

4) выбор длительности промежутка времени.

Для отслеживания поведения нашего генератора выберем длительность моделирования 400 ns, запустив моделирование на ограниченное время. Перед моделированием система спросит, какой модуль является главным, то есть точкой входа моделирования. Выбираем модуль с приставкой top, так как хотим запустить симуляцию всей схемы.

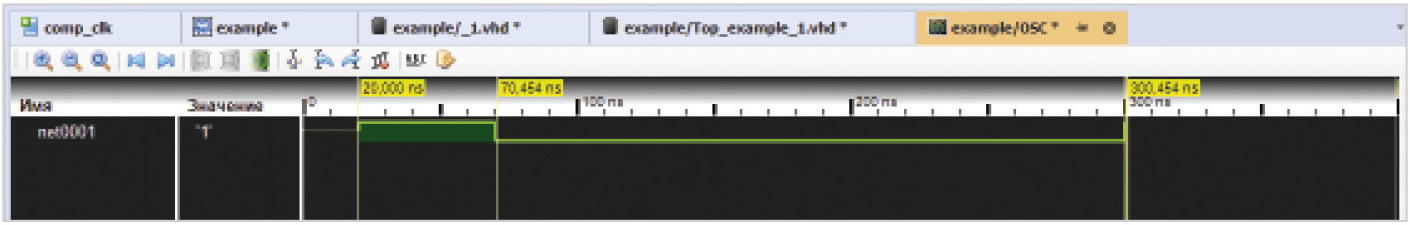

Получим осциллограммы, представленные на рис. 18.

Как нетрудно увидеть, перепады находятся на 20, 70 и 300 наносекундах, как и в коде, которым мы описывали компонент.

Библиотека цифрового моделирования

В модуле цифрового моделирования Simtera имеется библиотека моделей готовых компонентов. Внутренний состав модели включает в себя УГО и HDL-модели, которые можно просмотреть, если нажать правой клавишей на элемент и выбрать пункт «Изменить». Далее необходимо перейти в раздел «HDL модель» и переключить слайдер на VHDL-код.

Заключение

Схемотехническое проектирование в Delta Design Simtera позволяет проводить цифровое моделирование схем в «несколько кликов» при наличной компонентной базе.

В отсутствии таковой – задача её создания облегчается за счёт встроенных шаблонов, а также преднаполненной базы УГО и HDL-моделей. Последующая за цифровым моделированием выгрузка нетлиста в сторонние системы проектирования позволяет использовать Delta Design Simtera в качестве альтернативной системы проектирования и моделирования. А с учётом поддержки отечественных ПЛИС и БМК DeltaDesign Simtera является единственной системой полного цикла разработки для российских чипов.

Напоминаем также, что открыто бета-тестирование DeltaDesign Simtera. Получить тестовую версию системы можно, написав запрос на адрес info@eremex.ru либо запросив её в Telegram-сообществе.

Литература

- Малышев Н., Поляков А. Библиотеки HDL-тестов для систем моделирования цифровой аппаратуры // Современная электроника. 2023. № 3. С. 12–15.

- Малышев Н., Поляков А. Сравнение систем цифрового моделирования электронной аппаратуры // Современная электроника. 2023. № 4. С. 8–10.

- URL: www.xilinx.com.Vivado Design Suite User Guide: Designing IP Subsystems Using IP Integrator (UG994).

- URL: www. microchip.com. Libero SOC design Suit Versions 2023. 22023202023.1 to 1.

- Система цифрового моделирования Simtera, Руководство пользователя // URL: https://www.eremex.ru/upload/iblock/c85/jlk2v87u5vkv1pfsgp2xyu0f07poqrqn/DeltaDesign.Simtera.pdf.

- Смирнов А., Гимеин А. Схемотехническое моделирование DeltaDesign SimOne // Современная электроника. 2021. № 9. С. 34–36.

Если вам понравился материал, кликните значок — вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал —не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!