Модели ПЛИС с АЦП

В состав части ПЛИС семейства MAX10 от Intel (Altera) производитель включил встроенный аппаратный модуль АЦП (ADC Hard IP Block), имеющий в своём составе встроенный аналоговый температурный датчик. Указанная особенность этих ПЛИС позволяет в рамках одной микросхемы реализовать как оцифровку, так и всю необходимую цифровую обработку внешних по отношению к ПЛИС аналоговых сигналов, в том числе сигнала от встроенного температурного датчика.

Тип АЦП семейства MAX10 – АЦП последовательного приближения (ADC SAR), обеспечивающий оцифровку одной выборки входного напряжения за один период синхросигнала.

ПЛИС семейства MAX10, содержащие АЦП и температурный датчик, имеют в обозначении буквы SA или DA, например 10M08SAE144C8G. При этом буква S или D указывает на количество необходимых для данного типа ПЛИС внешних напряжений питания: одно (Single Supply) или два (Dual Supply) [3]. ПЛИС типа Single supply для работы цифровой части (цифрового ядра и линий ввода/вывода общего назначения GPIO) и модуля АЦП требуют напряжения питания с номинальным значением 3,3 В. ПЛИС типа Dual supply для работы цифровой части требуют напряжения питания с номинальным значением 1,2 В, а для работы модуля АЦП – напряжения питания с номинальным значением 2,5 В.

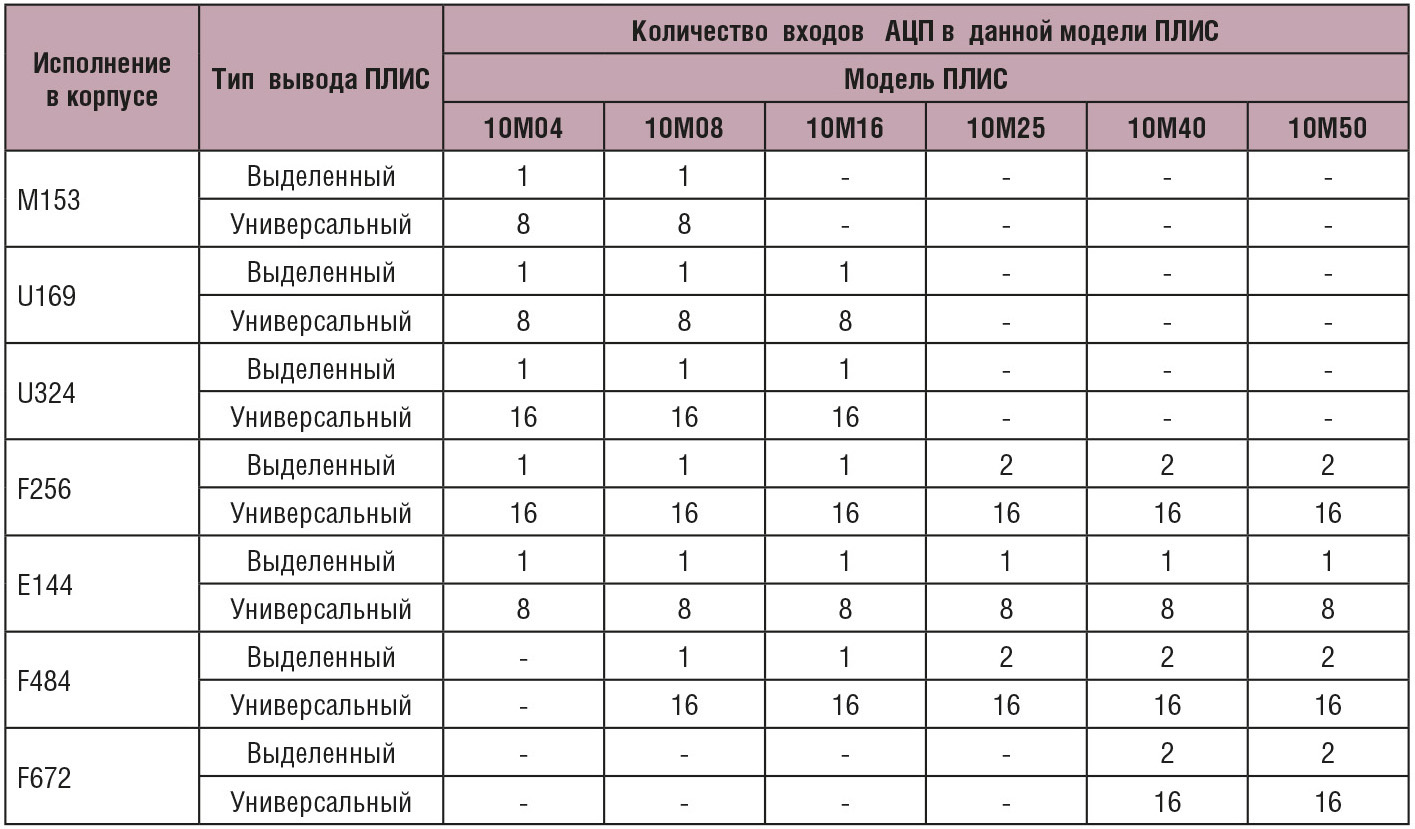

Буква A в обозначении модели ПЛИС указывает на наличие в составе ПЛИС модуля АЦП с датчиком температуры и массива пользовательской Flash-памяти (Analog and Flash Features) [3]. В зависимости от модели ПЛИС внутри семейства MAX10, она может содержать один или два аппаратных модуля АЦП. В таблице 1 перечислены все модели ПЛИС, имеющие встроенные аппаратные модули АЦП, с указанием количества модулей АЦП в ПЛИС [1].

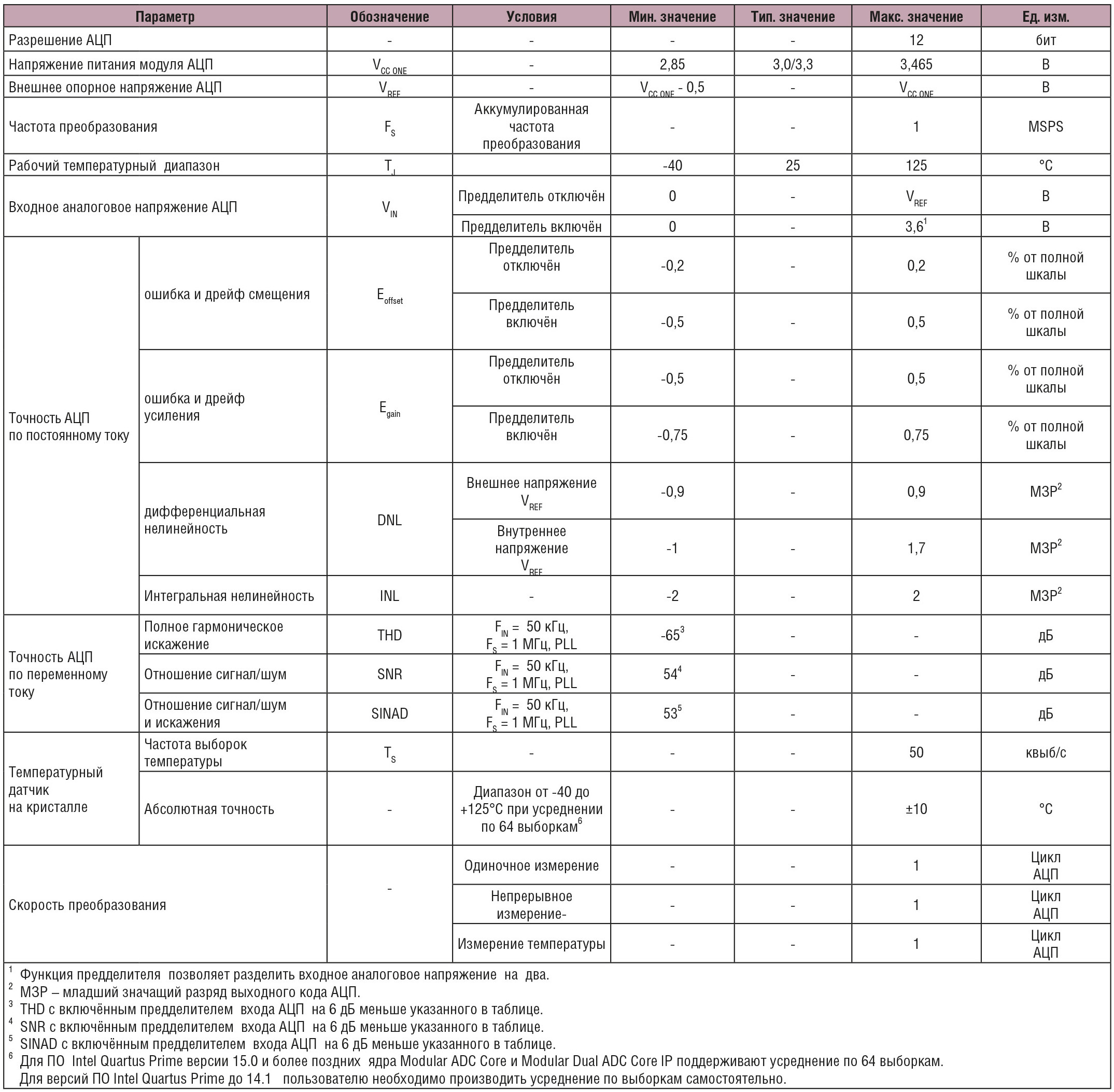

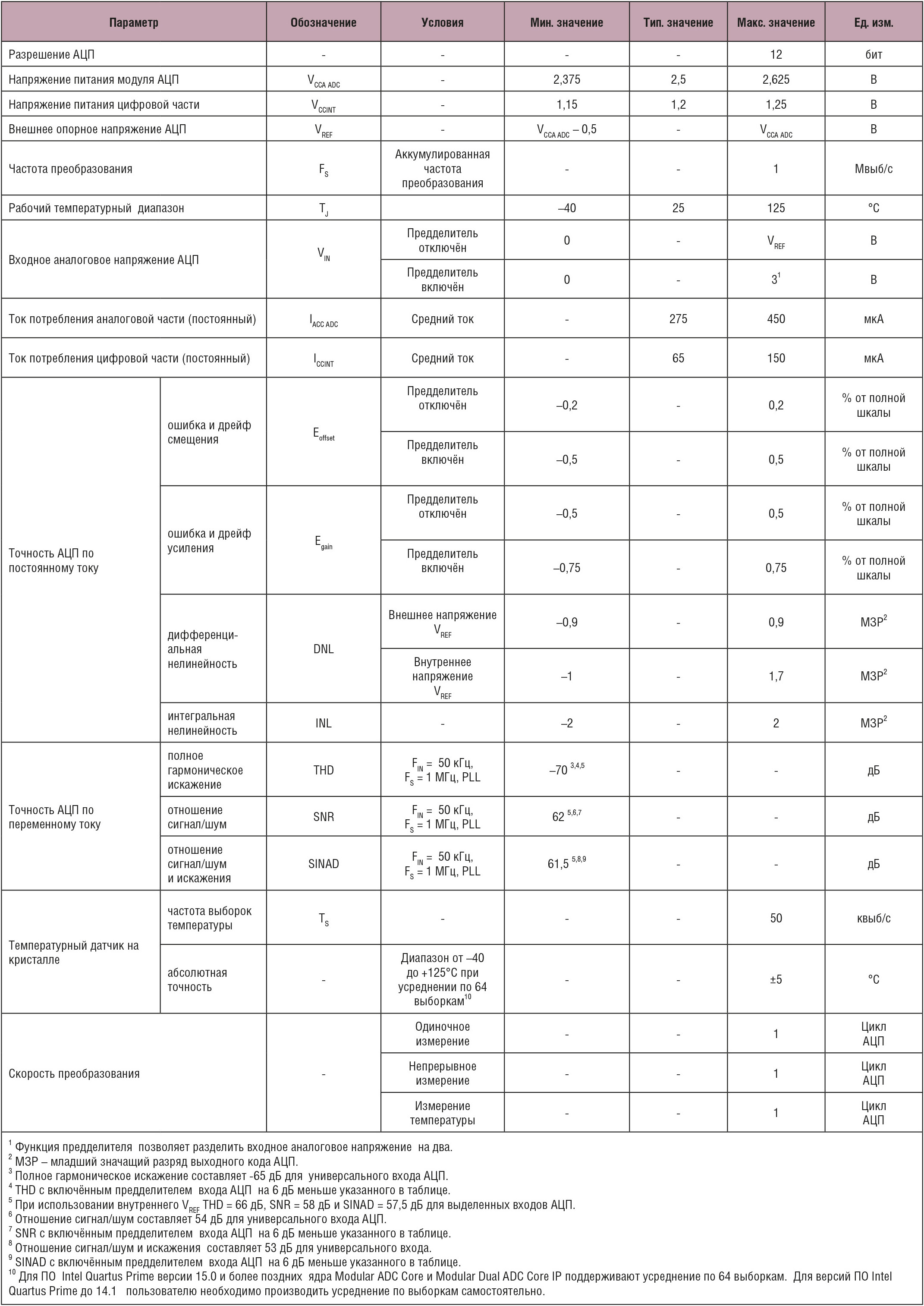

Параметры АЦП в ПЛИС

Параметры аппаратного модуля АЦП в конкретной ПЛИС зависят от её типа (Single Supply или Dual Supply). В таблице 2 приведены параметры аппаратного модуля АЦП в ПЛИС типа Single supply [2]. В таблице 3 приведены параметры аппаратного модуля АЦП в ПЛИС типа Dual supply [2].

Входы АЦП в ПЛИС

В качестве аналоговых входов аппаратных модулей АЦП в ПЛИС семейства MAX10 могут быть использованы либо выделенные выводы ПЛИС, имеющие единственную функцию аналогового входа (Dedicated), либо универсальные выводы ПЛИС, имеющие двойную функцию, – аналоговый вход или цифровой вход/выход GPIO (Dual Function). В таблице 4 содержатся сведения о количестве входов АЦП каждого из указанных типов для всех моделей ПЛИС, имеющих аппаратный модуль АЦП [1]. Как можно видеть из таблицы 4, максимальное количество доступных для использования в ПЛИС входов АЦП равно 18: 2 выделенных входа и 16 универсальных входов.

Помимо внешних входов АЦП, к входу модуля АЦП внутри ПЛИС может быть подключён встроенный диодный датчик температуры (TSD), для которого задан канал с номером 17. В случае если в качестве универсальных аналоговых входов в проекте ПЛИС используются линии GPIO из банка 1A, оставшиеся свободными линии GPIO в этом банке в качестве таковых использовать уже нельзя. Каждый аналоговый вход в аппаратном модуле АЦП ПЛИС имеет встроенную ячейку защиты от статического разряда (ESD).

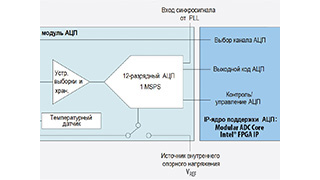

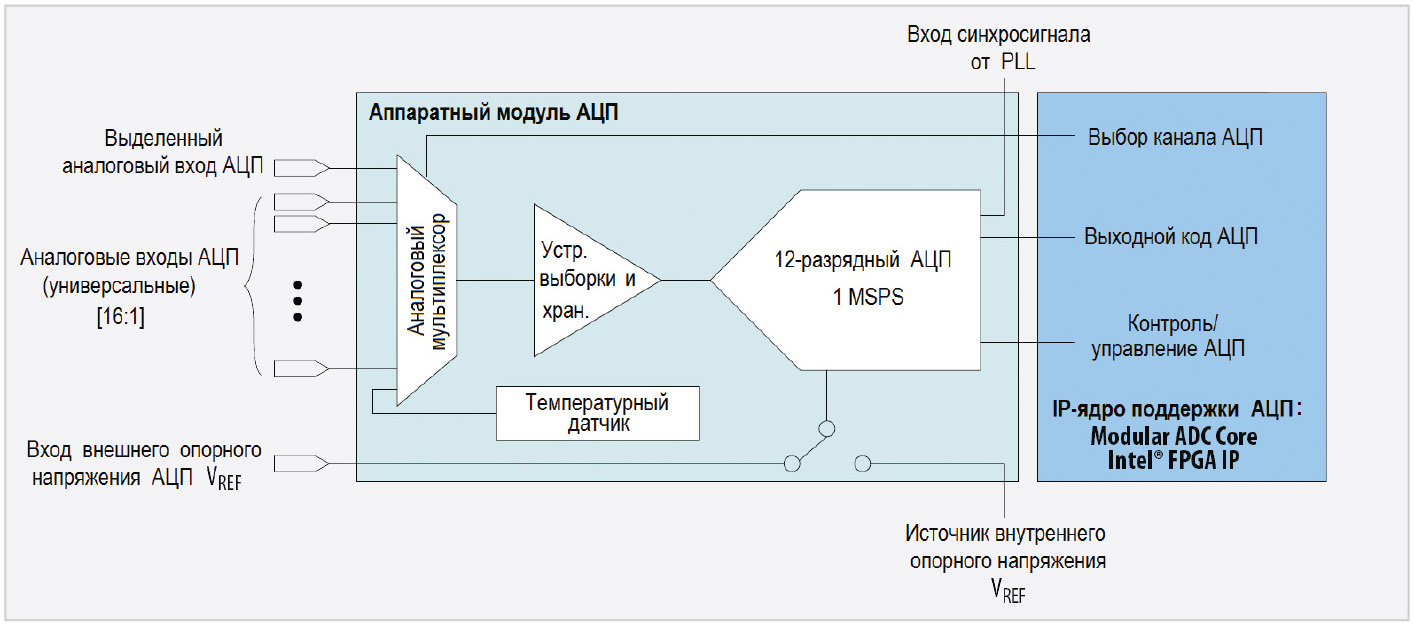

Блок-схема аппаратного модуля АЦП в ПЛИС семейства MAX10 показана на рисунке 1.

IP-ядра поддержки АЦП в ПЛИС

Как можно видеть из рисунка 1, для поддержки аппаратного модуля АЦП в проекте ПЛИС необходимо соответствующее IP-ядро. Производитель предоставляет разработчикам такое IP-ядро – Modular ADC Core Intel FPGA IP. Всего доступно два типа IP-ядер поддержки АЦП: с поддержкой одного аппаратного модуля АЦП (ядро Modular ADC Core IP core) и с поддержкой двух аппаратных модулей АЦП (ядро Modular Dual ADC Core IP core). Поддержка IP-ядром аппаратного модуля АЦП реализует три основные функции:

- обеспечение собственно преобразований, то есть конфигурирование АЦП, генерация сигналов выбора активного канала для преобразования управляющих сигналов для запуска и останова АЦП;

- так называемая программа упорядочения (sequencer) аппаратного модуля АЦП, позволяющая задать перечень активных каналов для преобразования, порядок их автоматического переключения, а также осуществлять простейшую обработку результатов АЦП, например сравнение их с порогом;

- поддержка интерфейсов автоматического сохранения результатов АЦП во внутренней или внешней памяти ПЛИС.

Каждое из IP-ядер поддержки аппаратного модуля АЦП может использоваться в конкретном проекте ПЛИС в нескольких различных конфигурациях. При использовании IP-ядра Modular ADC Core IP core модуль АЦП в ПЛИС в каждый момент времени может осуществлять аналого-цифровое преобразование сигнала только с одного выделенного или универсального аналогового входа. При использовании IP-ядра Modular Dual ADC Core IP core в ПЛИС с двумя аппаратными модулями АЦП, в каждый момент времени могут одновременно осуществляться аналого-цифровые преобразования сигнала от двух различных выделенных аналоговых входов. При этом производитель указывает, что задержка распространения сигнала для выделенных аналоговых входов будет одинаковой. Универсальные аналоговые входы для осуществления одновременных преобразований в двух аппаратных модулях АЦП одной ПЛИС производитель использовать не рекомендует, поскольку для этих входов одинаковая задержка распространения не гарантируется.

IP-ядро Modular ADC Core Intel FPGA IP обоих типов поддерживает следующие возможности по конфигурированию и управлению аппаратным модулем АЦП в ПЛИС:

- задание синхросигнала для АЦП, скорости преобразования, источника и значения опорного напряжения АЦП;

- задание активных каналов для АЦП, то есть таких, для которых в принципе разрешено преобразование путём наложения маски;

- задание порогового значения выходного кода АЦП, при достижении которого генерируется некий сигнал уведомления;

- настройка конверсионной последовательности, задающей очерёдность и частоту выбора для преобразования сигналов со входов активных (незамаскированных) каналов.

IP-ядро Modular ADC Core Intel FPGA IP обоих типов поддерживает четыре различные конфигурации:

- стандартная программа упорядочения с сохранением выборок АЦП по шине Avalon-MM во внутренней памяти ПЛИС.

- стандартная программа упорядочения с сохранением выборок АЦП по шине Avalon-MM во внутренней памяти ПЛИС и с задаваемым порогом выходного кода АЦП, при достижении которого сверху или снизу генерируется сигнал уведомления;

- стандартная программа упорядочения с сохранением выборок АЦП во внешней памяти;

- только управление АЦП без сохранения выборок.

Конфигурация 1 применяется в системах сбора данных и рассчитана на взаимодействие АЦП в ПЛИС с внешним микропроцессором, который по сигналам генерируемых прерываний читает блоки накопленных данных (оцифрованных выборок АЦП) из внутренней памяти (RAM) ПЛИС.

Конфигурация 2 также применяется в системах сбора данных и отличается от конфигурации 1 только тем, что в ней поддерживается задание порогового значения выходного кода АЦП, при достижении которого сверху или снизу конфигурация 2 генерирует сигнал уведомления. Используя этот сигнал, внешний микропроцессор может осуществлять системный мониторинг значений выборок АЦП и соответствующим образом реагировать на выходы результатов преобразования за заданные пределы. При наличии двух аппаратных модулей АЦП они могут генерировать сигнал уведомления о достижении порогов независимо друг от друга.

Конфигурация 3 аналогична конфигурации 1 с той лишь разницей, что блоки накопленных данных (оцифрованных выборок АЦП) хранятся не во внутренней памяти ПЛИС, а во внешней памяти. При этом для взаимодействия с внешней памятью разработчик должен спроектировать собственную логику, например используя для этого цифровую часть ПЛИС.

В конфигурации 4 IP-ядро Modular ADC Core Intel FPGA IP реализует только функции управления аппаратным модулем АЦП без функций упорядочения и сохранения оцифрованных выборок АЦП. В этой конфигурации разработчику предоставляется полная свобода проектирования своей собственной программы упорядочения и способа управления обработкой результатов АЦП.

Для получения подробностей по использованию конфигураций 1–4 рекомендуется обратиться к документу [1]. В рамках этой статьи будет рассмотрено использование АЦП в ПЛИС только в конфигурации 4.

Параметры IP-ядра поддержки АЦП в ПЛИС

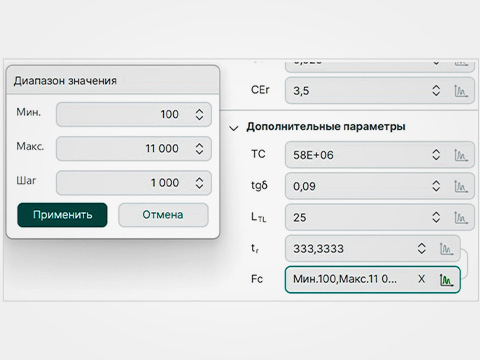

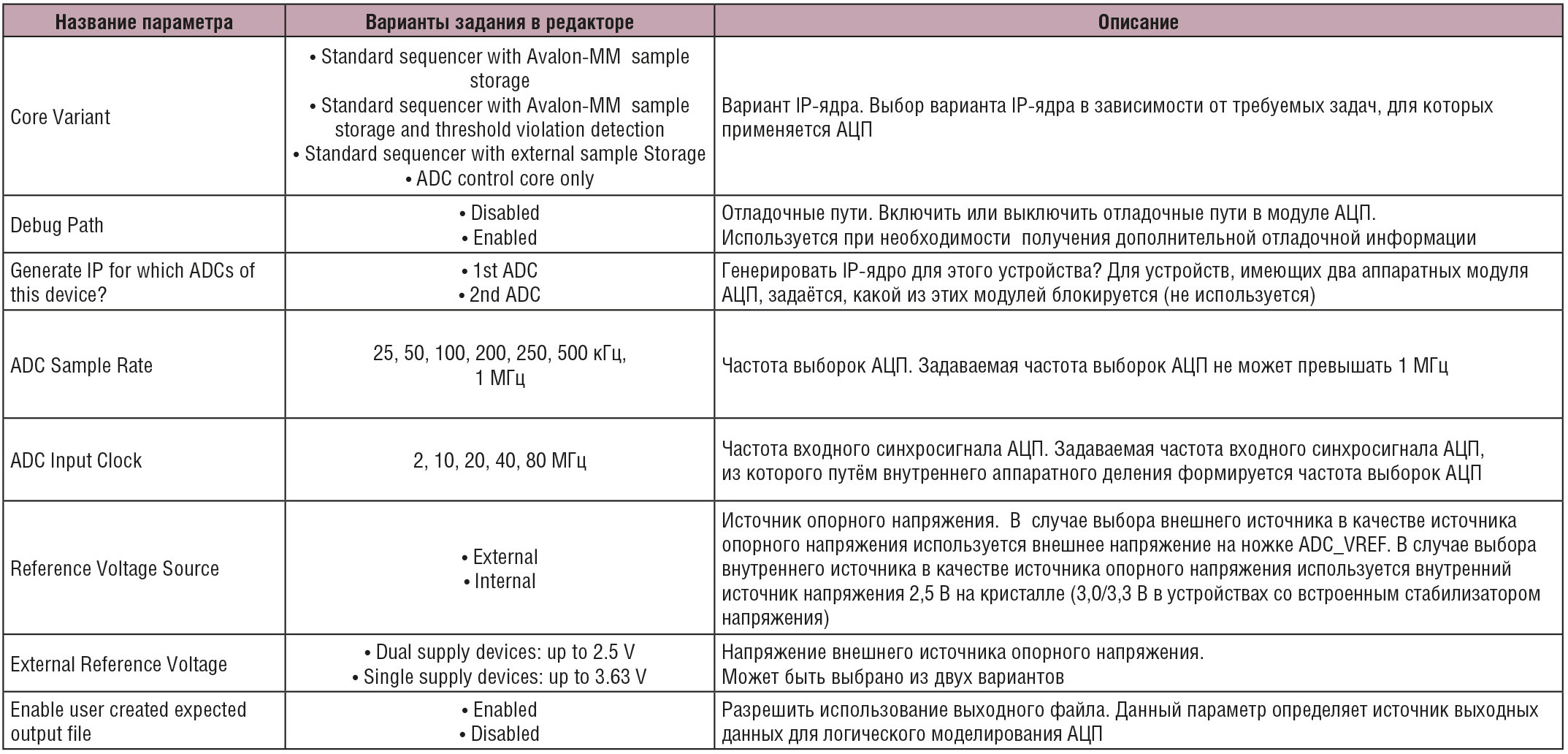

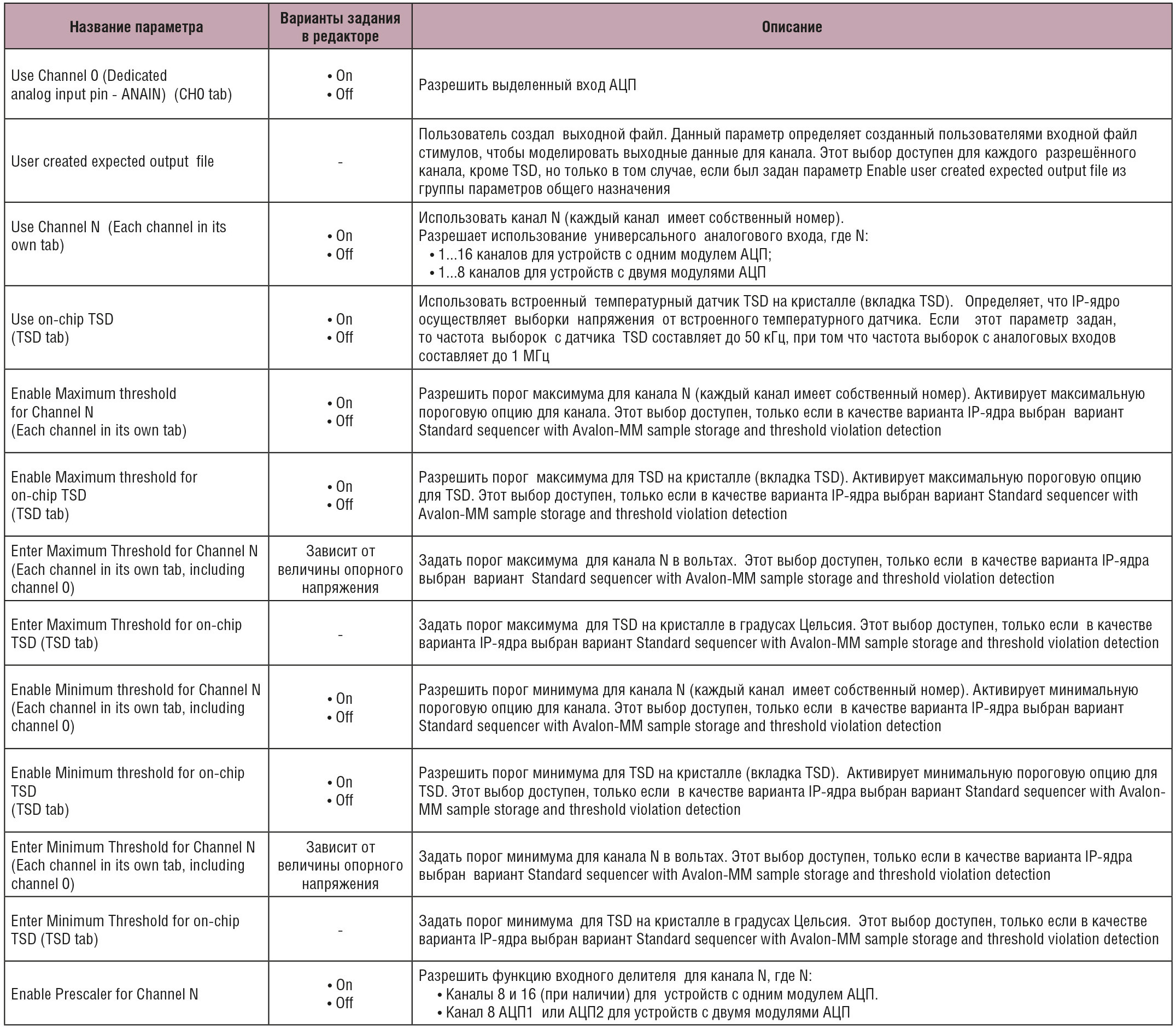

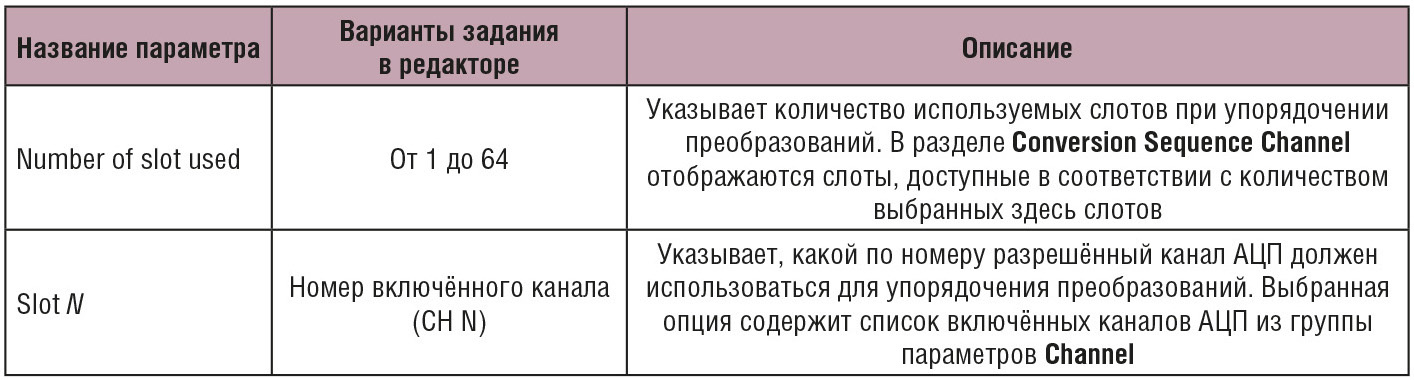

IP-ядра Modular ADC Core IP core и Modular Dual ADC Core IP core имеют ряд параметров, которые пользователь может задать в специальном редакторе параметров АЦП, поддерживаемом инструментальной средой разработки проектов ПЛИС Quartus II. Всего имеется три группы параметров: группа параметров общего назначения, группа параметров каналов АЦП, группа параметров упорядочения преобразования.

Параметры общего назначения IP-ядра Modular ADC Core IP core перечислены в таблице 5. Параметры каналов АЦП IP-ядра Modular ADC Core IP core перечислены в таблице 6. Параметры упорядочения IP-ядра Modular ADC Core IP core перечислены в таблице 7. Параметры IP-ядра Modular Dual ADC Core IP core имеют аналогичную структуру с поправкой на количество аппаратных модулей АЦП.

Подробнее о настройке АЦП и задании параметров IP-ядер в среде Quartus II будет рассказано во второй части статьи.

Синхронизация АЦП в ПЛИС

В качестве синхросигнала для аппаратного модуля АЦП в ПЛИС семейства MAX10 производителем рекомендуется использовать выходной сигнал встроенной в ПЛИС системы PLL (ФАПЧ). В зависимости от модели, ПЛИС семейства MAX10 содержат одну или две системы PLL: или только PLL1, или PLL1 и PLL3. В последнем случае для синхронизации АЦП можно использовать любую из имеющихся PLL. В случае использования ПЛИС с двумя аппаратными модулями АЦП и двумя PLL возможны следующие схемы синхронизации АЦП:

- оба модуля АЦП используют для синхронизации одну и ту же PLL;

- каждый модуль АЦП использует для синхронизации отдельную PLL.

В случае если каждый модуль использует свою PLL, программный инструмент монтажа проекта ПЛИС Intel Quartus Prime Fitter в ходе синтеза проекта ПЛИС автоматически выбирает один из двух вариантов. Если заданные разработчиком частоты выходных синхросигналов используемых PLL различны, Intel Quartus Prime Fitter оставляет выбранную разработчиком конфигурацию синхронизации АЦП неизменной (две PLL). Если же частоты выходных синхросигналов используемых PLL заданы одинаковыми, Intel Quartus Prime Fitter оставляет в качестве источника синхронизации обоих модулей АЦП одну PLL, а вторую высвобождает.

Опорное напряжение АЦП в ПЛИС

В качестве опорного напряжения каждый аппаратный модуль АЦП в ПЛИС может независимо использовать как внутренний, так и внешний источники опорного напряжения. В моделях ПЛИС с двумя модулями АЦП один из этих модулей может использовать внутренний источник опорного напряжения, а другой – внешний.

Однако в каждой ПЛИС имеется только один вход для подачи внешнего опорного напряжения VREF, поэтому при выборе в качестве опорных напряжений внешних источников для обоих модулей АЦП в ПЛИС на них поступит одно и то же напряжение с вывода VREF.

Встроенный температурный датчик в ПЛИС

В составе всех аппаратных модулей АЦП имеется внутренний диодный датчик температуры (TSD), сигнал с которого поступает внутри АЦП на вход отдельного канала. При выборе в качестве активного входа канала с датчиком температуры частота преобразования АЦП автоматически становится равной 50 квыб/с. При переключении на другой вход частота преобразования АЦП автоматически возвращается к значению 1 Мвыб/с или менее, если задано.

При оцифровке сигнала с датчика температуры аппаратный модуль АЦП автоматически производит усреднение напряжения с датчика по 64 выборкам. При этом используется метод бегущего среднего. Это означает, что первый результат усреднения вычисляется по истечении 64 выборок и усредняются выборки с 1-й по 64-ю, второй – по усреднению выборок со 2-й по 65-ю, третий – по усреднению выборок с 3-й по 66-ю и т.д. Таким образом, любой результат усреднения, кроме первого, выдаётся с выхода АЦП при каждой выборке.

Для вычисления текущей температуры кристалла ПЛИС, в которой установлен температурный датчик TSD, используется таблица соответствия температуры выходному коду АЦП при оцифровке напряжения с датчика, приведённая в [1]. Согласно этой таблице, диапазон измеряемых температур датчика составляет от –40 до +125°C включительно. При этом температуре –40°C соответствует выходной код АЦП, равный 3798, температуре +125°C – выходной код, равный 3431. Таким образом, области выходного кода размером (3798 – 3431) = 367 младших значащих разрядов (МЗР) соответствует интервал температур 165°C, то есть средняя чувствительность датчика с учётом оцифровки его выходного сигнала составляет 2,22 МЗР/°C. Заметим, что чувствительность датчика во всем диапазоне измеряемых температур неравномерная и на отдельных участках может ухудшаться вплоть до 1 МЗР/°C.

Режимы АЦП в ПЛИС

Аппаратный модуль АЦП в ПЛИС может функционировать в двух режимах.

Нормальный режим. Модуль АЦП осуществляет преобразование аналогового сигнала от одного выбранного аналогового входа с частотой преобразования до 1 Мвыб/с. В ПЛИС с одним аппаратным модулем АЦП всего доступно до 17 аналоговых входов: до 16 универсальных и один выделенный. В ПЛИС с двумя модулями АЦП в совокупности доступно до 18 аналоговых входов: по восемь универсальных и по одному выделенному в каждом аппаратном модуле АЦП.

Режим измерения температуры. Модуль АЦП осуществляет преобразование аналогового сигнала от внутреннего датчика температуры с частотой преобразования 50 квыб/с. В ПЛИС с двумя модулями АЦП данный режим поддерживается только первым модулем.

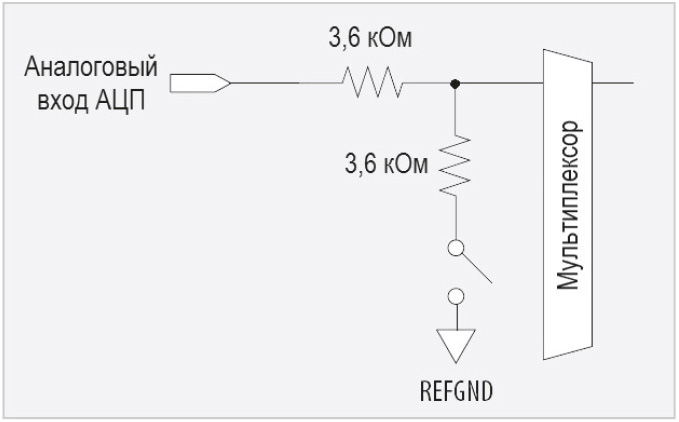

АЦП в ПЛИС типа Single Supply может оцифровывать входное напряжение в диапазоне от 0 до 3,0 В или до 3,3 В в зависимости от значения напряжения питания ПЛИС. АЦП в ПЛИС типа Dual Supply может оцифровывать входное напряжение в диапазоне от 0 до 2,5 В. В случае использования функции предделителя на аналоговом входе АЦП в ПЛИС типа Single Supply может оцифровывать входное напряжение до 3,6 В, а АЦП в ПЛИС типа Dual supply – до 3,0 В. Предделитель физически представляет собой резистивный делитель напряжения на входе аналогового мультиплексора АЦП, принципиальная схема которого показа на рисунке 2.

Включение или отключение встроенного предделителя на аналоговом входе АЦП может быть осуществлено при задании конфигурации модуля АЦП в инструментальной среде разработки проекта ПЛИС Quartus II, о чём будет подробнее рассказано ниже.

Предделителем снабжены не все аналоговые входы АЦП, а только один или два в зависимости от модели ПЛИС. В ПЛИС с одним аппаратным модулем АЦП это вход канала 8 или вход канала 16 (при наличии последнего). В ПЛИС с двумя аппаратными модулями АЦП это вход канала 8 первого или второго модуля АЦП, если для применения АЦП используется IP-ядро Modular ADC Core IP core. Если для применения АЦП используется IP-ядро Modular Dual ADC Core IP core, то предделителями оснащаются вход канала 8 первого модуля АЦП и вход канала 17 второго модуля АЦП.

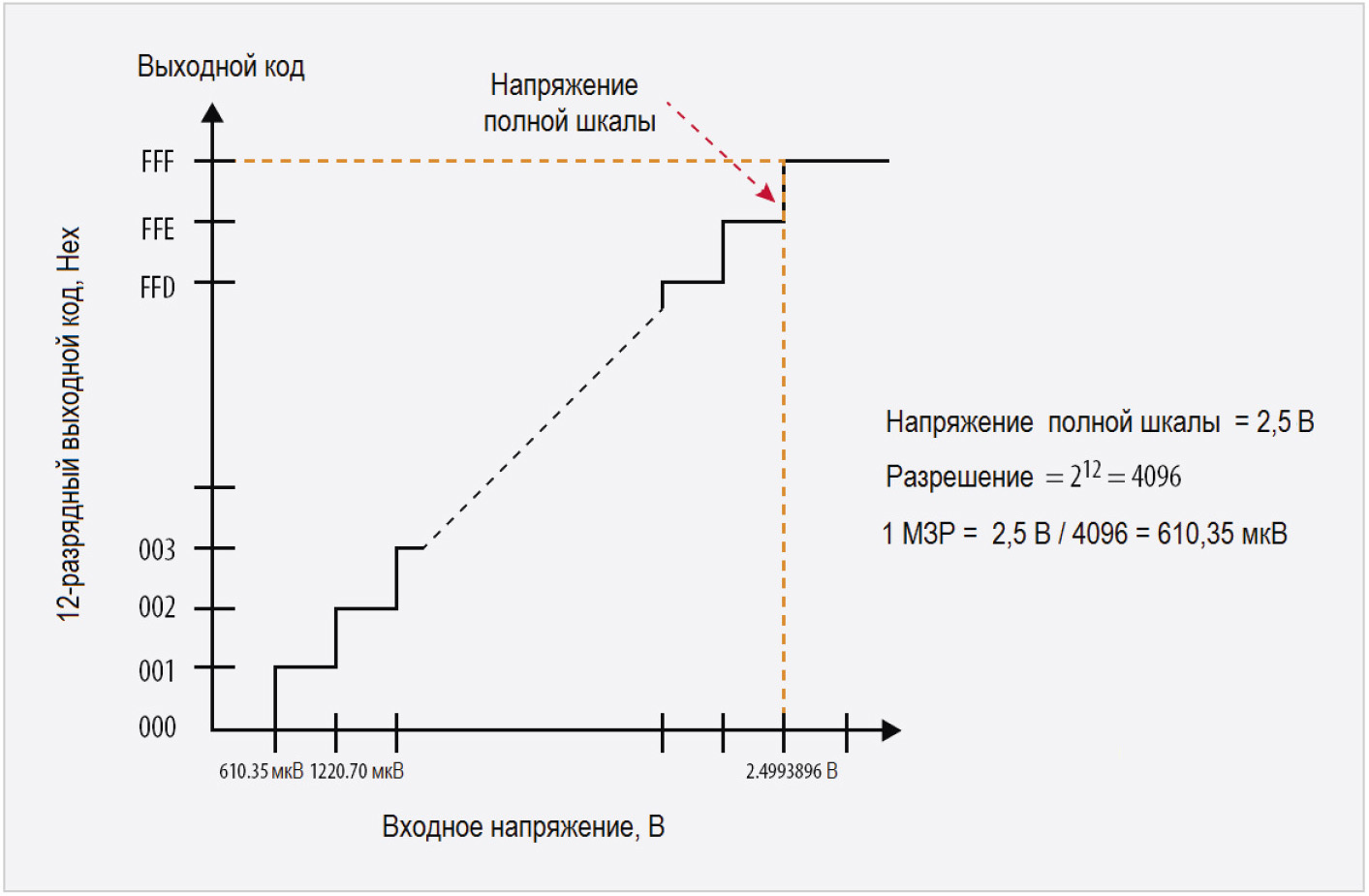

Выходной код АЦП во всех ПЛИС может принимать значения в диапазоне от 000h до FFFh. При формировании выходного кода в АЦП используется униполярное прямое двоичное кодирование согласно формуле:

Цифровой код = (VIN / VREF) × 212 (1)

где VIN – входное аналоговое напряжение, VREF – опорное напряжение АЦП.

Соответствие значений выходного кода АЦП и входного аналогового напряжения показано на рисунке 3. Как можно видеть из рисунка, максимальное разрешение (610,35 мкВ) АЦП обеспечивает при минимально возможном напряжении полной шкалы 2,5 В.

Значение входного напряжения может быть вычислено из выходного цифрового кода АЦП по формуле:

Входное напряжение = цифровой код × (VREF / 212)

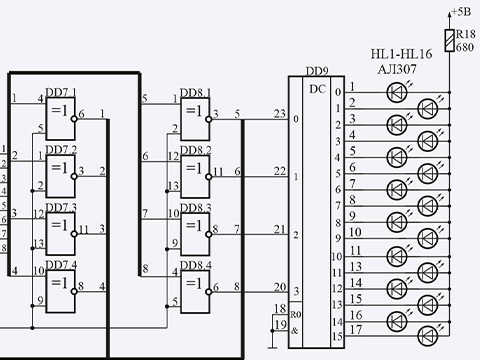

Временные диаграммы работы АЦП

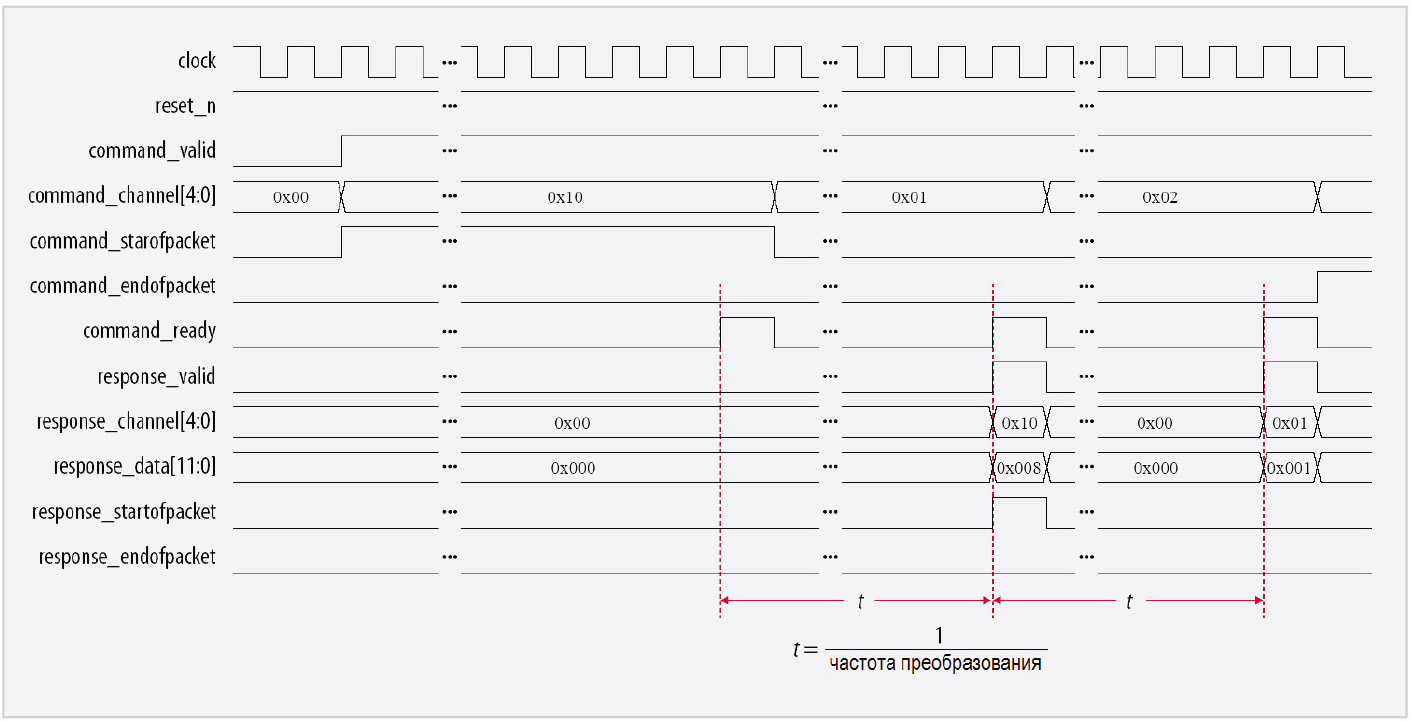

На рисунке 4 показаны временные диаграммы работы модуля АЦП в ПЛИС.

Названия сигналов, отображаемых на диаграммах, соответствуют их наименованиям, используемым производителем в IP-ядре Modular ADC Core IP core. Диаграммы иллюстрируют соответствия между сигналами глобальной синхронизации и сброса модуля АЦП (clock, reset_n), управляющими интерфейсными сигналами модуля АЦП (command_valid, command_startofpacket, command_endofpacket, command_channel[4:0]) и ответными интерфейсными сигналами модуля АЦП (response_valid, response_data[11:0]). Для случая, показанного на рисунке, осуществляется преобразование сначала в канале 16 (0x10), затем в канале 1, затем в канале 2. Номер канала для преобразования задаётся управляющим сигналом command_channel[4:0], запуск преобразования задаётся сигналом command_valid (активный уровень высокий). Готовность результата преобразования индицируется сигналом command_ready (активный перепад положительный), однако действительные данные в результате преобразования (выходном коде АЦП) имеют место только при наличии сигнала response_valid (активный уровень высокий).

Как можно видеть из диаграмм, для канала 16 результат преобразования равен 8, а для канала 1 он равен 1. Интервал преобразования t (величина, обратная частоте преобразования) равен периоду между передними фронтами импульсов сигнала готовности результата command_ready.

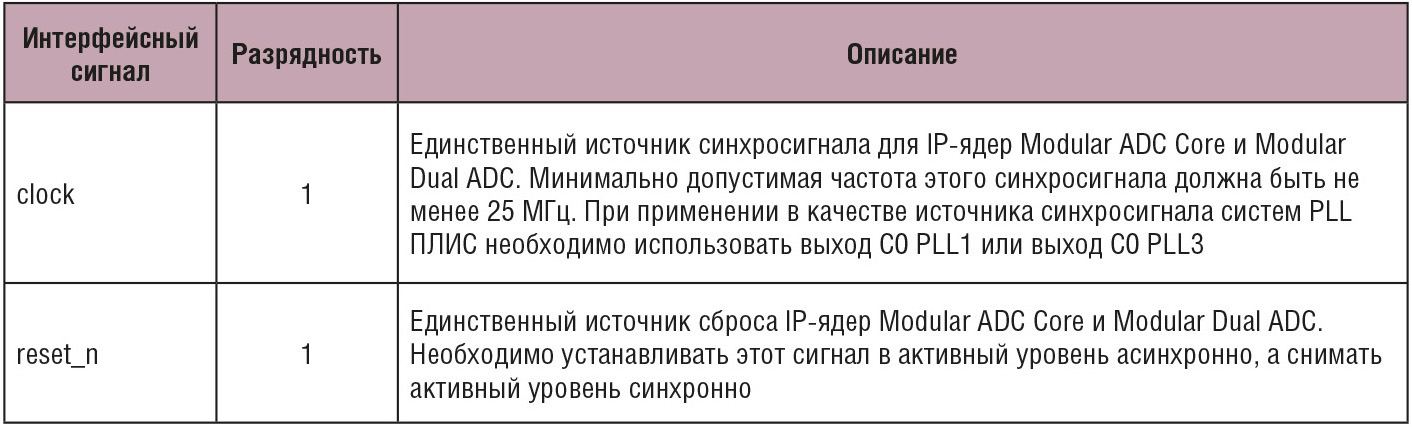

Описание сигналов глобальной синхронизации и сброса IP-ядер Modular ADC Core и Modular Dual ADC Core приведено в таблице 8.

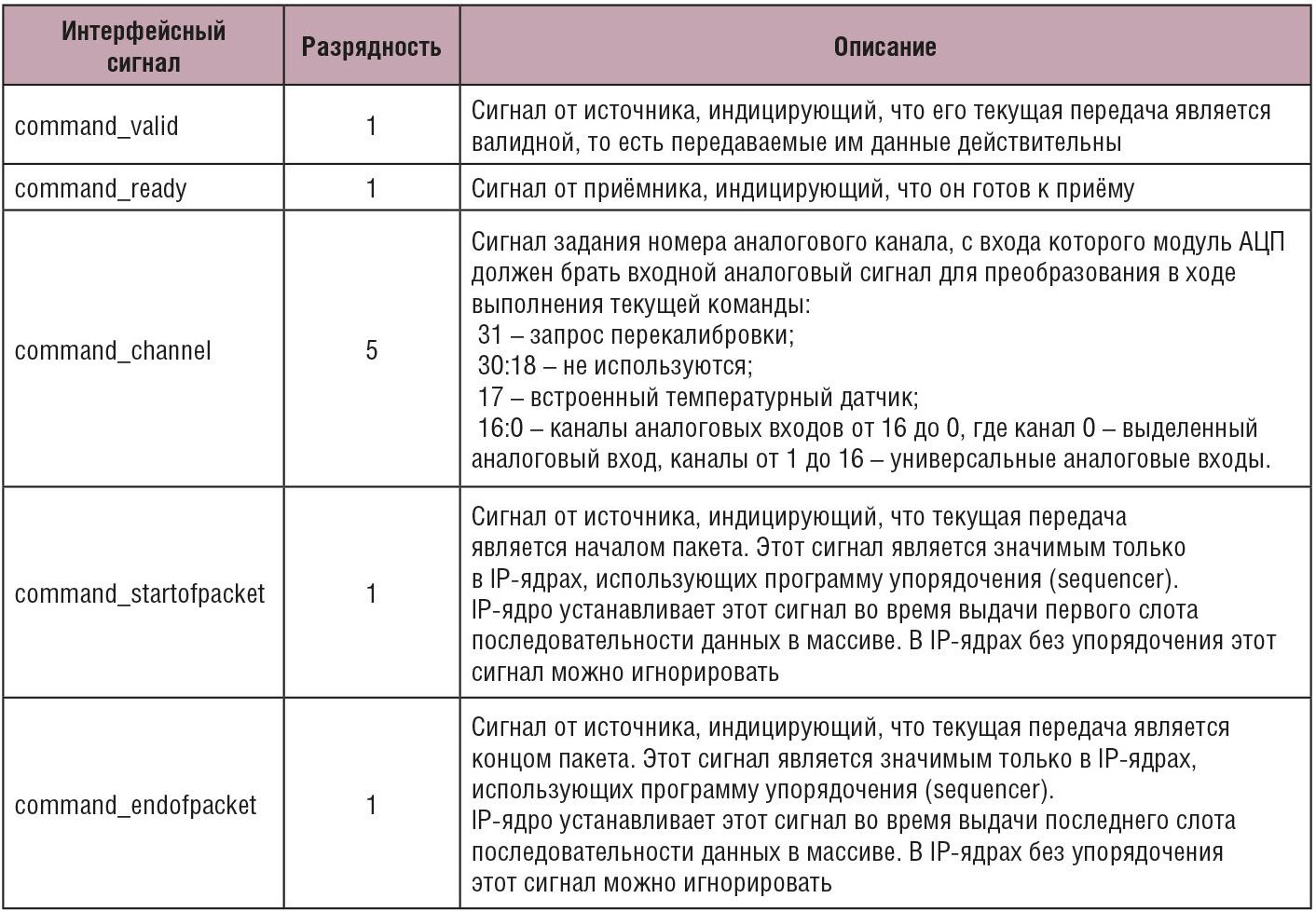

Описание интерфейсных управляющих сигналов IP-ядер Modular ADC Core и Modular Dual ADC Core приведено в таблице 9. Управляющие сигналы имеют префикс command.

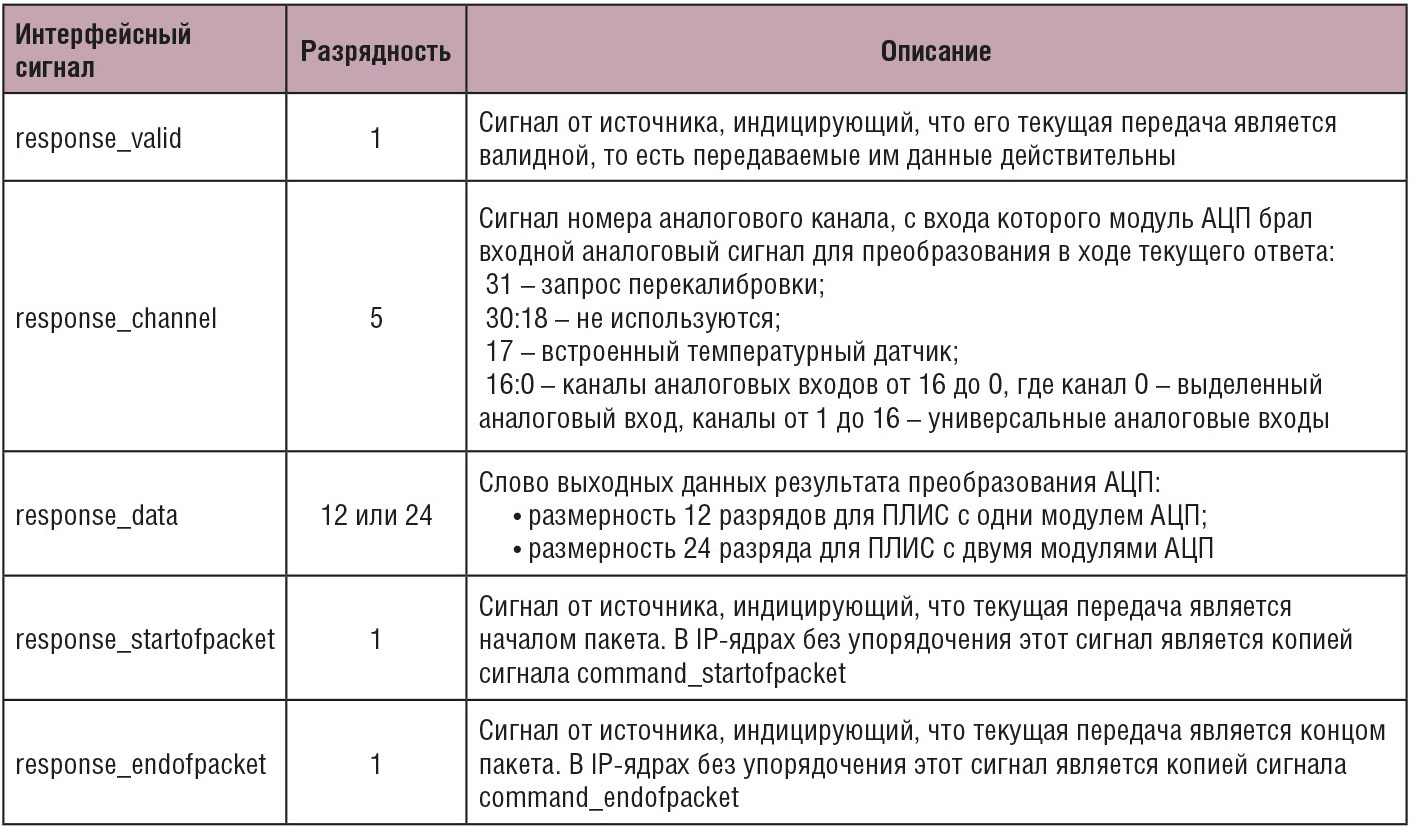

Описание интерфейсных сигналов ответа IP-ядер Modular ADC Core и Modular Dual ADC Core приведено в таблице 10. Сигналы ответа имеют префикс response.

Построение внешних цепей АЦП в ПЛИС

В документе [3] производитель даёт ряд рекомендаций по практическому проектированию внешних аналоговых цепей ПЛИС с модулем АЦП. В качестве общего провода при подаче на входы АЦП в ПЛИС опорного напряжения необходимо использовать вывод ПЛИС аналогового общего провода REFGND. Цепь REFGND в целевом устройстве должна быть выполнена проводником максимально возможной ширины и иметь сопротивление, не превышающее 1,0 Ом. Соединение цепи аналогового общего провода REFGND с цепью цифрового общего провода GND рекомендуется делать только в одной точке схемы и через ферритовую бусину.

Рекомендуется в целевом устройстве прокладывать проводники, подводящие к входам АЦП ПЛИС внешние аналоговые сигналы, таким образом, чтобы минимизировать их совместный параллельный пробег с цифровыми линиями GPIO, линиями питания и общего провода ПЛИС. Если последнее невозможно, то проводники питания и общего провода рекомендуется делать максимально широкими и с сопротивлением, не превышающим 1,5 Ом.

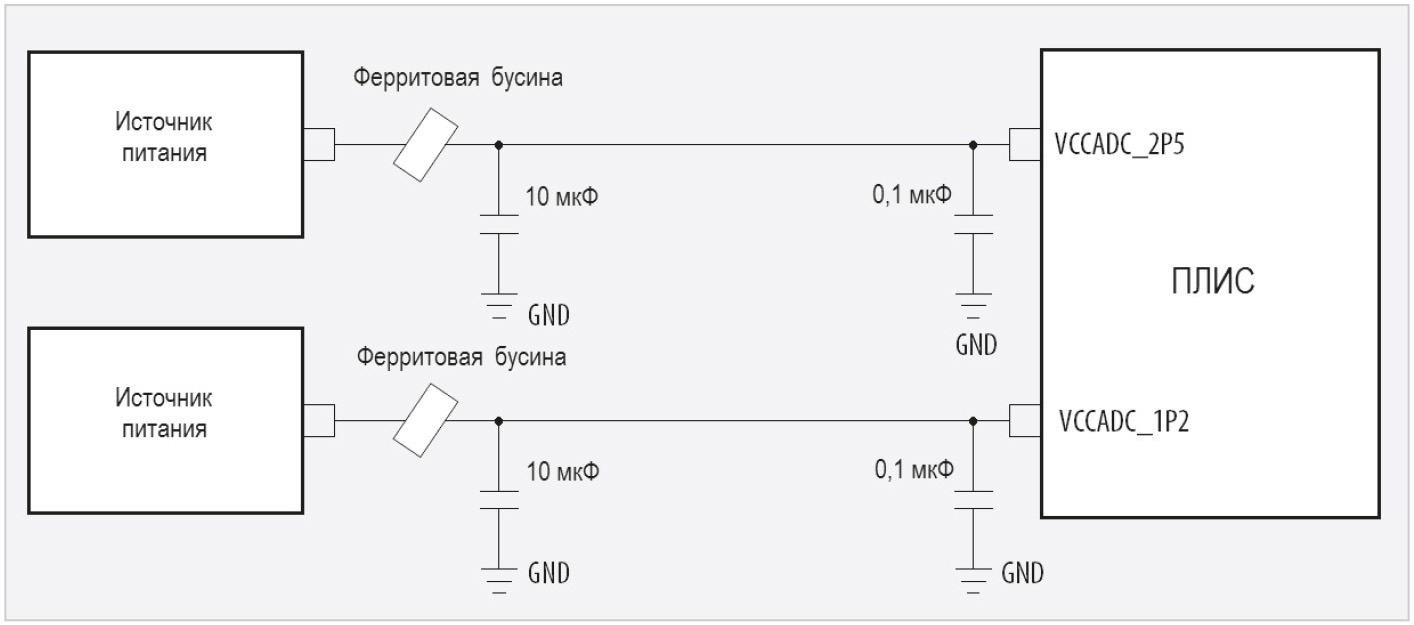

Цепи питания ПЛИС, используемые для модуля АЦП, рекомендуется выполнять по схеме, показанной на рисунке 5. При этом фильтрующие конденсаторы ёмкостью 0,1 мкФ должны располагаться как можно ближе к корпусу ПЛИС.

В качестве общего провода при подаче на входы АЦП в ПЛИС аналоговых сигналов также необходимо использовать вывод ПЛИС аналогового общего провода REFGND. При подаче на входы АЦП в ПЛИС внешних аналоговых сигналов необходимо учитывать электрические характеристики этих входов, прежде всего – их входной импеданс. Сумма паразитных ёмкостей корпуса ПЛИС, вывода ПЛИС, печатной платы, трассы аналогового сигнала внутри ПЛИС (аналогового мультиплексора) и входное сопротивление АЦП образуют RC-цепочку фильтра низких частот (ФНЧ) с постоянной времени, равной 42,4 нс. С учётом этого значения очевидно, что входной аналоговый сигнал АЦП полностью установится на входе преобразователя за время одной выборки, которое для максимальной частоты преобразования составляет 1 мкс. Чтобы избежать ошибок преобразования, связанных с рассогласованием сопротивлений источника аналогового сигнала и входа АЦП, производитель рекомендует минимизировать выходное сопротивление источника аналогового сигнала, которое без использования функции предделителя АЦП должно составлять не более 1 кОм, а с использованием функции предделителя – не более 11 Ом. Несоблюдение указанных рекомендаций может привести к ухудшению таких параметров АЦП, как THD, SINAD, DNL, INL (см. табл. 2, 3). Из сказанного следует, что напрямую подавать на аналоговые входы ПЛИС сигналы от источников с высоким выходным сопротивлением, например фотодиоды, фоторезисторы, не следует. Роль буферного элемента здесь могут выполнять внешние операционные усилители (ОУ).

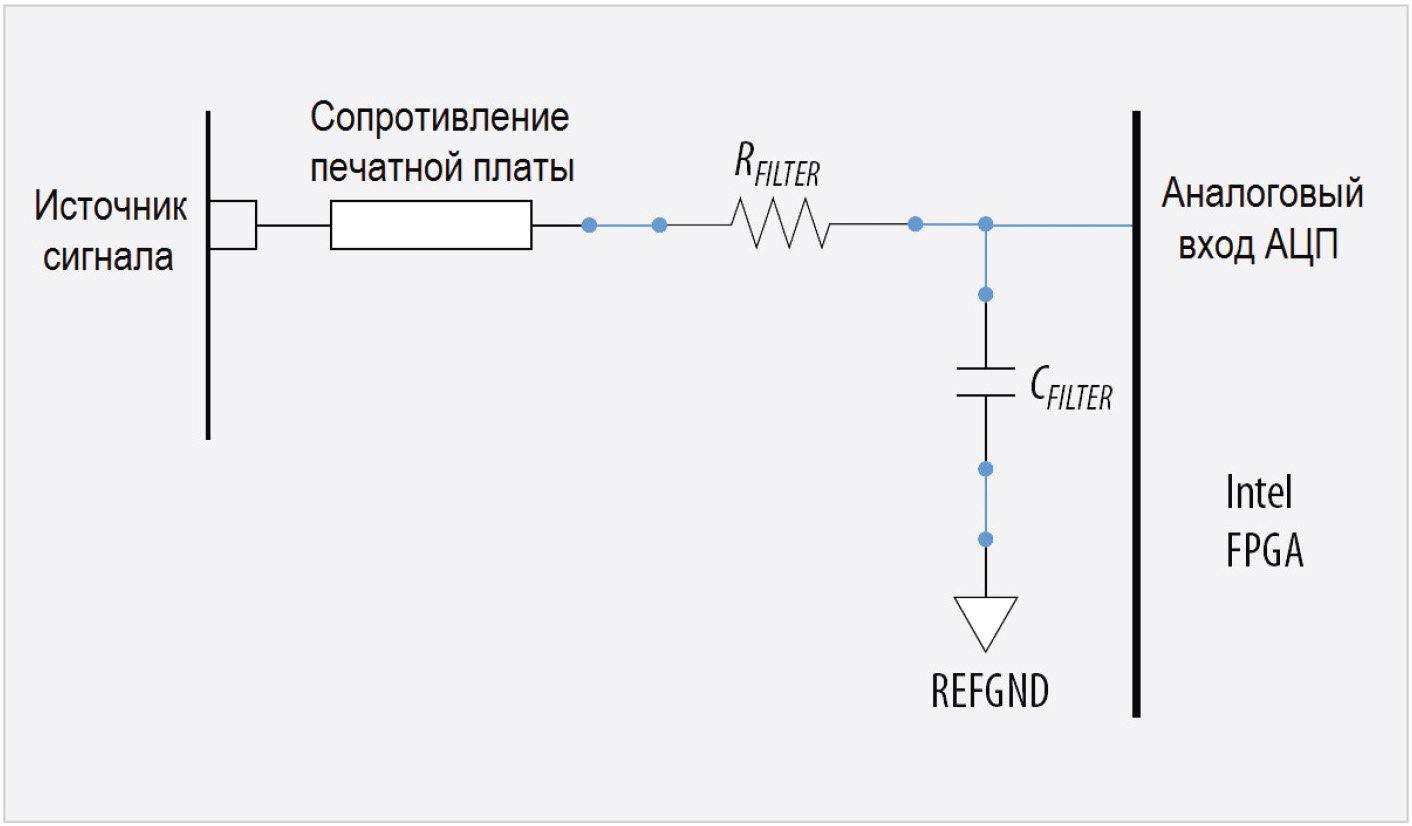

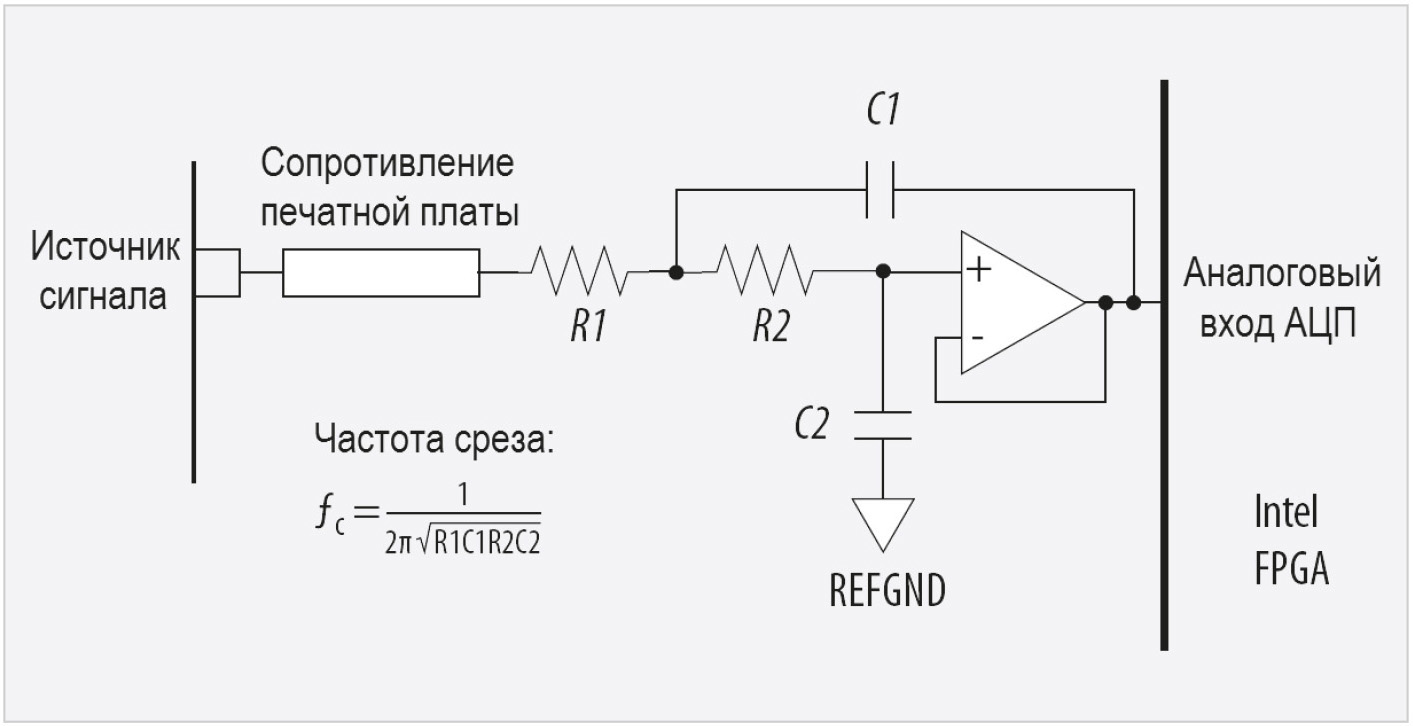

Производитель рекомендует устанавливать на аналоговых входах АЦП в ПЛИС внешние пассивные и активные (на базе ОУ) ФНЧ для подавления высокочастотных шумов во входных сигналах. При этом частоту среза ФНЧ рекомендуется выбирать не менее чем в 2 раза больше максимальной частоты входного сигнала. На рисунке 6 показана рекомендуемая схема внешнего пассивного ФНЧ на аналоговых входах АЦП в ПЛИС, а на рисунке 7 – активного ФНЧ на основе ОУ. Рекомендуемые значения сопротивления RFILTER и ёмкости CFILTER пассивного ФНЧ с учётом наличия всех перечисленных выше паразитных сопротивлений и ёмкостей для источника аналогового сигнала с выходным сопротивлением 5 Ом составляют соответственно 60 Ом и 550 пФ, а для источника сигнала с выходным сопротивлением 10 Ом составляют соответственно 50 Ом и 580 пФ. При этом конденсатор CFILTER рекомендуется размещать как можно ближе к выводу аналогового входа ПЛИС.

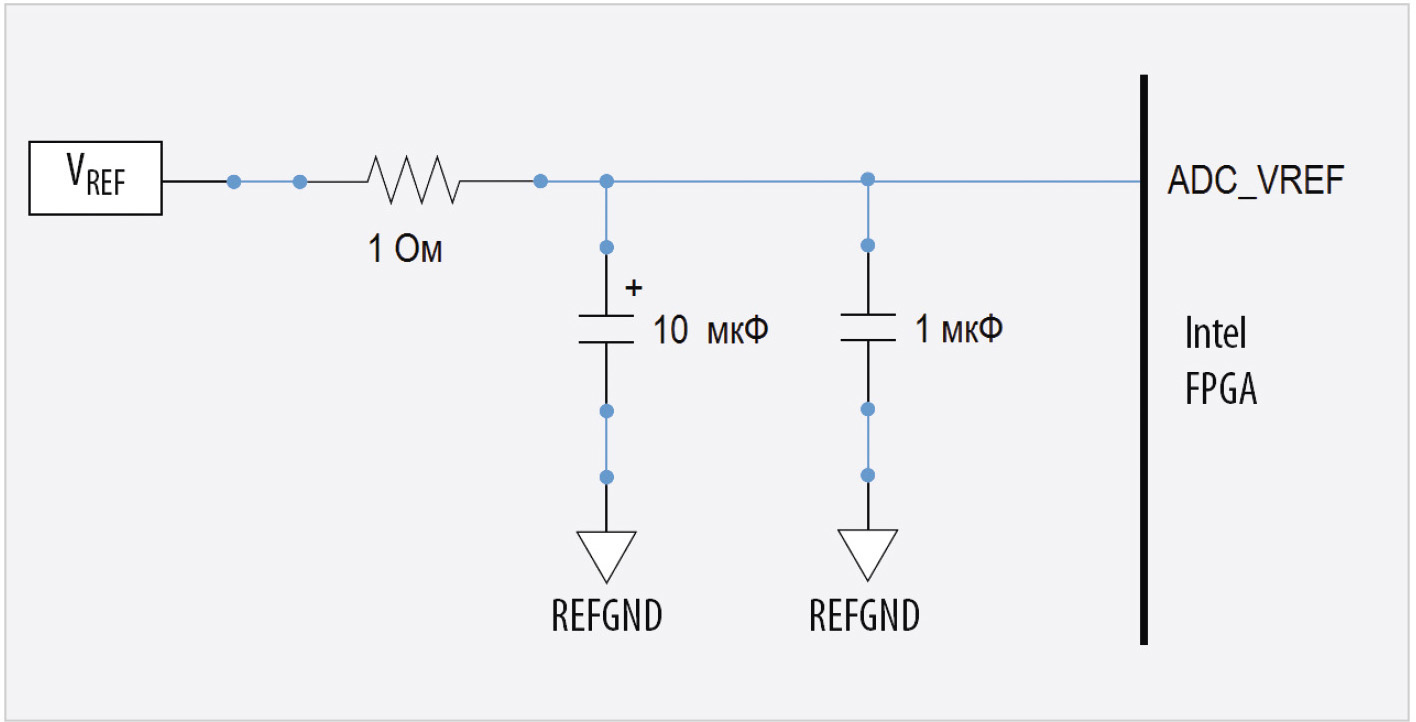

Цепь подачи внешнего опорного напряжения АЦП ПЛИС рекомендуется выполнять по схеме, показанной на рисунке 8. В цепи подачи внешнего опорного напряжения АЦП ПЛИС должно быть два фильтрующих конденсатора: полярный ёмкостью 10 мкФ, и неполярный (керамический) ёмкостью 1 мкФ. При этом неполярный фильтрующий конденсатор должен располагаться как можно ближе к корпусу ПЛИС.

Во второй части статьи будет рассмотрена работа с отладочной платой Altera MAX 10 FPGA в инструментальной среде Quartus II.

Литература

- Intel® MAX® 10 Analog to Digital Converter User Guide. Updated for Intel® Quartus® Prime Design Suite: 19.1/ UG-M10ADC | 2020.03.17. https://www.intel.com/content/ dam/www/programmable/us/en/pdfs/literature/hb/max-10/ug_m10_adc.pdf.

- Intel® MAX® 10 FPGA Device Datasheet. M10-DATASHEET | 2018.06.29. https://ru.mouser.com/datasheet/2/612/m10_datasheet-1115242.pdf.

- Intel® MAX® 10 FPGA Device Overview. M10-OVERVIEW | 2017.12.15. https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/max-10/m10_overview.pdf.

Скачать

Если вам понравился материал, кликните значок - вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал - не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!