Процессор с потоковой обработкой функции БПФ

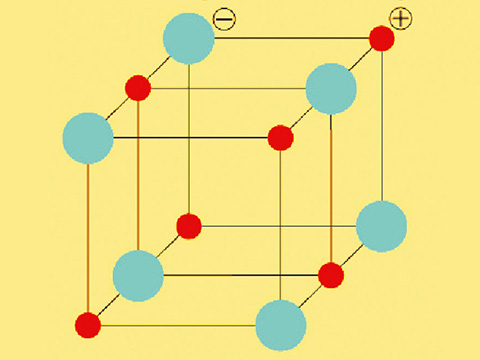

3D М ФЭ СБИС ПФ – матрица процессоров с потоковой обработкой функции расщеплённого алгоритма БПФ предназначена для вычисления БПФ с фильтром конечных импульсных характеристик и моделирования. Она входит в состав модуля 3D М ФЭФ М ПФ. Данный кристалл изготавливается по 180 нм КМОП-технологии SOI фирмы XFAB (технология XT018), аналогично 3D М ФЭ СБИС А/Ц [1].

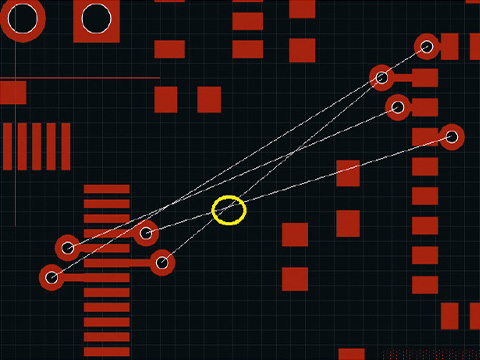

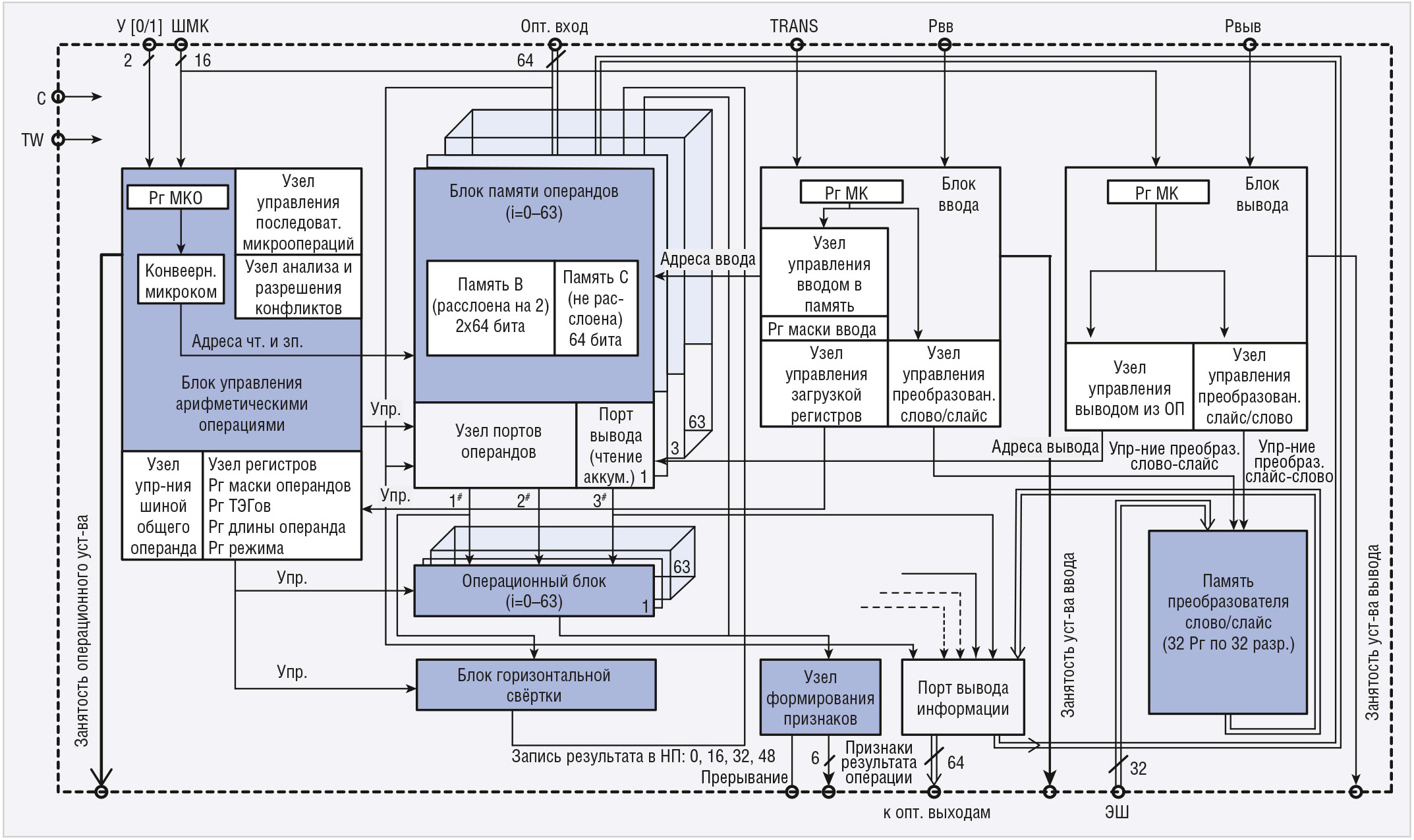

На рисунке 32 изображена блок-схема кристалла функции расщеплённого алгоритма 3D М ФЭ СБИС ПФ.

В состав кристалла 3D М ФЭ СБИС ПФ входят:

- матрица из 64 8/16/32-битных пикселей процессоров цифровой обработки сигналов (ЦОС) с последовательным оптическим входом и выходом;

- контроллер 64-разрядной шины EMIFA для связи со скалярным процессором, например, TMS320C6455;

- контроллер внешней памяти и межпиксельный коммутатор.

Управление, синхронизация, загрузка программ, данных и коэффициентов в 3D М ФЭ СБИС ПФ осуществляются как по 64-разрядной шине EMIFA, так и по нескольким выделенным каналам волоконно-оптических линий связи. Сам кристалл СБИС ПФ обладает универсальной системой команд, позволяющей реализовывать любые вычислительные алгоритмы, но наибольшая производительность достигается за счёт алгоритмов ЦОС.

Основные блоки 3D М ФЭ СБИС ПФ

Память данных SRAMX

Память данных SRAMX состоит из двух одинаковых независимых блоков, которые можно переключать (менять местами) в любой момент времени. Пока в один блок пишутся исходные данные и одновременно считываются результаты, другой блок используется для вычислений. Потом блоки меняются местами и т.д.

Каждый блок состоит из 16 одинаковых двухпортовых 8-разрядных 512-словных банков ОЗУ. Этого достаточно для выполнения 32-битного БПФ на 1024 отсчёта или 16-битного на 2048 отсчётов.

Считывание из блока SRAMX может производиться как одновременно из 16 банков с общим адресом (в режиме NEURO), так и поочерёдно из разных банков со сквозной адресацией (в режиме FFT). В режиме NEURO, таким образом, достигается наибольшая скорость чтения исходных данных, при которой возможна непрерывная загрузка всех умножителей и сумматоров. В режиме FFT необходима более сложная адресация и меньшая скорость получения данных, что обеспечивается сквозной адресацией. Запись результатов (промежуточных и конечных) в любом режиме производится поочерёдно в разные банки SRAMX в режиме сквозной адресации. Запись и чтение одного и того же банка могут выполняться одновременно.

Устройство блока FFT4

Блок FFT4 содержит четыре блока FIR/FFT, которые состоят из 4 блоков регистров/умножителей MULT сумматоров/вычитателей.

MULT производит умножение 8 пар 8-битных слов за 8 тактов, либо 4 пар 16-битных слов за 16 тактов, либо 2 пар 32-битных слов за 32 такта. Сумматоры/вычитатели построены аналогично – могут работать с соответствующим количеством 8, 16 и 32-битных слов. Таким образом, блок FIR/FFT производит базовую операцию умножения с аккумулированием (и вычитание при необходимости), которая используется для вычисления БПФ, КИХ-фильтрации и при моделировании нейронных сетей.

Все блоки MULT в пикселе соединены таким образом (несмотря на иерархию блоков), что при вычислении КИХ-фильтра данные побитно сдвигаются от оптического входа. По мере поступления с оптического входа входных отсчётов эти отсчёты сдвигаются вглубь по цепочке умножителей, то есть блоки MULT совмещают в себе функции как умножения, так и задержки, необходимой при вычислении КИХ-фильтра.

При суммировании результатов работы блоков FIR/FFT поочерёдно (каждый такт) открываются ключи TRIF0 – TRIF7 и на сумматоре SUMF происходит накопление суммы.

Блок управляющих регистров

Система управления пикселом состоит из машины состояний, выполняющей микрокоманды, и регистров (фактически, реализован микроконтроллер общего назначения).

Во время действия сигнала остановки машины возможна загрузка микропрограмм. По окончании сигнала остановки все машины состояний переходят на исполнение по адресу 0. Сигнал остановки формируется управляющими командами по шине EMIFA или по оптическому тракту, загрузка микрокода предполагается возможной по этим же каналам.

Все микрокоманды выполняются за один такт. Это необходимо для возможности генерации потактовой последовательности сигналов управления для вычислительного поля.

Для записи управляющих регистров существует отдельная машина состояний, исполняющая свой микрокод.

Каждый управляющий регистр имеет соответствующий теневой регистр. Запись управляющего регистра осуществляется в два этапа.

Последовательность микрокоманд производит запись в один, несколько или все теневые регистры.

Одна микрокоманда производит одновременную запись содержимого теневых регистров в соответствующие управляющие регистры. Возможна запись не всех сразу регистров управления, а поблочная. Например, возможно записать регистры группы RegXADDR_AOUTx при этом не изменяя содержимое остальных.

Система управления пикселом

При каскадировании нескольких пикселей в пределах одной СБИС возможно вычисление БПФ до 8192 точек в темпе поступления входных данных.

Производительность одного пикселя при тактовой частоте 640 МГц составляет:

- БПФ 8 бит 1024 комплексных отсчёта выполняется за 26 мкс.

Суммарная производительность 3D М ФЭ СБИС ПФ при тактовой частоте 640 МГц составляет:

- более 5,5 млн 8-битных комплексных БПФ на 1024 отсчёта в секунду;

- более 1,28 трлн связей в секунду при моделировании нейросетей.

Таким образом, при передаче данных по многоканальным оптическим и локальным электрическим каналам связи единичный пиксель 3D М ФЭ СБИС ПФ выполняет следующие функции:

- Реализует разнообразные алгоритмы цифровой обработки сигналов, содержащих операции сложения, вычитания, умножения, сдвигов, логические операции.

- Реализует вычисления прямого и обратного БПФ до 1024 точек с разрядностью – 8, 16 и 32 бита соответственно модификации.

- Производит моделирование нейронных сетей. Так базовая нейрооперация умножения с аккумулированием и вычислением нелинейной функции активации вычисляется с разрядностью – 8, 16 и 32 бита соответствующей модификации.

- Реализует вычисление фильтра конечных импульсных характеристик (КИХ): 8 бит – 128 отсчётов, 16 бит – 64 отсчёта, 32 бита – 32 отсчёта. Также реализована возможность каскадирования нескольких пикселей для увеличения числа отсчётов КИХ-фильтра.

- Присутствует квадратурная модуляция 8-, 16- или 32-битного входного сигнала.

- Выполняет обработку выходных данных других пикселей и производит цифровой синтез сигналов.

Матрица пикселей памяти с функцией перестановки – 3D М ФЭ СБИС ПП

Кристалл матрицы пикселей памяти с функцией перестановки – 3D М ФЭ СБИС ПП изготавливается аналогично кристаллам 3D М ФЭ СБИС А/Ц и 3D М ФЭ СБИС ПФ – по 180 нм КМОП-технологии SOI фирмы XFAB (технология XT018). Кристалл 3D М ФЭ СБИС ПП при передаче данных по многоканальным оптическим и локальным электрическим каналам связи выполняет следующие операции:

- запись, хранение и выдача слайсов и слов информации из внутренней памяти;

- выполнение операций клеточной логики по двум различным шаблонам над слайсом памяти, представленным в виде матрицы 8 ´ 8;

- выполнение ряда логических операций над слайсами памяти;

- копирование слайса памяти из одного адреса в другой;

- транзит слайсов;

- выполнение операций перестановки слов информации путём копирования из ячейки с одним адресом в ячейку с другим адресом;

- маскируемое копирование слов памяти, предназначенное для реализации команды сборка/разборка по маске;

- генерация нулевого или единого слайса.

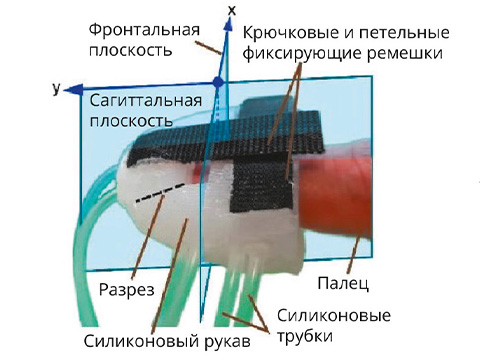

Кристалл 3D М ФЭ СБИС ПП предназначен для использования в составе модуля 3D М ФЭФ М ПП. Управление кристаллом 3D М ФЭ СБИС ПП производится посредством микрокоманд, передающихся по шине EMIFA микропроцессором, например, TMS320C6455. Одна микрокоманда в 3D М ФЭ СБИС ПП может совмещать в себе выполнение нескольких микроопераций, однако не все микрооперации совместимы. Сама матрица пикселей памяти с функцией перестановки имеет следующие порты:

- «word_in» – электрическая шина данных для байтового/словного доступа, 32 бита, возможна работа с данными 32, 24, 16 или 8 бит;

- «slice_in» – оптический слайсовый вход, 64 бита;

- «slice_out» – оптический слайсовый выход, 64 бита;

- «command» – вход управляющей микрокоманды;

- «clk» – тактовый вход;

- «reset» – сброс.

Интегральная микросхема (ИМС) матрицы пикселей памяти состоит из следующих частей:

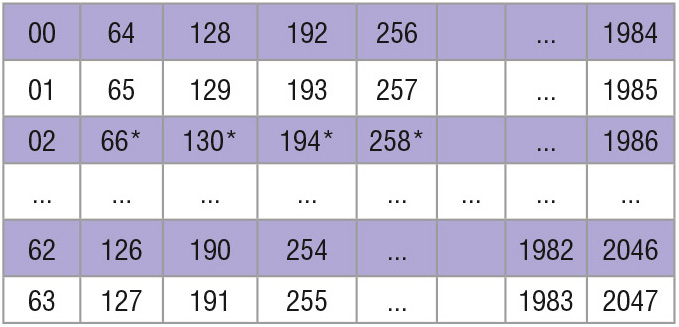

1. Двухпортовая память со слайсовым и словным доступом.

Размер слайса – «SLICE_SIZE». Слайс представляет собой квадратную матрицу со стороной «SLICE_SIDE_SIZE». Максимальный размер слова – «WORD_SIZE». Допускается обращение к памяти с размером слова, кратным 8 битам и меньше либо равным «WORD_SIZE». Внутри память организована в виде банков (количество – «BANKS_NUMBER»), число байт в банке равно размеру слайса, число слайсов равно 8 (размер байта). Слово с размером больше одного байта состоит из байтов из смежных банков, взятых по одинаковому адресу. Адресом слова является адрес его младшего байта. В таблице 5 приведён пример организации памяти для размера слайса 64, слово 32, число банков 32 (в ячейках указаны адреса).

2. Блок байтовой фильтрации состоит из массива одинаковых логических схем, каждая из которых подключается к соответствующим битам регистров слайсовых операндов.

Эти схемы образуют двумерную матрицу. Выход блока через мультиплексор подключён к внутренней шине ИМС.

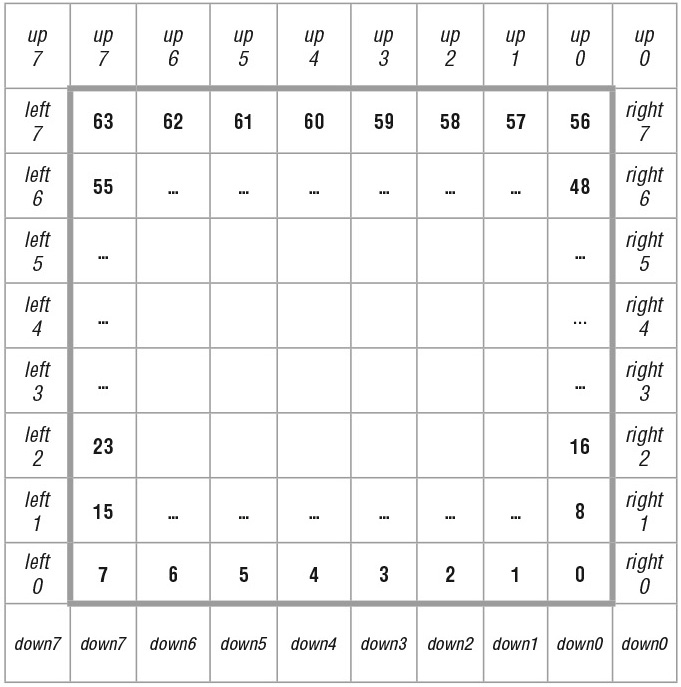

Организация слайса представлена в таблице 6.

Крупным жирным шрифтом показаны номера битов, относящиеся к слайсу. Курсивом – биты регистров расширения слайса.

Направления координатных осей для нормального шаблона – ось X – слева направо, ось Y – снизу вверх. Для диагонального шаблона – ось X – слева сверху направо вниз, ось Y – слева снизу направо вверх.

Блок байтовой фильтрации может выполнять следующие операции:

- «SHIFTXP» – сдвиг по направлению оси X;

- «SHIFTXM» – сдвиг по отрицательному направлению оси X;

- «SHIFTYP» – сдвиг по направлению оси Y;

- «SHIFTYM» – сдвиг по отрицательному направлению оси Y;

- «EDGE» – выделение контура: элемент устанавливается в 1, если он – 1 и хотя бы один из соседей – 0, иначе элемент сбрасывается в 0;

- «PROJY» – проекция на ось Y: элемент устанавливается в 1, если он – 1 или сосед по отрицательному направлению оси X = 1, иначе элемент сбрасывается в 0;

- «PROJX» – проекция на ось X: элемент устанавливается в 1, если он – 1 или сосед по отрицательному направлению оси Y = 1, иначе элемент сбрасывается в 0;

- «SHRINK» – сжатие: элемент устанавливается в 1, если он – 1 и (все соседи нулевые или два соседа на одной оси единичные, а два других – нулевые или все соседи – единичные), иначе элемент сбрасывается;

- «EXPAND» – расширение: элемент сбрасывается в 0, если он – 0 и (все соседи нулевые или два соседа на одной оси единичные, а два других – нулевые или все соседи – единичные), иначе элемент устанавливается в 1;

- «INV» – инверсия: элемент устанавливается в 1, если он – 0, элемент сбрасывается в 0, если он – 1;

- «SMOOTH» – сглаживание: элемент устанавливается в 1, если он – 1 и хотя бы два соседа единичные, иначе элемент сбрасывается в 0;

- логические операции над двумя операндами – «AND», «OR», «XOR» и «NXOR».

Схема управления включает в себя регистры операндов «ARGA», «ARGB», регистры расширения слайсов для байтовой фильтрации, регистр маски «VM», регистр входных данных «VD», а также автомат для выполнения операций сборки и разборки.

Кристалл нейропроцессоров – 3D М ФЭ СБИС НП

Кристалл нейропроцессоров с коммутацией каналов предназначен для работы в составе оптоэлектронного модуля 3D М ФЭ Ф НП. Аналогично предыдущим кристаллам он изготавливается по 180 нм КМОП-технологии SOI фирмы XFAB (технология XT018).

Кристалл 3D М ФЭ СБИС НП имеет 64 одноразрядных процессора для коммутации каналов (КК), каждый из которых имеет внутреннюю память. Такой кристалл 3D М ФЭ СБИС НП предназначен для одновременной послайсовой обработки 64 процессорами 64 пар исходных операндов (целочисленная арифметика) под управлением общей микрокоманды. Микрокоманда загружается из центрального устройства управления по разделяемой 16-разрядной шине микрокоманд за три такта (совмещено с выполнением предыдущей микрокоманды).

Архитектурные особенности 3D М ФЭ СБИС НП

Каждый нейропроцессор (НП) имеет внутреннюю память ёмкостью 24 байта, в которую загружаются операнды на границах своей длины. Длина операндов задаётся по специальной микрокоманде в загружающей 6-разрядной PrL (L – длина операнда) из внешней относительно СБИС НП памяти. L может принимать значения от 2 до 64 (L – чётное число).

Количество нейропроцессоров, участвующих в обработке, определяется содержимым регистра ТЭГов при соответствующей микрокоманде. Выбор вида операндов, участвующих в операции, определяется как микрокомандой, так и содержимым специального регистра арифметической маски (64 бита), для которых в СБИС имеются встроенные микроконтроллеры управления вводом и выводом.

Загрузка микрокоманд в эти микроконтроллеры производится за 1 такт по общей 16-разрядной шине микрокоманд (разделяемая с шиной арифметических микрокоманд). Введение в СБИС данных микроконтроллеров позволяет совмещать во времени операции ввода/вывода с текущей арифметической операцией. Соответственно, обработка ввода и вывода осуществляются послайсно. Количество слайсов ввода/вывода задаётся микрокомандой (частный случай – количество слайсов определяется регистром L). Ввод и вывод осуществляются как через оптические тракты ввода и вывода (каждый тракт – 64 разряда слайса), так и через общую электронную 4-байтную шину, связывающую БИС НП с внешней памятью (относительно СБИС НП). Через электронную шину ввод и вывод может производиться как послайсно, так и пословно.

В СБИС НП имеется встроенный буфер 32 слова по 32 разряда для преобразования вида вводимой/выводимой информации (слово/слайс). Ввод в буфер производится под управлением микрокоманды с учётом содержимого специального регистра маски ввода (64 разряда) или регистра арифметической маски. Регистры ТЭГов, арифметической маски, маски ввода могут загружаться специальными микрокомандами как из внутренних памятей нейропроцессоров, так и из внешней памяти через электронную шину. Под загрузкой из внутренних блоков памяти имеется в виду загрузка слайса.

В состав СБИС НП введена общая разделяемая шина чтения 1-го операнда. Весь массив из 64 НП возможно разбить на один, два или четыре подмассива (соответственно, из 64, 32 или 16 НП каждый подмассив). В каждом подмассиве возможно задание считывания одного общего для всех НП данного подмассива операнда. Источник общего операнда указывается при этом единичным состоянием соответствующего бита арифметической маски (ограничение – только один из разрядов маски должен быть «1» в данном подмассиве). Для управления разбиением массива НП на подмассивы введён 2-разрядный регистр режима (объединён в 1 байт вместе с PrL). В арифметической микрокоманде возможно задание записи результата во внутреннюю память одновременно с выдачей переноса в выходной оптический тракт. Транзитные передачи с оптического входа непосредственно на оптический выход задаются центральным устройством управления независимыми от микрокоманд сигналами. Данные передачи могут быть совмещены с текущими арифметическими операциями.

Синхронизация выдачи (вывода) информации из одного СБИС и приём её в другой (принимающий) СБИС (ввод) осуществляется центральным устройством управления по специальным сигналам. Система команд СБИС НП предусматривает как обработку операндов, предварительно загруженных во внутреннюю память, так и операндов, непосредственно заданных в микрокоманде (константы для задания 1-го или 2-го операндов). Кроме того, в качестве одного из операндов может выступать информация непосредственно с оптического входа. В последнем случае необходима синхронизация (управление оптическим входом) непосредственно от центрального устройства управления.

Технические особенности СБИС НП

Цикл (такт) работы устройства определён временем работы операционного устройства (акселератора умножения) и ориентировочно равен ~25 нc. Большинство операций выполняется за n тактов, где n = L (длина операнда). Для ускорения операции умножения в состав каждого НП введён акселератор умножения (реализует частично матричный способ умножения), который позволяет умножение двух чисел выполнить за 2n тактов. Кристалл СБИС НП ориентирован на выполнение основной нейрооперации – умножение с аккумулированием. Эта операция использует акселератор умножения, и время её выполнения превышает время умножения только на D тактов, где D – добавочная длина аккумулятора результатов сложения произведений (D= 8).

Акселератор умножений используется также для быстрого выполнения ещё двух нейроопераций: «манжеттоново» и «эвклидово» расстояния, в которых для быстрого сложения аккумуляторов нейропроцессоров внутри каждого из подмассивов в составе СБИС НП введён общий сумматор подмассивов (выполняет свёртку результатов НП подмассивов).

Для максимального ускорения операций выполнение внутренних микроопераций над слайсами конвейеризовано, так что обработка каждого слайса завершается за 1 такт. Задание адресов хранения исходных операндов и результатов совершенно произвольно и не ставит перед центральным устройством управления каких-либо значительных ограничений. Совмещённое выполнение текущих операций с операциями ввода/вывода ставит перед центральным устройством управления только задачу слежения за концептуальностью выполнения команд. Всякий раз, приняв микрокоманду соответствующего вида на выполнение, СБИС НП выставляет в центральное устройство управления сигнал занятости по данному виду и снимает его только по окончании обработки последнего слайса. Обработка слайсов может быть задана от младших к старшим (как правило) или наоборот (от старших к младшим, в некоторых операциях, например, операциях поиска МАХ, MIN). При этом независимо от вида обработки в исходной микрокоманде указываются в качестве начальных адреса младших слайсов операндов.

Внутреннее устройство управления СБИС НП самостоятельно определяет все виды конфликтов при обращении за операндами и автоматически выбирается необходимая временна¢я диаграмма по выполнению микрооперации над слайсами и вид совмещения (полное или неполное совмещение). Поэтому для обеспечения максимального быстродействия программа (микропрограмма) с указанием адресов хранения операндов и результатов, а также адресов ввода и вывода должна быть оптимизирована (на этапе составления объектного кода программы).

Таким образом, СБИС НП имеет основные количественные и технологические характеристики:

- система элементов (база) КМОП ~0,18 мкм;

- количество бит оптического входа/выхода – 64/64;

- количество бит микрокоманды – 16;

- количество управляющих дополнительных сигналов – 10, 32;

- количество признаков результатов – 6;

- количество бит электронной шины – 32;

- ориентировочное количество транзисторов ~0,6 млн;

- скорость оптических переключений (вместе с системой памяти и с акселератором умножения определяет такт работы всей системы) ~25 нc.

Кристалл маршрутизатора SPACE WIRE – 3D М ФЭ СБИС SW

Кристалл 3D М ФЭ СБИС SW предназначен для обмена информацией по стандарту SpaceWire и позволяет работать по 32 оптическим линиям связи и 2 электрическим линиям связи с оконечными объектами под управлением контроллера – маршрутизатора SPACE WIRE, реализующего протокол подключения точка–точка. Аналогично предыдущим кристалл изготавливается по 180 нм КМОП-технологии SOI фирмы XFAB (технология XT018).

Алгоритм функционирования кристалла 3D М ФЭ СБИС SW полностью соответствует общему описанию протокола SpaceWire.

Основные характеристики 3D М ФЭ СБИС SW

Технологически матрица кристалла 3D М ФЭ СБИС SW изготовлена форматом 8 ´ 8 интеллектуальных пикселей с модуляцией по принципу DS-кодирования. Количество оптических каналов ввода – 64. Каждый пиксель имеет электрический драйвер вывода для подключения лазеров вертикального излучения. В кристалле также присутствует электрическая процессорная параллельная шина EMIFA и два электрических SpaceWire-канала входа-выхода. Таким образом количество оптических коммутируемых SpaceWire- каналов – 32 со скоростью до 300 МГц.

Кристалл 3D М ФЭ СБИС SW позволяет работать по 32 оптическим линиям связи и 2 электрическим линиям связи с оконечными объектами под управлением контроллера – маршрутизатора SPACE WIRE, реализующего протокол подключения точка–точка по стандарту SPACE WIRE для удалённой связи по многоканальным оптическим и локальным электрическим каналам связи.

Представленный базовый ряд функциональных трёхмерных модулей фотон-электронных СБИС (3D М ФЭ СБИС) является основанием для формирования трёхмерных фотон-электрон-фотонных Гибридных Интегральных Многокристальных Схем (3D М ФЭФ ГИМС) и создания модулей на их основе (3D М ФЭФ М).

В перспективных разработках будут дополнительно включены в структуру матриц 3D М ФЭ СБИС базового функционального ряда аналого-цифровые и цифроаналоговые преобразователи. Это позволит увеличить объём многоканальной информации. Так, при тактовой частоте 166 МГц, АЦП / ЦАП 2.8 (2.16) и матрице оптических каналов 64 имеем поток данных 166 ´ 8 ´ 64 = 84,992 Гбит (166 ´ 16 ´ 64 = 169,984 Гбит) между модулями 3D М ФЭФ М.

Модуль 3D М ФЭФ М с базовым рядом функциональных кристаллов 3D М ФЭ СБИС может применяться для построения информационно-вычислительных, коммутационных и радиолокационных устройств, а также систем и комплексов большой сложности и высокой производительности, например:

- 3D М ФЭФ минисупер ЭВМ с параллельной многопроцессорной архитектурой;

- 3D М ФЭФ ЭВМ для высокопроизводительных векторных вычислений с параллельной организацией данных;

- 3D М ФЭ минисупер ЭВМ для сверхсложного нейросетевого моделирования различных процессов, в том числе и социально значимых;

- 3D М ФЭФ векторно-матричная ЭВМ для сверхскоростных вычислений;

- 3D М ФЭФ многопрофильная модульно-наращиваемая многоканальная цифровая антенная решётка с локальными или удалёнными центрами обработки и управления многоканальной информацией;

- 3D М ФЭФ цифровая антенная решётка с системой удалённого центра обработки и управления многоканальной информацией авиационного мониторинга технического состояния самолёта или гуманитарного состояния лётного состава для предупреждения катастрофы, включая дистанционную принудительную посадку самолёта из центра;

- 3D М ФЭФ модульно-наращиваемая, многоуровневая, неблокируемая процессорная система коммутации аэрокосмического стандарта SpaceWire с оптическими и электрическими многоканальными линиями связи для формирования многоуровневых, многодатчиковых архитектур для внутриобъектовых и удалённых коммутационных и информационно-вычислительных систем.

Специалисты российского предприятия «Микрон» принимали участие в разработке и изготовлении 3D М ФЭ СБИС функционального ряда по проектным нормам 180 нм. Сегодня на предприятии «Микрон» внедрена кремниевая технология с 90 нм технологическими нормами. Изготовление 3D М ФЭ СБИС по проектным нормам 90 нм позволит получить улучшить технические характеристики 3D М ФЭ СБИС функционального ряда, при этом для сопряжения с 3D М ФЭ СБИС могут применяться российские DSP-процессоры отечественных предприятий «МОДУЛЬ» (Л1879ВМ3) и/или «ЭЛВИС» (1892ВМ14Я с двумя электрическими портами SpaceWire).

Заключение

Модули и устройства, разработанные на основе 3D М ФЭ СБИС функционального ряда и базового ряда многоканальных волоконных и призменных оптических элементов ООО «ОЭС» могут быть применены в высокопроизводительных аэрокосмических и наземных радиоинформационных, информационно-коммутационных и вычислительных системах и комплексах.

В следующей части статьи будут описаны конструктивные решения модулей 3D М ФЭФ М с использованием алюмооксидной и LTCC-технологий на основе мезонинных печатных плат в различных модификациях с описанием преимуществ и недостатков соответствующих решений.

Литература

-

Сведе-Швец В., Сведе-Швец В., Зиновьев М. Кремниевая и арсенид-галлий-алюминиевая технология: базовый ряд 3D М ЭФ СБИС VCSЕL и функциональных 3D М ФЭ СБИС для 3D М ФЭФ М. Часть 4. Современная электроника. 2017. №6. С. 18

Если вам понравился материал, кликните значок — вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал —не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!