Введение

Полупроводниковая оперативная память классифицируется по её способности сохранять данные при отсутствии напряжения питания. Статическая память с произвольным доступом (SRAM) теряет содержащиеся в ней данные при выключении напряжения питания и является энергозависимой памятью. Другим типом энергозависимой памяти является динамическая память с произвольной выборкой (DRAM), применяющаяся во всех настольных компьютерах и ноутбуках.

Память, сохраняющая данные при отсутствии напряжения питания, называется энергонезависимой. К такому типу памяти относятся: энергонезависимая SRAM (nvSRAM), ферроэлектрическая RAM (F-RAM), электрически стираемая перепрограммируемая ROM (EEPROM), флэш-память, магниторезистивная (MRAM) и другие. Эти виды памяти применяются там, где необходимо сохранять важные данные при отключённом питании или при периодических прерываниях подачи напряжения питания во время работы. Примером прерывания подачи питания может служить «горячее» подключение и отключение карт памяти к серверам, промышленным компьютерам, медицинскому оборудованию. При этом не происходит потери важных данных в памяти устройств.

Память nvSRAM относится к классу энергонезависимой памяти и при этом сохраняет все достоинства SRAM-памяти. В отличие от других технологий энергонезависимость nvSRAM-памяти Cypress обеспечивается без использования батарей, суперконденсаторов или иных источников питания для сохранения данных. Память nvSRAM имеет ряд преимуществ в тех приложениях, где требуются одновременно высокое быстродействие и энергонезависимость в недорогом исполнении. Такие решения востребованы в интеллектуальных измерительных приборах, серверах, ПЛИСах, игровых приставках, многофункциональных принтерах и массивах памяти.

Компания Cypress предлагает несколько семейств высокоскоростных nvSRAM-продуктов, обеспечивающих более 20 лет хранения данных. Длительное хранение данных происходит в энергонезависимых элементах, интегрированных с ячейками SRAM-памяти.

Во время работы в режиме быстрой SRAM-памяти (время доступа менее 20 нс) память nvSRAM может сохранять (STORE) или считывать (RECALL) данные из энергонезависимых ячеек. Операции STORE и RECALL могут выполняться как по команде из программы пользователя, так и автоматически (режим AutoStore). В режиме AutoStore устройство nvSRAM автоматически переписывает содержимое ячейки памяти SRAM в ячейку энергонезависимой памяти в момент выключения питания за счёт запасённой энергии во внешнем конденсаторе. Затем, после подачи напряжения питания на устройство данные автоматически восстанавливаются из энергонезависимой ячейки хранения в SRAM-ячейку памяти без участия программы пользователя.

Энергонезависимые элементы памяти, также называемые «теневой» EEPROM, гарантируют сохранность данных в течение не менее 20 лет при максимальной рабочей температуре.

Архитектура ячейки nvSRAM

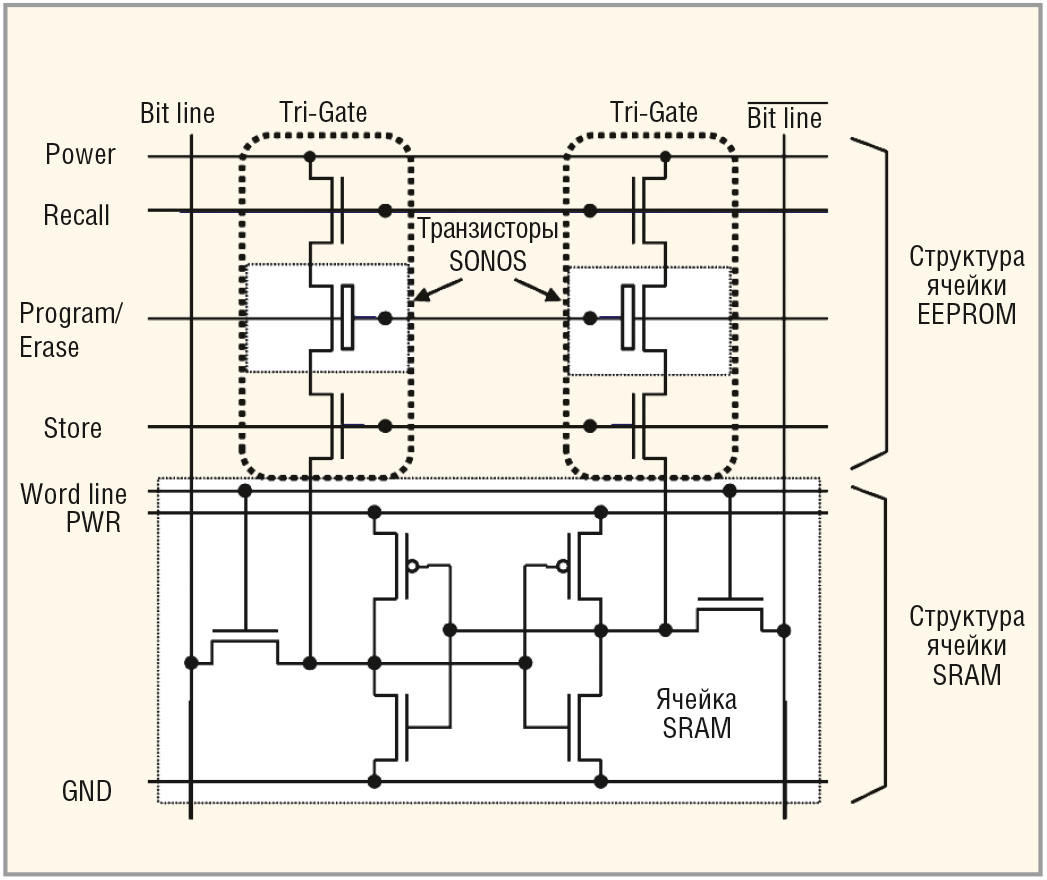

Память nvSRAM компании Cypress объединяет в себе стандартные КМОП-ячейки SRAM и ячейки EEPROM, выполненные по технологии SONOS для обеспечения быстрой работы в режиме чтения-записи и сохранности данных на протяжении не менее 20 лет. Каждая ячейка SRAM работает в паре со своей ячейкой EEPROM. Архитектура ячейки nvSRAM памяти показана на рисунке 1.

До тех пор, пока на прибор подаётся напряжение питания, он работает точно так же, как и обычная SRAM-память. Когда питание пропадает, содержимое каждой ячейки SRAM может автоматически сохраняться в присоединённой к ней ячейке энергонезависимой памяти. Энергонезависимые ячейки используют стандартную КМОП-технологию, обеспечивающую высокую производительность для совместной работы со SRAM-памятью. Кроме того, технология SONOS обеспечивает высокую устойчивость и способность выдержать до 1 миллиона циклов выполнения операции STORE.

Интерфейс

Интерфейс связи для nvSRAM реализуется подобно интерфейсу связи с обычной высокоскоростной SRAM-памятью, но имеет несколько характерных выводов.

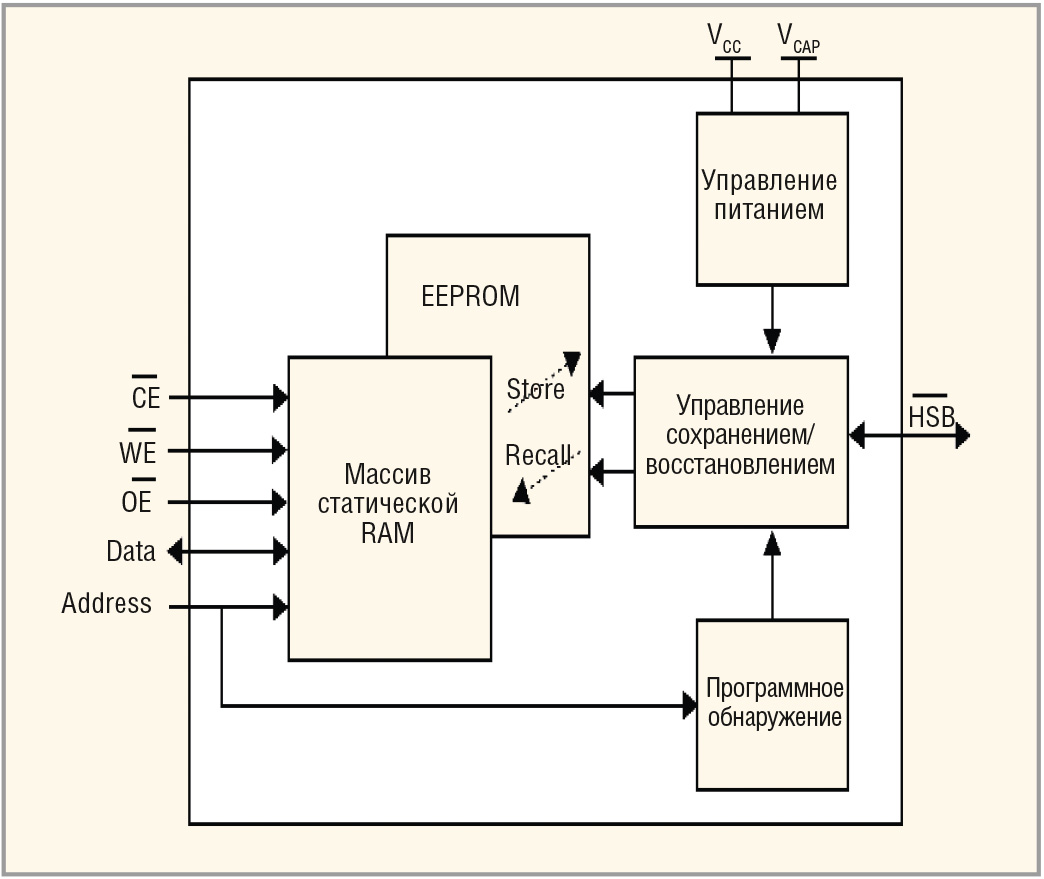

На рисунке 2 показана логическая схема параллельного интерфейса nvSRAM. Шины адреса, данных и управления аналогичны интерфейсу быстродействующей SRAM. Для обычных операций чтения-записи, обращение к памяти происходит так же, как к SRAM. Последовательные nvSRAM и асинхронный NAND интерфейс nvSRAM имеют те же логические блоки, что и у SRAM.

Блок управления питанием отслеживает изменения питающего напряжения (VCC) для включения режима автосохранения. Блок программного обнаружения отслеживает последовательности чтения адреса при записи и восстановлении данных во всех режимах, и управляет включением/выключением режима автосохранения. Блок управления сохранением/восстановлением управляет включением операций сохранения или считывания данных, с возможностью аппаратного включения операции сохранения через вывод HSB. Программно операция автосохранения осуществляется через стандартный интерфейс SRAM.

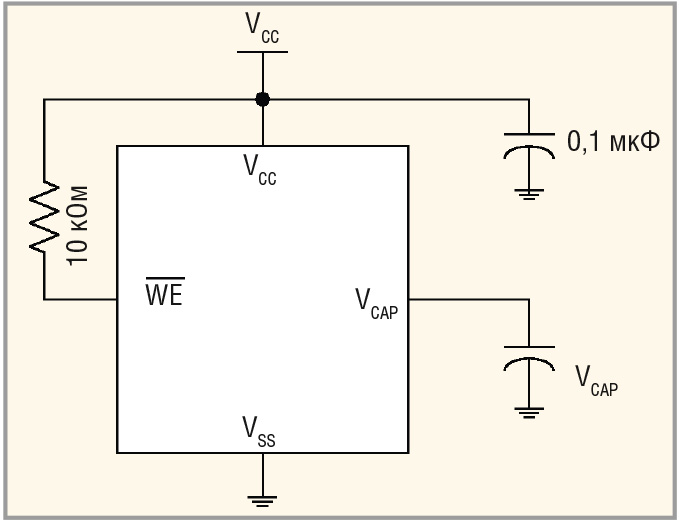

Таким образом, для применения памяти nvSRAM вместо SRAM потребуются лишь незначительные аппаратные изменения. Единственным дополнительным компонентом, необходимым для реализации операции автосохранения является конденсатор, подключённый к выводу VCAP, который при включении заряжается до напряжения питания. Накопленная энергия заряда этого конденсатора используется при переносе содержимого энергозависимой статической памяти в энергонезависимую область при выключении питания. Требуемая ёмкость конденсатора указывается в справочном листке для каждой конкретной микросхемы и обычно составляет около 60–100 мкФ.

На рисунке 3 показано подключение накопительного конденсатора (VCAP) и смещающего резистора к выводу WE. Смещение необходимо для предотвращения случайной записи контроллером чтения-записи, поскольку при восстановлении питания он готов к работе позже, чем nvSRAM.

Процесс энергонезависимого хранения

В процессе энергонезависимого сохранения данные передаются параллельно из SRAM в энергонезависимые ячейки SONOS. Параллельная запись позволяет осуществлять эту операцию менее чем за 8 мс.

Режим nvSRAM STORE может быть осуществлён тремя способами:

- Автоматически – начинается при отключении питания устройства.

- Программно – из исполняемой программы;

- Аппаратно – используется вывод HSB.

Во время перемещения данных в энергонезависимые элементы, предыдущая информация в них стирается и заменяется новой. После начала цикла сохранения все операции чтения-записи прекращаются до его завершения.

Сигнал на выводе HSB позволяет системе определять статус режима сохранения. При низком уровне на нём память nvSRAM будет недоступна. Для уменьшения числа ненужных сохранений аппаратное или автоматическое сохранение не выполняется, если после предыдущего цикла сохранения или восстановления не было хотя бы одной записи в память. Однако при программном запуске сохранение выполняется в любом случае.

Автосохранение

В режиме автосохранения данные автоматически сохраняются в EEPROM при снижении напряжения питания ниже определённого уровня. До тех пор, пока питание поступает, конденсатор, подключённый к выводу VCAP, заряжается. При достижении напряжением питания критического уровня начинается процесс автосохранения. Энергии, накопленной в конденсаторе, хватает на один цикл сохранения.

Аппаратный запуск сохранения

Для аппаратного запуска сохранения используется вывод HSB. Когда внешний контроллер подаёт на этот вывод низкий логический уровень, после некоторой задержки начинается цикл сохранения. При этом сохранение начнётся только в случае, если после предыдущего цикла сохранения или восстановления была осуществлена запись в SRAM. Задержка позволяет закончить все текущие записи в память.

Вывод HSB является выходом с открытым стоком (через внутренний резистор 100 кОм подключён к шине питания) и при происходящем аппаратном или программном сохранении сигнализирует о статусе «занят» низким логическим уровнем. Низкий логический уровень на этом выводе поддерживается nvSRAM в течение любых сохранений независимо от того, как они инициированы, до окончания операции. nvSRAM остаётся недоступной до тех пор, пока на этом выводе не появится высокий логический уровень.

Если данный вывод не используется, его можно оставить не подключённым.

Программный запуск сохранения

Данные из SRAM перемещаются в энергонезависимую память последовательно адрес за адресом. Программный цикл STORE инициализируется путём запуска контролируемых входами CE или OE последовательности циклов чтения из шести особых адресов в точно заданном порядке. В процессе сохранения в энергонезависимой памяти стираются данные, сохранённые в прежнем цикле, и заменяются новыми. Чтение и запись невозможны до окончания процесса сохранения.

Восстановление данных

Восстановление данных происходит путём их перемещения из EEPROM в SRAM по параллельной шине менее чем за 30 мс. Процесс восстановления может быть начат при включении питания или из программы пользователя.

При включении питания или выходе из состояния с низким энергопотреблением, когда напряжение питания превысит уровень переключения, начнётся процесс восстановления, который продлится некоторое время. В течение этого времени на выводе HSB будет установлен низкий логический уровень, что сделает невозможным осуществление операций чтения-записи nvSRAM.

Программное восстановление инициируется таким же способом, как и программное сохранение, и осуществляется путём считывания специальной последовательности из шести адресных ячеек без доступа к адресам ячеек, находящимся между ними.

nvSRAM во время операций в энергонезависимом режиме

Во время исполнения операций сохранения и восстановления данных память nvSRAM недоступна для внешних устройств.

На входах игнорируются все логические уровни и их изменения, а выходы, за исключением вывода HSB, находятся в третьем логическом состоянии. Чтение и запись данных можно начинать только после завершения операции сохранения/восстановления. Низкий логический уровень на выводе HSB устанавливается внутренней схемой и сигнализирует о занятости nvSRAM.

Если вывод подключён к внешним элементам, то необходим внешний резистор между ним и шиной питания. Обычно достаточно резистора номиналом около 10 кОм.

Защита от непреднамеренного сохранения

Память Cypress nvSRAMs имеет встроенные средства для предотвращения непреднамеренного запуска операции сохранения.

Когда напряжение питания снижается ниже уровня переключения, у nvSRAM становятся недоступны операции ввода-вывода и отменяются запущенные пользователем операции сохранения. Это гарантирует, что операции сохранения, инициированные программно или аппаратно, не начнутся, поскольку для их выполнения недостаточно питания. Кроме того, для операций сохранения, инициированных аппаратно или автоматически, требуется, чтобы после последнего сохранения была произведена хотя бы одна запись в SRAM.

Описанные средства гарантируют, что нестабильность питающего напряжения или помехи на линии вывода HSB не приведут к ненужным запускам операции сохранения.

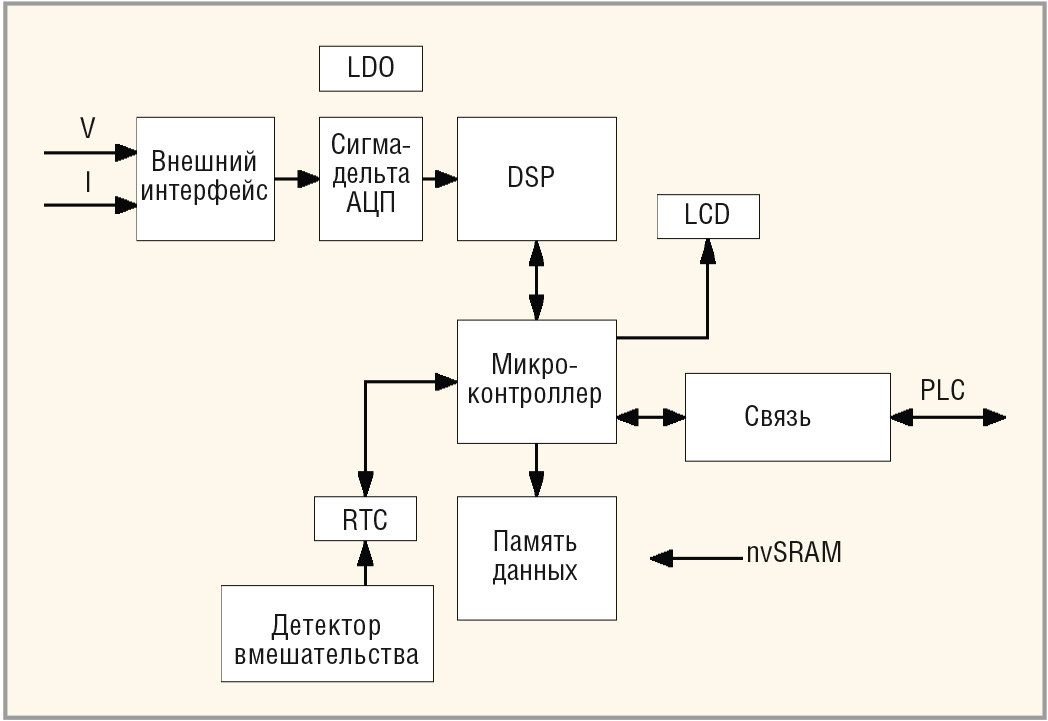

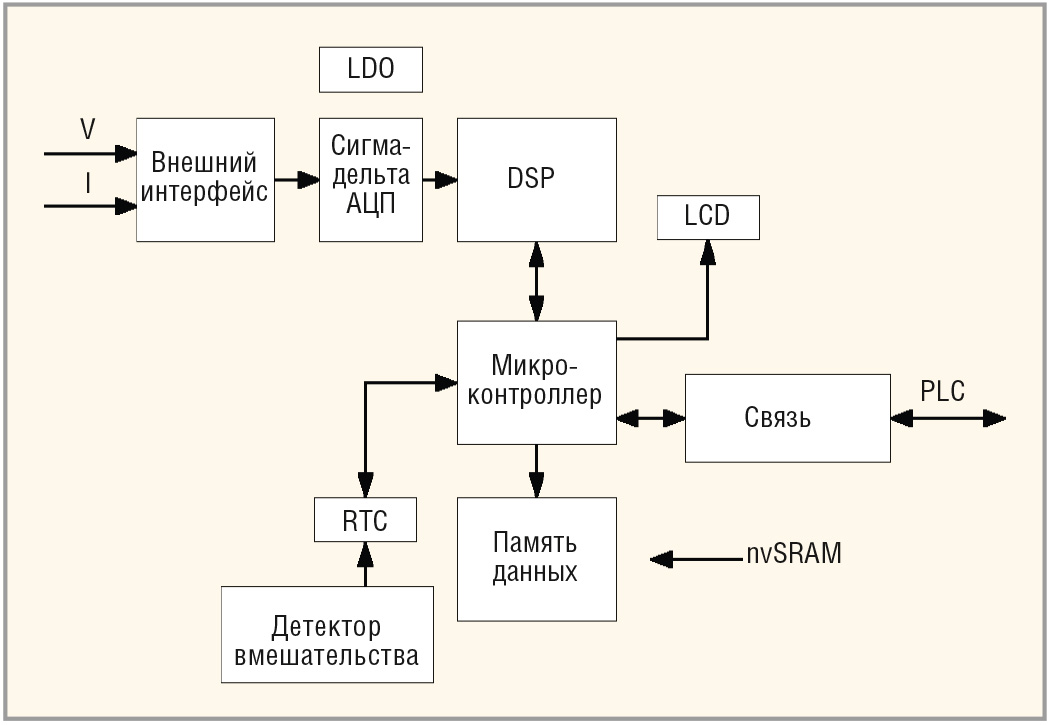

Область применения Cypress nvSRAM

Cypress nvSRAM хорошо подходит для применения там, где требуются высокая скорость доступа и долговременная надёжность. Среди таких приложений можно отметить системы хранения данных в RAID-архивах (см. рис. 4), системы «умных» счётчиков электроэнергии (см. рис. 5), программируемые логические контроллеры, многофункциональные принтеры.

Заключение

Память nvSRAM с параллельным доступом сочетает в себе все достоинства быстрой памяти SRAMs с оригинальной технологией энергонезависимости, которая реализуется посредством встроенной флэш-памяти и небольшого внешнего конденсатора. Наряду с простотой и доступностью данное решение обеспечивает высокую надёжность хранения данных.

В архитектуре nvSRAM используются такие же шины данных, адреса и управления, что и в асинхронных SRAM. Благодаря этому применение памяти nvSRAM существенно упрощается. Для упрощения построения сложных систем некоторые микросхемы оснащены дополнительными встроенными функциями, например, часами реального времени.

Память Cypress nvSRAMs с последовательным доступом имеет стандартные I2C и SPI-интерфейсы, что позволяет применять её в высокоскоростных приложениях с малым числом контактов.

Cypress также предлагает асинхронный интерфейс NAND nvSRAM, соответствующий спецификации ONFI 1.0, со скоростью доступа к данным до 33 МГц.

Обзор подготовлен по материалам статьи Рави Пракаш (Ravi Prakash), инженера по применению компании Cypress Semiconductor Corp.

Литература

- Nonvolatile SRAM (nvSRAM) Basics.

- www.cypress.com/file/46216/download

Если вам понравился материал, кликните значок - вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал - не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!