В конце 2009 года была принята спецификация PICMG 2.30, которая является ещё одним шагом в закреплении технических решений основных игроков в сегменте последовательных коммуникационных технологий для объединительных панелей высокопроизводительных систем. Прежде чем перейти к детальному обсуждению сути самой этой спецификации, будет не лишним ещё раз оглянуться на историю развития объединительных панелей высокопроизводительных систем, под которыми мы будем понимать магистрально-модульные системы, ориентированные на рынок индустриальных и специализированных решений.

Немного истории

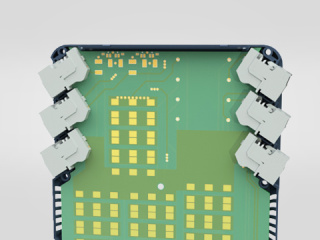

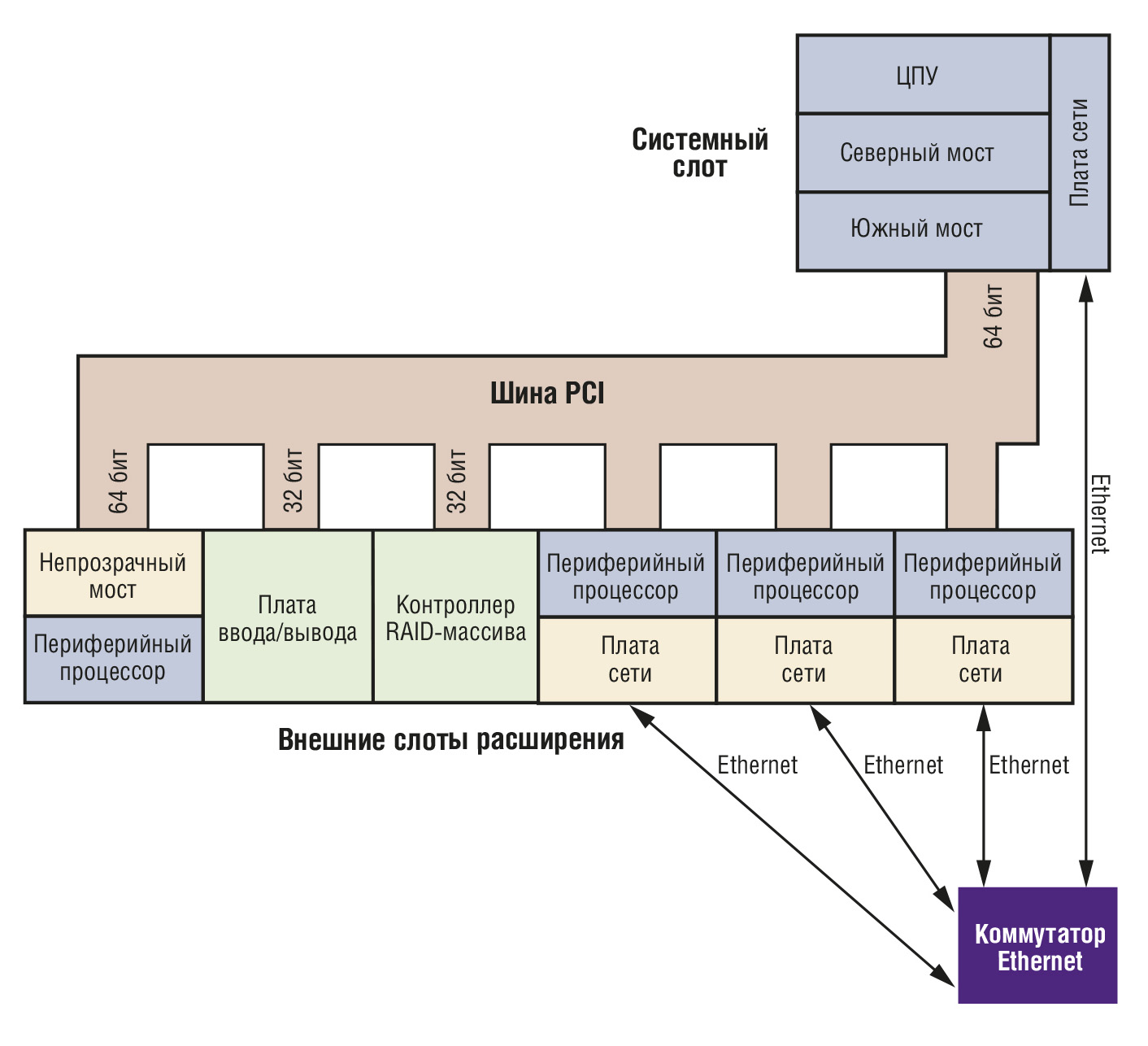

Безусловным ветераном в этом сегменте является детище фирмы Motorola – шина VME. Это параллельная, асинхронная, имеющая 32- и 64-разрядные варианты исполнения, появившаяся в 70-х годах прошлого столетия и до сих пор здравствующая шина. Фактической монополии этой шины пришел конец с появлением в 1997 году спецификации PICMG 2.x, определившей новый стандарт CompactPCI (рис. 1).

В отличие от VME эта шина, во многом являющаяся преемницей классической шины PCI v.2.1, – синхронная и мультиплексируемая, но так же, как и VME, параллельная.

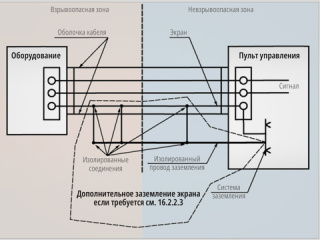

Надо сказать, что вообще конец прошлого и начало этого столетия в сфере творческих дискуссий о развитии системных шин ознаменовались весьма бурной полемикой. Сначала «хоронили» шину ISA, вместо использования которой предлагался тотальный переход на PCI, потом намечались тотальные «похороны» параллельных шин. Но самое интересное, что многие последовательные шины, прочившие себя в альтернативу параллельным, канули в Лету (например, StarFabric), в то время как шина ISA и та же долгожительница VME и по сей день живы и здоровы. Тем не менее движение в сторону последовательных шин на объединительных панелях является объективной необходимостью текущего состояния потребительских запросов на сервисы и современные технологии, их обеспечивающие. Если вернуться к нашей теме, то наиболее удачной спецификацией в плане реализации идей внедрения последовательных шин на объединительной панели, но не замещающей, а развивающей стандарт CompacPCI (сPCI), является PICMG 2.16 R1.0 CompactPCI Packet Switching Backplane (для VME подобная функциональность поддерживается для устройств, отвечающих стандарту ANSI/VITA 31.1). Соответствующая архитектура представлена на рис. 2.

Эта спецификация была принята в 2001 году. На мой взгляд, она была не просто неожиданным прецедентом, а одним из серьёзнейших переосмыслений иерархической модели связей, переводящих Ethernet из межсистемной коммуникации верхнего уровня в фактически сквозную (включая полевой уровень) вертикальную связь. Это безусловно прогрессивное решение позволяет в рамках одного крейта строить высоконадёжные масштабируемые решения, активно используя при этом весь парк материальных наработок в виде классических плат расширения ввода/вывода для шины CompactPCI. В то же время при наличии «интеллектуальных» плат в этом же крейте можно без особых усилий осуществлять полноценный обмен данными как в рамках сети крейта, так и в рамках межсистемной (межблочной) связи, при этом опять же активно используя ранее наработанное программное обеспечение для сети Ethernet. Реализация спецификации PICMG 2.16 позволяет решить многие проблемы, но не все. Так, при необходимости использовать интерфейс Ethernet в рамках крейта появляется в соответствии с принципами организации сетей Ethernet достаточно дорогостоящий элемент – коммутатор. Кроме того, спецификация PICMG 2.16 реализуется только для варианта исполнения 6U сPCI, так как Ethernet-связи задействуют контакты разъёма P3, отсутствующего в варианте 3U cPCI.

Развитие технологии PCI Express

На текущий момент в гонке за обладание «жёлтой майкой» лидера системной последовательной шины для объединительных панелей фактически остались две технологии – Ethernet и PCI Express (PCIe).

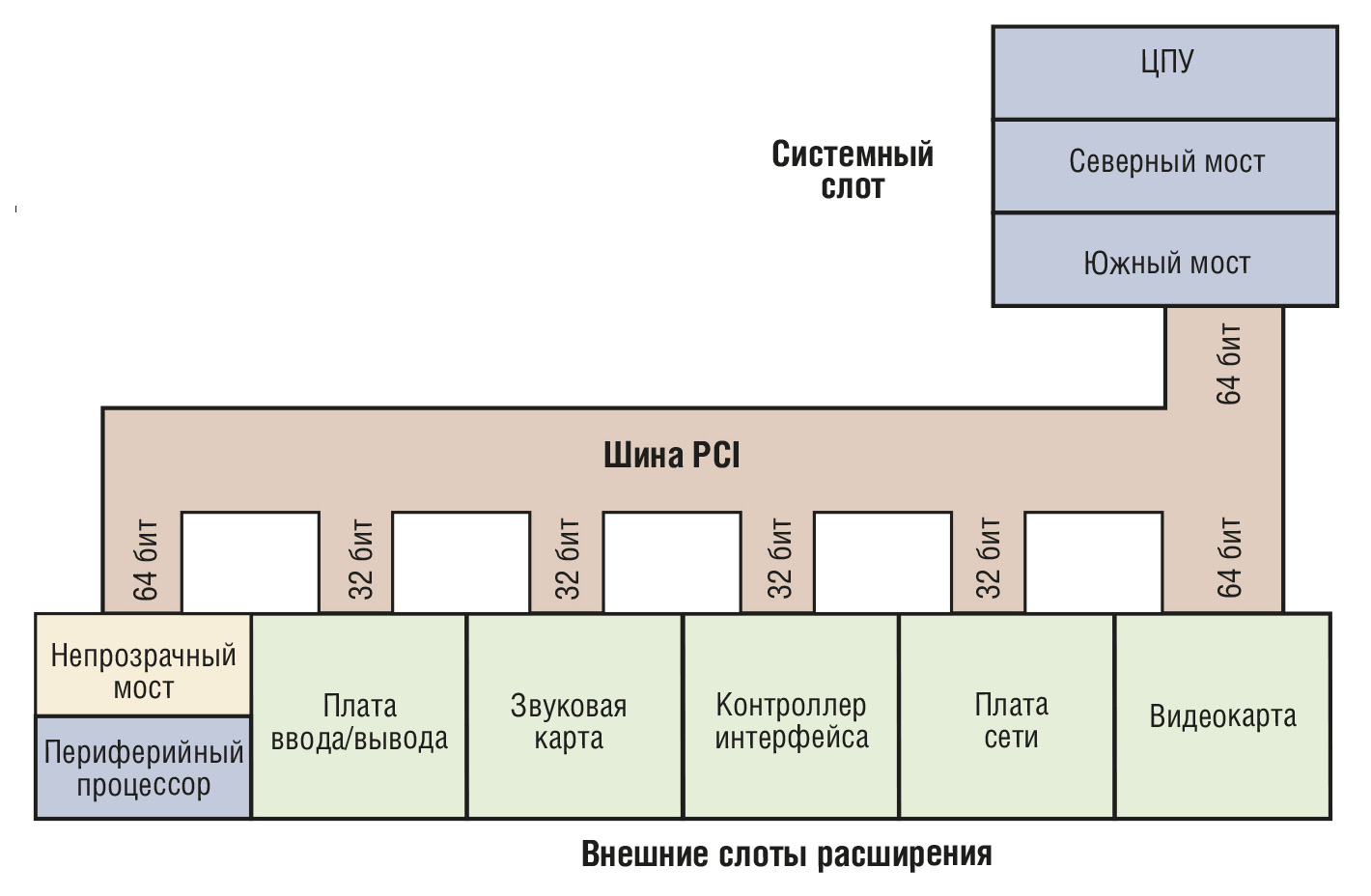

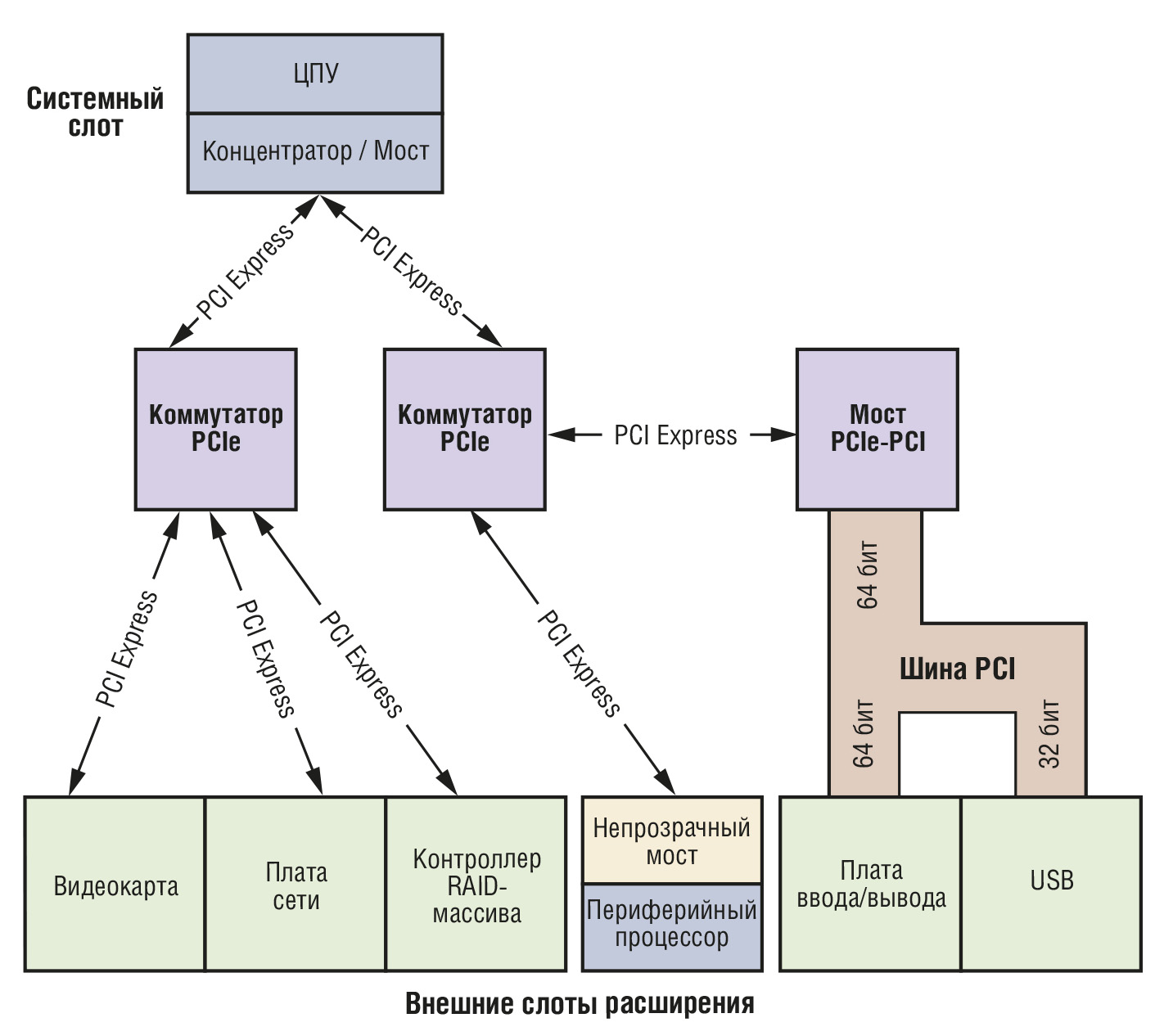

Официально первая базовая спецификация PCI Express (ранее известная как 3GIO – ввод/вывод 3-го поколения) увидела свет в июле 2002 года. Можно только порадоваться динамичности сообщества PICMG, оперативно внедряющего современные технологии в уже существующие и зарекомендовавшие себя промышленные стандарты. Так, уже в июне 2005 года появилась спецификация CompactPCI Express (PICMG EXP.0 R1.0 Specification). Она ставила своей целью внедрение последовательного интерфейса PCI Express в платформы на базе спецификации CompactPCI PICMG 2.0 (по сути, это была попытка тотального перехода на PCI Express) и удовлетворение будущих потребностей рынка приложений вооруженных сил и авиации. В стандарте CompactPCI Express определяются новые типы разъёмов, детально описываются требования к электрическим и механическим характеристикам 3U/6U системных и периферийных плат, а также к платам коммутаторов и бекплейнам. В частности, определяется древовидная топология (рис. 3), соединители, которые поддерживают полосу пропускания PCI Express первого поколения и потенциальную возможность её увеличения в будущем (High-Speed Advanced Differential Fabric Connectors – ADF, Hard Metric – eHM).

Системный слот обеспечивает широкополосные варианты линков PCI Express (четыре x4 PCIe, два x8 PCIe и т.д. на двух разъёмах ХР2 и ХР3) и тыльный ввод/вывод, а также поддерживает возможность обеспечения повышенного энергопотребления как ныне применяемых, так и перспективных моделей процессоров. Периферийные слоты обеспечивают возможность поддержки процессорных плат (тип 1), а также поддержку плат, не требующих широкополосной передачи данных шире x8 PCIe (тип 2). Кроме того, на бекплейне установлены гибридный слот, обеспечивающий поддержку PCI32 и PCIe, унаследованный (или традиционный) слот, служащий для возможности подключения плат в стандарте CompactPCI PICMG 2.0, и слот коммутатора. Архитектура и технические решения, определяемые спецификацией для реализации заложенных в неё возможностей, фактически требуют создания новых комплексных решений, так как предполагается активное использование развёрнутой масштабируемой последовательной коммуникации со всеми присущими техническими атрибутами (в частности, с коммутаторами, встроенными или установленными на объединительной панели).

Эта прогрессивная спецификация, безусловно, требует серьёзных капитальных вложений для реализации заложенной в ней идеологии, что в наше время несколько расходится с доминирующими тенденциями, ориентированными в основном на экономию (COTS-технологии). Кроме того, в спецификацию не интегрированы в явном виде некоторые современные последовательные интерфейсы, доказавшие свою состоятельность (речь идёт о Gigabit Ethernet, SATA/SAS, USB 2.0).

Прагматизм как основа философии спецификации

История развития технических решений говорит о том, что потенциальной живучестью обладают те из них, которые обеспечивают разумный баланс между предыдущими наработками и возможностью использовать современные спецификации. Давайте попробуем посмотреть на необходимые ресурсы подсистем в некоторой «усреднённой» системе управления. Одной из основных её подсистем является подсистема ввода/вывода. Надо признать, что в подавляющем большинстве случаев нет необходимости в увеличении скорости доступа к периферийным платам, осуществляющим ввод/вывод, так как скорость физических процессов, данные которых обрабатываются ими, существенно медленнее, чем время обмена данными между процессором и периферийной платой. Это же относится и к периферийным платам, осуществляющим управление физическими процессами. К классическим примерам можно отнести измерение температуры, которая принципиально не может скачкообразно измениться, либо управление через цифровой выход реле или механическими исполнительными устройствами. К базовым подсистемам также относятся подсистемы хранения данных и визуализации. Здесь уже очевидна необходимость в увеличении пропускной способности интерфейса связи, что, собственно, мы объективно и наблюдаем как в офисных вариантах настольных систем, так и в промышленных компьютерах (например, в промышленных компьютерах, использующих процессорные платы спецификации PICMG 1.3). Тотальный переход на последовательные интерфейсы Serial ATA для подсистем хранения данных и PCI Express для видеоподсистем не оставляет сомнений в своей целесообразности, практика таких решений стала стандартной.

Собственно, эти интерфейсы разработчики процессорных плат в формате cPCI уже давно используют как интерфейсы связи с платами мезонинов, обеспечивающими возможности разработки «вариантных компоновок» расширения функционала процессора. Но дело в том, что специфика организации связи мезонинов с процессорной платой часто не позволяет сторонним производителям участвовать в появлении актуальных вариантов таких расширений, делая использование данных системных интерфейсов для конкретной процессорной платы фирменно зависимым. В то же время для настольных систем вынесение PCI Express для организации видеоподсистемы, очевидно, способствует разнообразию предлагаемых решений, что определяется как разнообразием чипов видеопроцессоров от разных производителей, так и разнообразием функциональных возможностей видеокарт в рамках линейки одного производителя. То есть вынесение этих стандартных интерфейсов в поле стандартизованного форм-фактора было бы благом с точки зрения увеличения вариантов технических решений для таких подсистем; кроме того, пространственное разнесение при этом процессора, видео-процессора и подсистемы хранения (на мезонинах часто предполагается возможность крепления 2,5" HDD) создаёт условия для улучшения распределения тепла в системе. Очевидно, что внешние интерфейсы позволят использовать вновь разработанные периферийные платы ввода/вывода или подсистем хранения, требующие увеличенной скорости обмена между процессором и этими платами, которые нередко представляют собой достаточно интеллектуальные устройства с предобработкой входных сигналов (например, плата цифровой фильтрации на DSP-процессорах).

Если мы говорим о желаемой преемственности интерфейсов, ставших неотъемлемой частью современных систем управления, не стоит, наверное, отказываться и от наличия шины USB, которая позволит использовать наработанный парк внешних устройств с малой и средней скоростью обмена (всевозможные внешние флэш-накопители, беспроводные модемы, DVD-приводы и т.д.). А если говорить о подсистеме коммуникации, пожалуй, трудно не согласиться с тем, что Ethernet не только стал стандартом как основной интерфейс межсистемной связи, но и органично прижился как интерфейс связи на объединительной панели (вспомним PICMG 2.16).

Изложенные прагматичные соображения, которые мы рассмотрели в этом разделе, и легли в основу спецификации PICMG 2.30 CompactPCI PlusIO.

Ключевые особенности спецификации PICMG 2.30

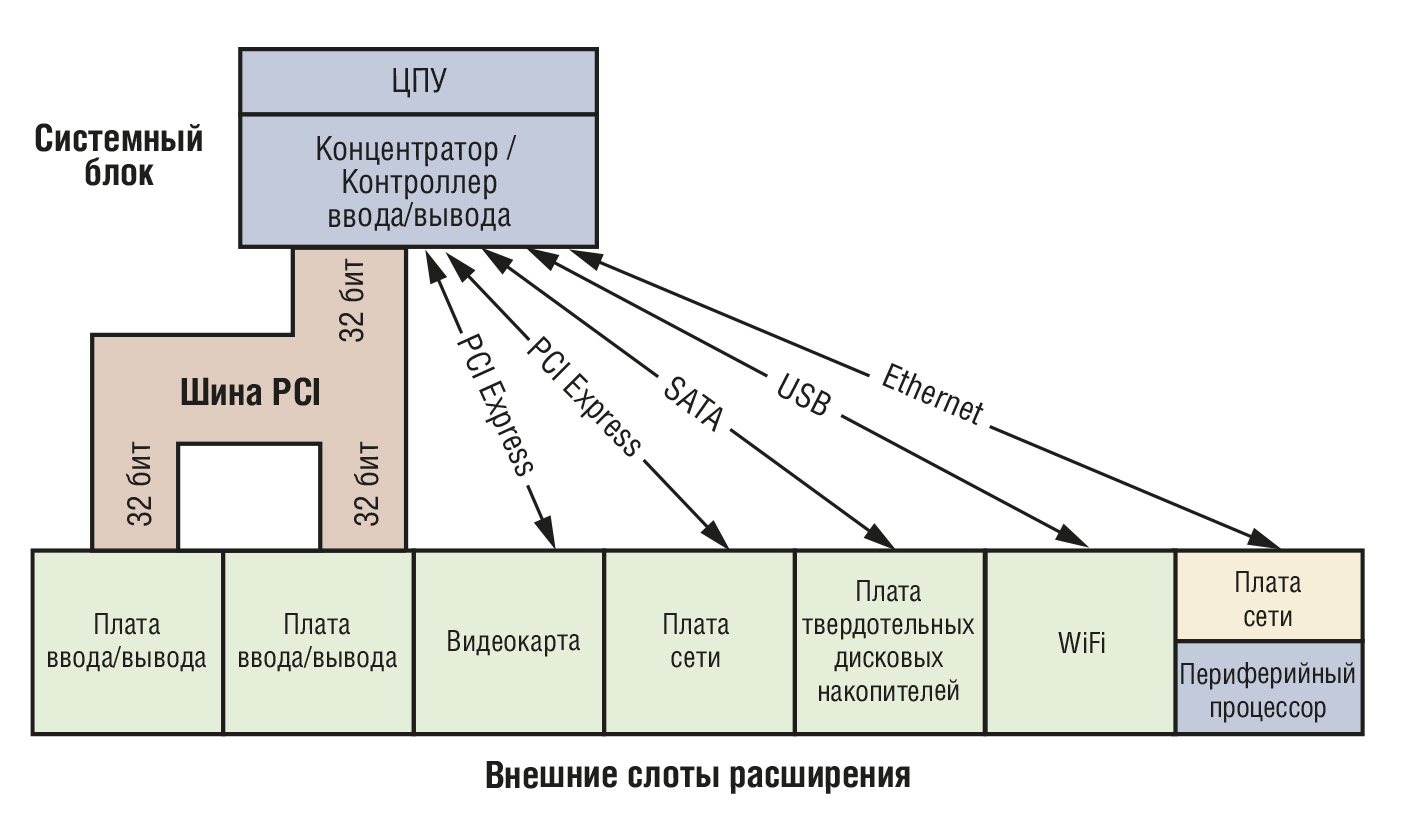

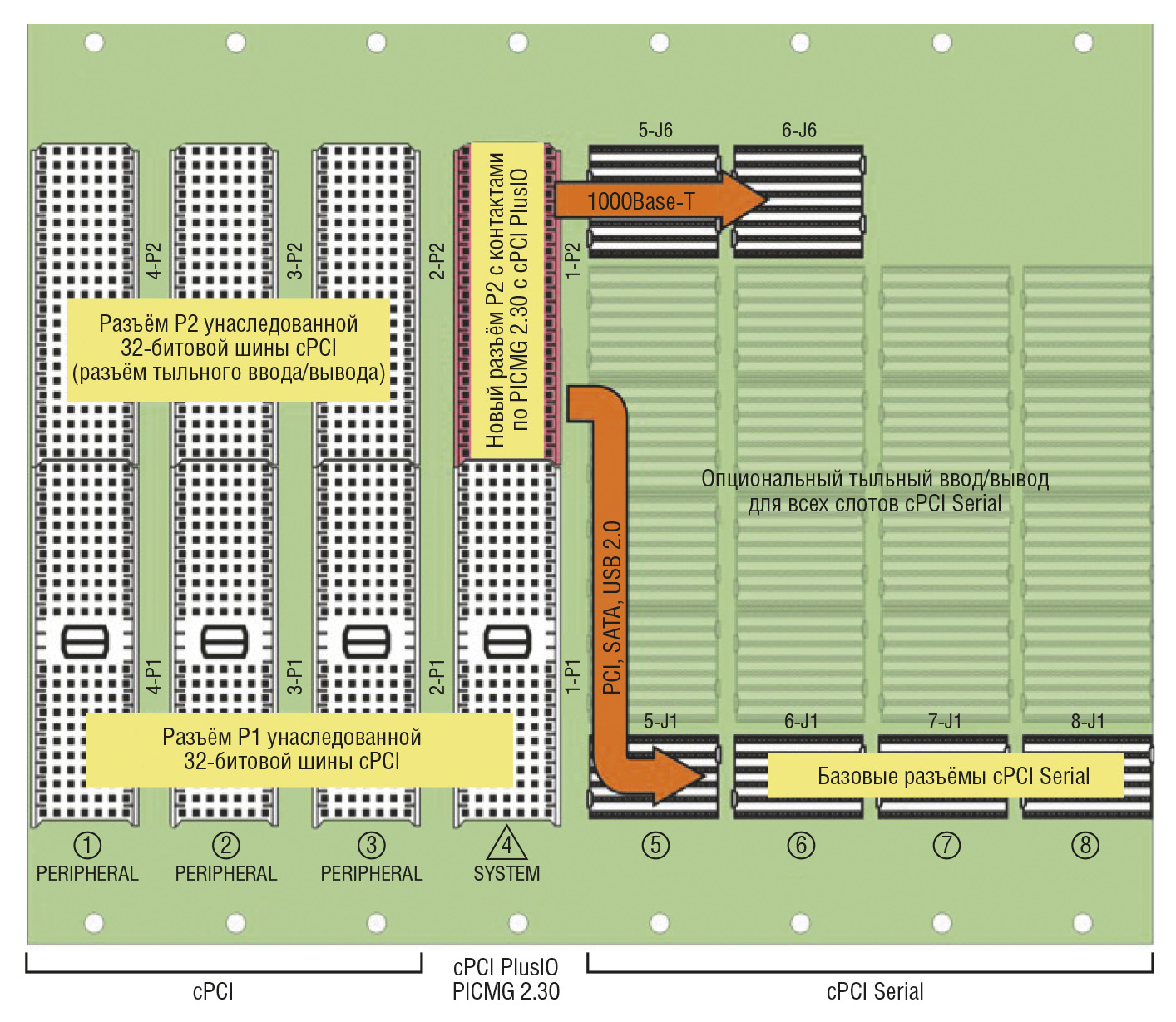

Архитектура системной шины в соответствии со спецификацией PICMG 2.30 представлена на рис. 4.

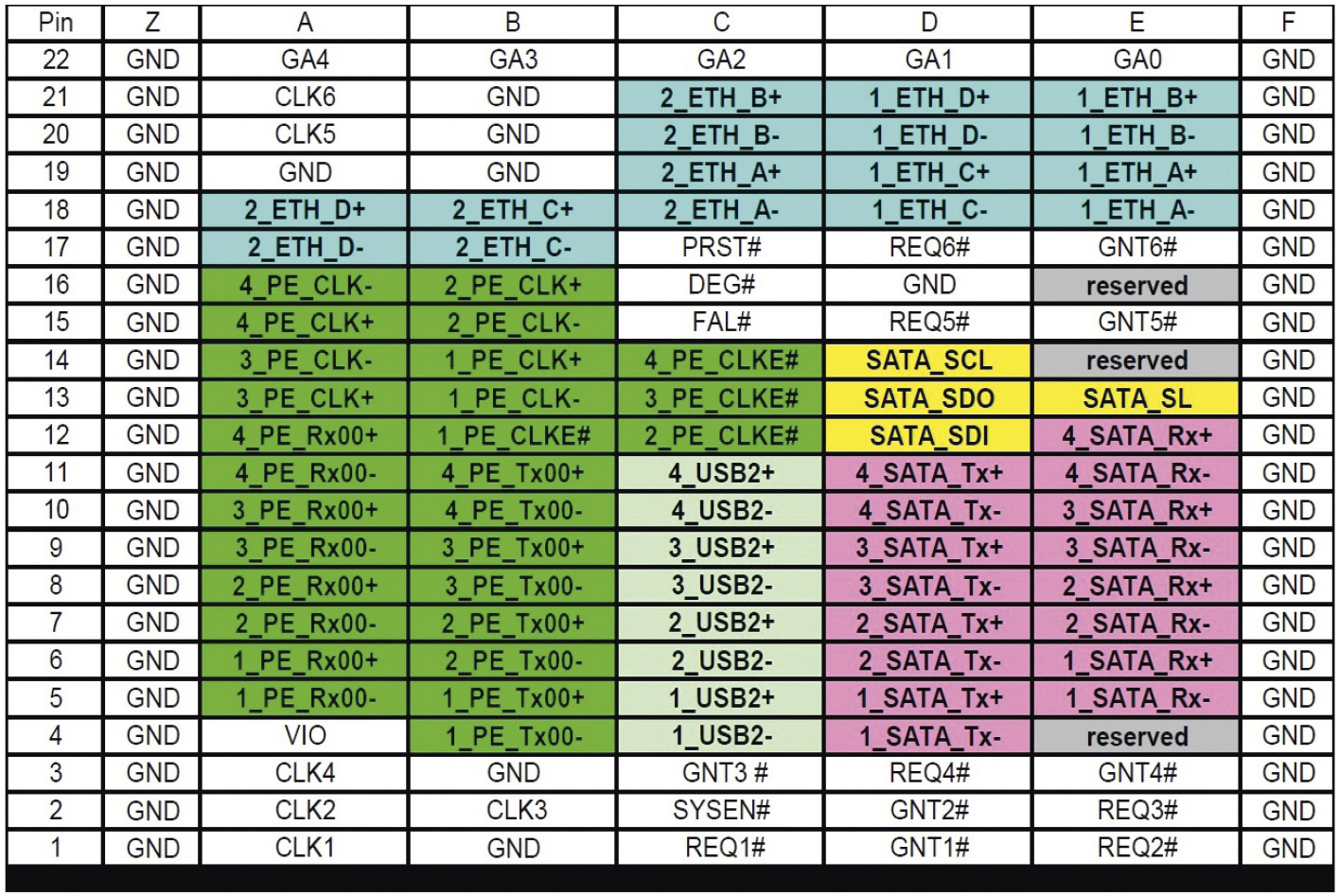

Основная идея этой спецификации, заключающаяся в преемственности с наработками PICMG 2.0 и возможности использования современных последовательных интерфейсов, технически решена исключительно красиво. Как мы помним, по спецификации PICMG 2.0 функциональное назначение части контактов на разъёме J2 плат CompactPCI остаётся на усмотрение разработчиков. Эти контакты и задействованы для теперь уже «законного» определения их под конкретные последовательные интерфейсы (2 канала Ethernet, по четыре канала PCIe, SATA, USB). Чёткое распределение ранее свободных контактов (рис. 5) снимает только часть вопросов.

Главный же вопрос – необходимость увеличить полосу пропускания соединителя (до 5 Гбит/с) и при этом обеспечить механическую совместимость с разъёмами базовой спецификации PICMG 2.0 – решается за счёт использования разъёма нового типа Ultra Hard Metric (UHM) UHM-S110B3-5AP1-TG30 или UHM-S110B3-5AP1-KR от компании 3M. Сигнальные линии Ethernet разводятся на разъёмы типа REC AirMax 4PAIR 8WAFER. Так как разъём J2 присутствует и для вариантов 6U-исполнения процессорных плат CompactPCI, то, конечно же, нововведение может быть поддержано и этим форм-фактором. Стоит обратить внимание, что, в отличие от спецификации CompactPCI PICMG 2.0, платы расширения в новой спецификации имеют соединители-вилки, а ответные розетки устанавливаются на бекплейне. В случаях, если по каким-либо причинам при установке в системный каркас контакт на периферийной плате «замялся», это не потребует вывода из работы всего блока.

В спецификации даются рекомендации по распределению сигналов на разъёмах при разработке бекплейнов с четырьмя, тремя, двумя и одним слотом расширения. Пример того, как может быть спроектирована гибридная система с четырьмя слотами, показан на рис. 6.

Несмотря на «детский возраст» принятой спецификации, на текущий момент ряд фирм уже предлагает продукцию для построения законченных систем с поддержкой спецификации PICMG 2.30 CompactPCI PlusIO. Так, например, известный производитель компонентов евромеханики фирма Schroff выпустила системный блок в конструктиве 19" с гибридной объединительной панелью (4 слота CompactPCI PICMG 2.0, 4 слота CompactPCI 2.30 PlusIO) и блоком питания (рис. 7).

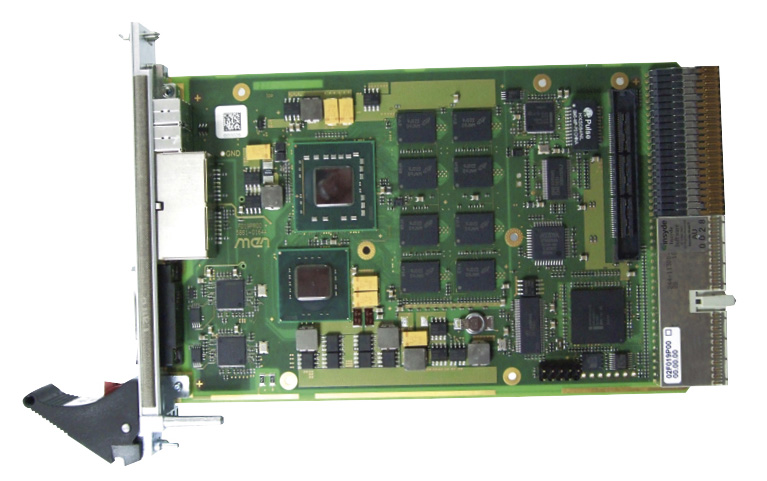

Известный производитель процессорных плат, плат ввода-вывода, а также законченных решений для магистрально-модульных систем компания MEN Mikro Elektronik GmbH предлагает процессорную плату F19P формата 3U CompactPCI PlusIO (рис. 8) с процессором Intel Core 2 Duo.

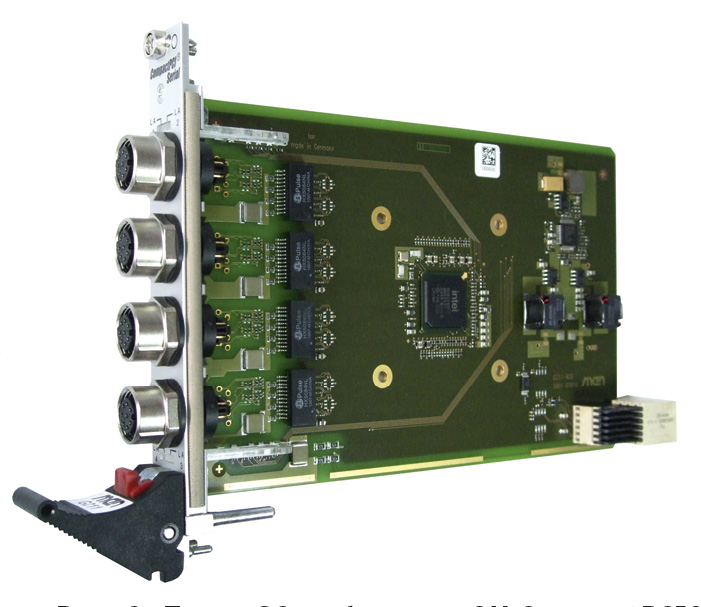

В качестве плат расширения в формате 3U CompactPCI Serial, которые можно установить в гибридную систему, могут быть задействованы две платы носителей MiniCard (G212), XMC 3U (G213), носитель SATA HDD (G501) и плата 4 каналов Gigabit Ethernet (G211) этого же производителя (рис. 9).

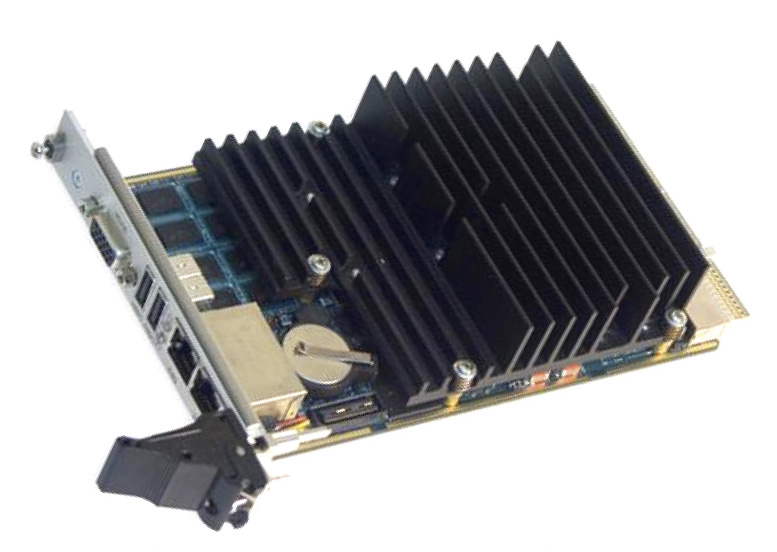

Приятно, что и отечественные производители в лице компании «Доломант», отвечая потребностям времени, разрабатывают изделия актуальных спецификаций. Предлагаемый «Доломантом» процессорный модуль CPC506 (рис. 10) разработан на базе процессоров семейства Intel Сore 2 Duo с частотами 1,0, 1,6 и 2,2 ГГц (долгосрочная производственная программа), системной шиной 800 МГц и набора логики 965GME/ICH8M в соответствии со стандартом PICMG 2.30 CompactPCI PlusIO.

Вывод

Нет сомнения, что возможность «мягкого» перехода от традиционных решений CompactPCI с параллельной шиной к последовательным, используя гибридные технологии PICMG 2.30, позволит во многих приложениях существенно оптимизировать функциональную нагрузку и динамику обмена между подсистемами, максимально задействуя при этом старые наработки аппаратного и программного характера. Одновременно это создаст отработанную материальную основу в виде плат следующего поколения систем CompactPCI, в которых будут применяться только последовательные интерфейсы (PICMG CPCI-S.0). ●

Автор – сотрудник фирмы ПРОСОФТ

Телефон: (812) 448-0444

E-mail: info@spb.prosoft.ru

Если вам понравился материал, кликните значок - вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал - не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!