Технология обмена данными PCI Express (PCIe) повсеместно используется в устройствах, требующих высокопроизводительных, ускоренных вычислений, подключения сетевых карт и графических ускорителей, но не исчерпывается только этим. Обладая преимуществом в высокой скорости передачи данных перед параллельными шинами PCI, PCI-X и AGP, а также низкой задержкой (временем использования шины периферийным устройством), интерфейс PCIe получил широкое распространение в построении иерархических структур хранения данных (например, подключения ОЗУ и DRAM через слоты PCIe с поддержкой протокола внутрисистемных соединений CXL (Compute Express Link) на базе PCIe 5.0.

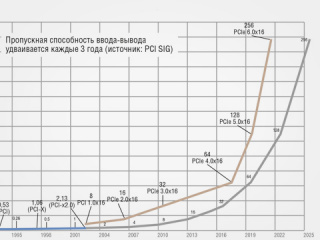

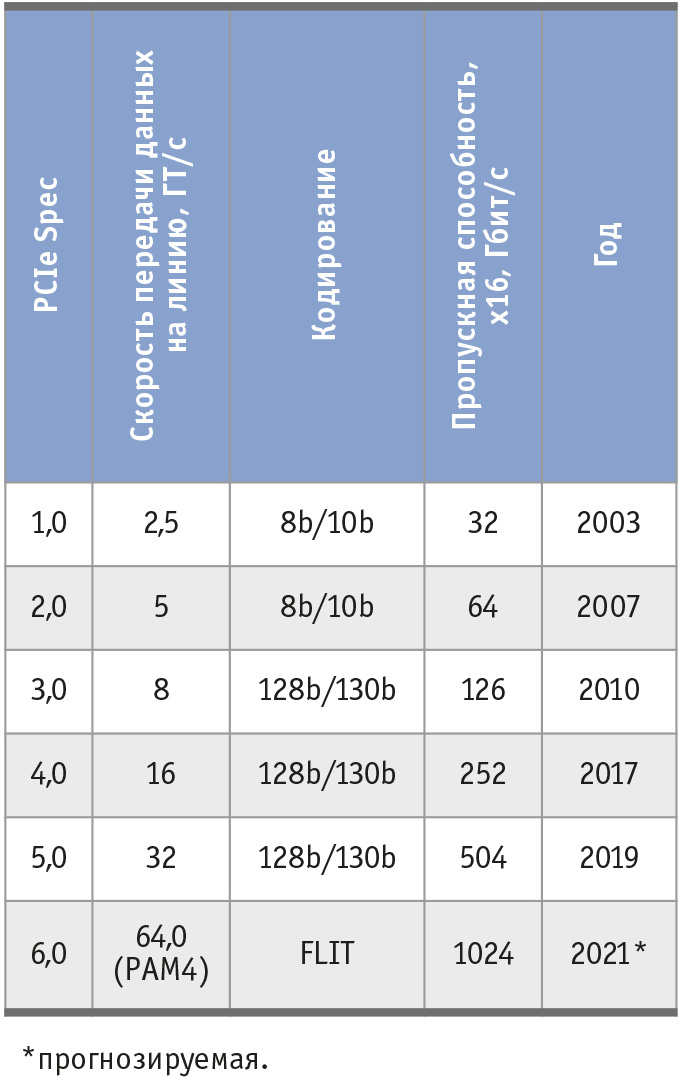

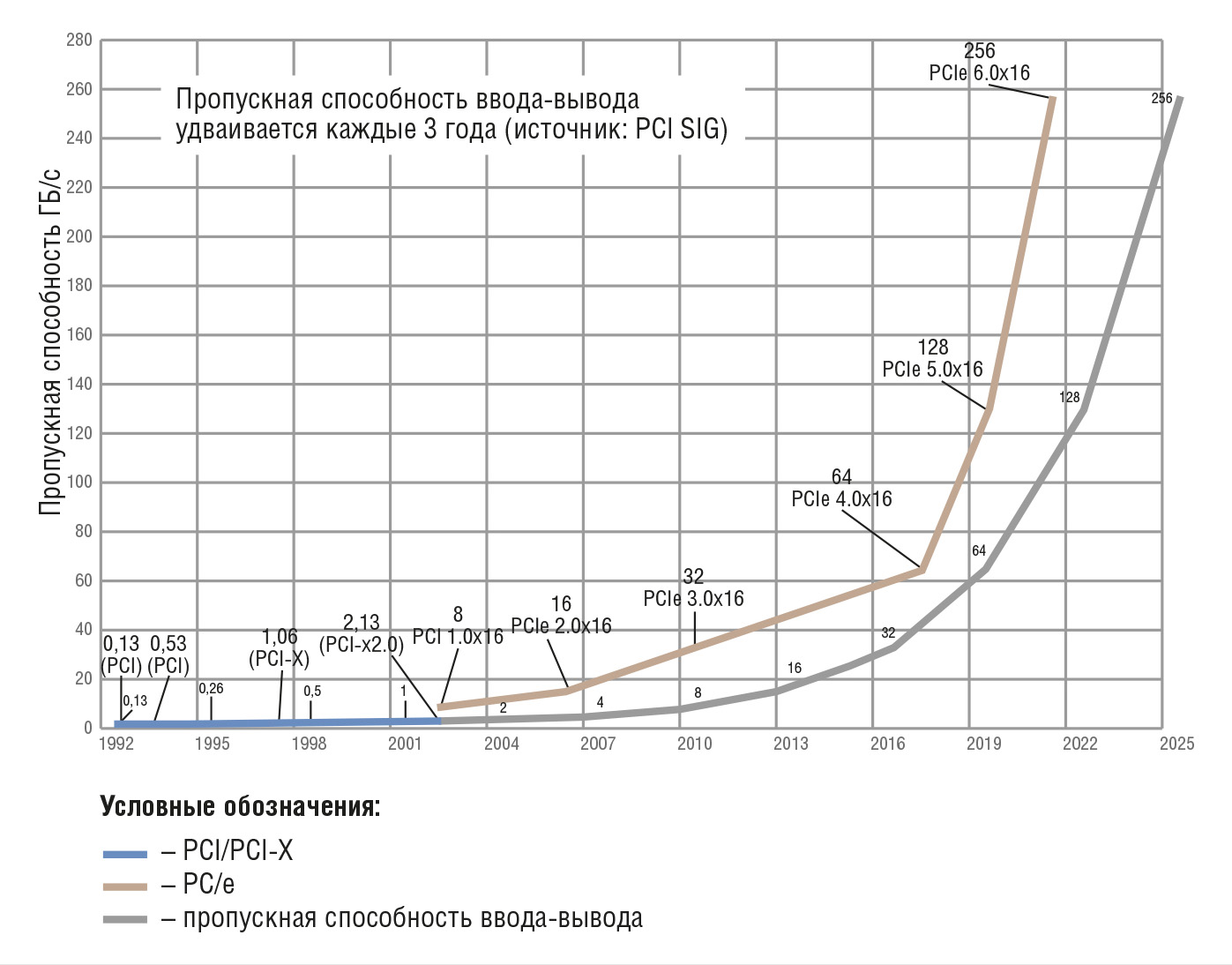

Каждые три-семь лет скорость передачи данных PCI Express при сохранении обратной совместимости с предыдущими поколениями PCIe удваивалась (см. табл. 1).

Разработка приложений искусственного интеллекта (AI – Artificial intelli-gence) и машинного обучения (ML – Machine Learning), построение высокопроизводительных серверных систем и организация облачных вычислений продолжают способствовать генерации трафика гигантских объёмов феноменальными темпами. Стараясь соответствовать непрерывно растущим запросам на увеличение скорости обмена данными между процессором и компонентами, установленными на плате (GPU, FPGA, память), консорциум PCI-SIG (PCI Special Interest Group) представил предварительную версию спецификации PCIe 6.0 со скоростью передачи данных до 64 ГТ/с, окончательное утверждение которой ожидается к концу 2021 года (рис. 1).

Рассмотрим подробнее новую версию интерфейса и его реализацию.

Главная проблема PCIe 6.0

Чтобы избежать дорогостоящей модернизации инфраструктуры, новый интерфейс должен соответствовать требованиям обратной совместимости с предыдущими спецификациями, например, электрические параметры устройств нового поколения PCIe 6.0 должны соответствовать более старым версиям на объединительной плате (например, поддерживать скорость передачи данных до 28 Гбит/с). Требование механической совместимости разъёмов PCIe не позволяет увеличивать количество линков для увеличения пропускной способности.

В спецификации PCIe 5.0 используется моделирование цифровых сигналов кодированием без возврата к нулю (NRZ, no-return-to-zero). При этом искажение сигнала для каналов может достигать 36 дБ (частота Найквиста, равная половине частоты дискретизации, при частоте тактирования 32 ГГц составляет 16 ГГц). При удвоении скорости передачи данных с 32 ГТ/с (гига-транзакций в секунду) до 64 ГТ/с кодированием без возврата к нулю частота Найквиста равна 32 ГГц, при этом частотно-зависимые потери канала увеличиваются до 70 дБ [1].

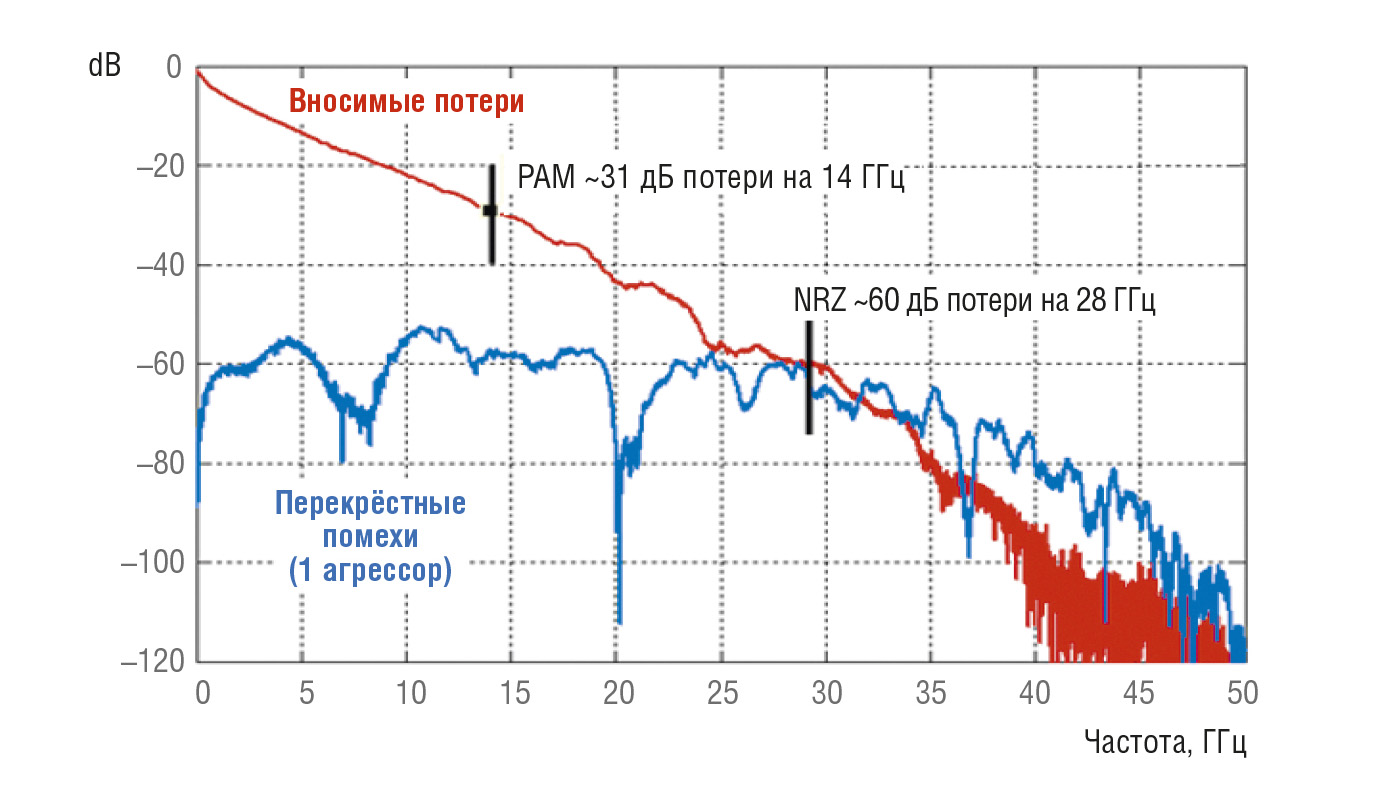

Таким образом, если пропускная способность будет увеличиваться за счёт увеличения частоты, например, до 56 ГГц, вносимые потери IL (Insertion loss) на частоте Найквиста (28 ГГц) составляли бы ~60 дБ, а отношение вносимых потерь сигнала IL к перекрёстным помехам (ICR – incertion-loss-to-crosstalk ratio) при этом стремилось бы к нулю. Это обстоятельство делает невозможным увеличение скорости передачи данных до 56 Гбит/с традиционным методом повышения частоты квантования (дискретизации). Удвоение скорости передачи данных вносит в сигнал существенные искажения, даже если речь идет о небольшом расстоянии, на которое передаётся сигнал.

Частота передачи сигнала свыше 32 ГГц делает его более нестабильным, практически неотличимым от шума.

Переход на PAM4-кодирование

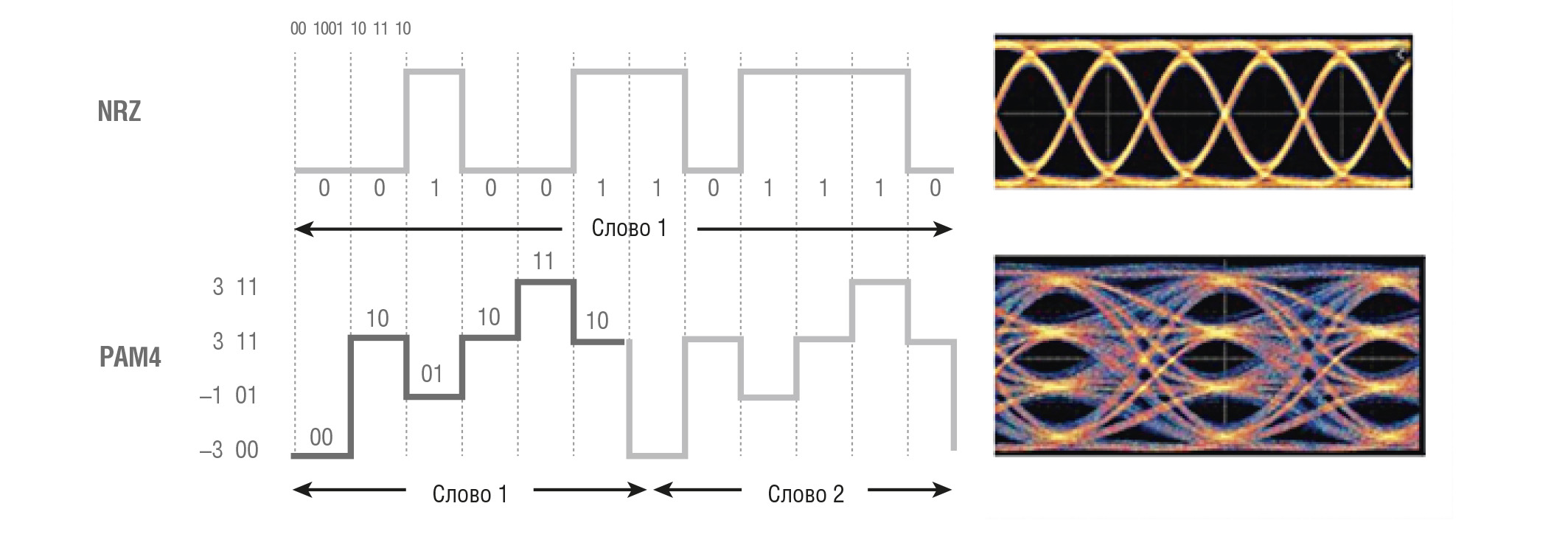

Новая ревизия интерфейса PCIe использует вместо NRZ-кодирования 4-уровневую амплитудно-импульсную модуляцию (PAM4), основанную на использовании не 2, а 4 значений напряжения, и передаёт 2 бита за минимальный интервал времени между изменениями состояния сигнала (Unit Interval), в отличие от кодирования без возврата к нулю, которое передаёт только 1 бит за тот же интервал (рис. 2).

Этот метод передачи сигнала позволяет увеличить пропускную способность PCIe 6.0 в 2 раза, поддерживая искажение сигнала на том же приемлемом уровне, что и в предыдущей версии стандарта PCIe 5.0.

На рис. 3 хорошо заметно, что для канала PAM4 вносимые потери IL составляют ~31 дБ, перекрёстные ICR – ~30 дБ на частоте 14 ГГц. Также можно заметить, что значения вносимых IL и перекрёстных ICR помех при моделировании сигналов NRZ (канал на объединительной плате предыдущих версий стандарта) на частоте 28 ГГц составляют 60 дБ.

Однако преимущество новой сигнальной структуры PAM4 обходится дорого: запас помехоустойчивости для PAM4-кодирования снижается на 9,5 дБ (33%). Это усугубляет неблагоприятное воздействие отражённого сигнала и шумов от источника питания.

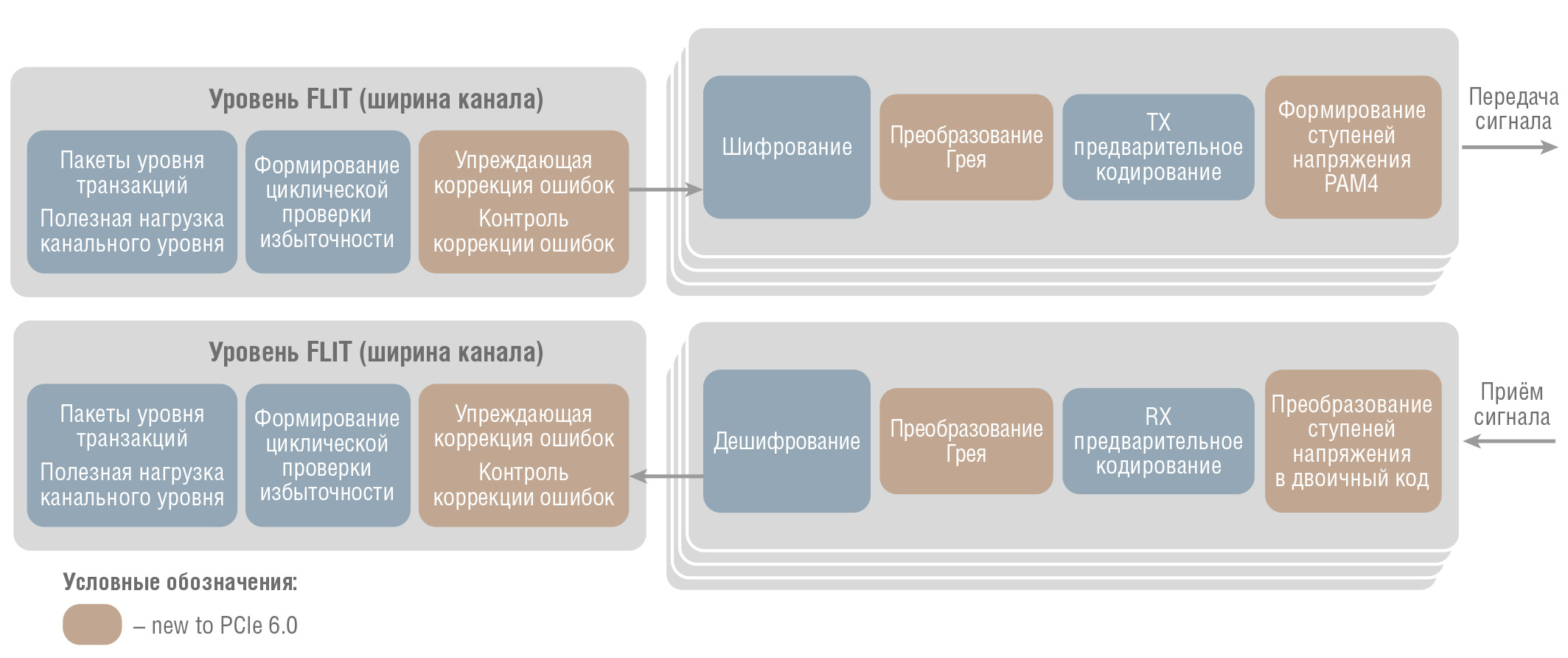

FEC и код Грея

Несмотря на то что в интерфейсе PCIe 6.0 удвоена скорость передачи данных за счёт использования PAM4-кодирования, пониженное соотношение сигнал/шум (SNR – signal-to-noise-ratio) делает его более восприимчивым к помехам по сравнению с кодированием NRZ, способствует высокой частоте битовых ошибок и может привести к сбоям в работе системы или снижению производительности. Метод восстановления целостности сигнала в стандарте PCIe 6.0 – упреждающая коррекция ошибок FEC (forward-error-correction) – предусматривает отправление избыточных данных вместе с полезными при условии, что частота ошибок ниже определённого порогового значения. Циклическая проверка избыточности (CRC – cyclic redundancy check) выполняется для обнаружения и исправления битовых ошибок, если CRC обнаруживает ошибки после FEC, запускается механизм повторной проверки.

Также в качестве повышения помехоустойчивости сигнала в PCIe 6.0 применяется двоичный циклический код (код Грея). Код Грея оперирует самым старшим битом (MSB – most significant bit) и самым младшим битом (LSB – least significant bit) таким образом, чтобы ошибка, вызванная электрическими помехами, приводила максимум к ошибке в одном разряде (рис. 4).

Предыдущие поколения PCIe поддерживали режим экономичного энергопотребления за счёт динамического изменения ширины канала. PCIe 6.0 вводит режим экономии энергопотребления L0p (Low Power State), который позволяет изменять потребляемую мощность пропорционально пропускной способности без прерывания трафика.

В спецификации PCIe 6.0 предусмотрено кодирование на основе блока управления потоком FLIT (Flow Control Unit) для обеспечения меньшей величины задержки, связанной с применением алгоритмов FEC и CRC. Таким образом, добавление вышеуказанных механизмов самокоррекции в PCIe 6.0 не должно существенно увеличивать задержку (латентность) по сравнению с версией PCIe 5.0.

Рабочая группа PCI-SIG доказала, что для PCIe 6.0 её уровень не превышает 10 нс (рис. 5).

Линейность

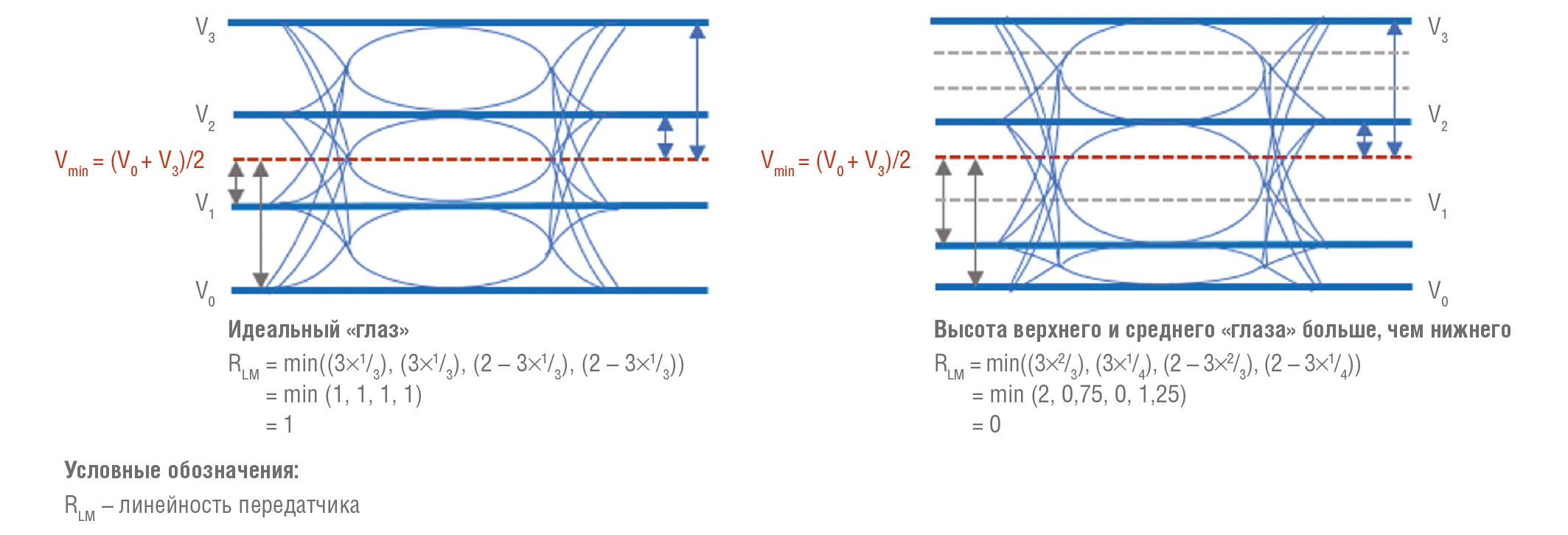

Для метода PAM4 характерен так называемый эффект нелинейности, хорошо видимый на глаз-диаграмме (рис. 6). В левой части приведена идеальная линейность, для которой высоты разделения уровней одинаковы. Интервал между V1 и Vmin составляет одну треть интервала между V0 и Vmin. Аналогичным образом расстояние между V2 и Vmin составляет одну треть от расстояния между V3 и Vmin. В идеальном случае коэффициент рассогласования расстояния между уровнями RLM равен 1. Чем ближе реальный показатель RLM к 1, тем лучше линейность.

Для примера на правой части рис. 6 показан «глаз» с плохой линейностью – уровень сигнала V1 и V2 настолько низок, что интервал между V1 и Vmin составляет две трети от V0 до Vmin, а интервал от V2 до Vmin равен всего одной четверти интервала между V3 и Vmin. В этом случае расчётный показатель RLM равен 0.

Выравнивание амплитудно-частотной характеристики и усиление сигнала могут внести такие искажения, что два уровня напряжения из четырёх будут зафиксированы приёмником сигнала как один. В целом недостаточная линейность, описанная правой частью глаз-диаграммы (рис. 6), приводит к неустранимым битовым ошибкам [2].

Заключение

Переход на 4-уровневую импульсно-амплитудную модуляцию (PAM4) сигнала в настоящий момент является оптимальным средством увеличения пропускной способности при условии сохранения совместимости линков и приемлемого соотношения сигнал/шум.

Несмотря на то что целый ряд задач ещё ждёт своих решений от разработчиков PCI-SIG, параметры помехоустойчивости новой спецификации интерфейса соответствуют возможностям современных приёмопередающих уст-ройств PCIe 6.0, что обеспечит центрам обработки данных, телекоммуникационным и другим системам с повышенными требованиями к пропускной способности скорость передачи данных до 64 Гбит/с на линию. ●

Литература

1. Whitepaper: Pushing the Envelope with PCIe 6.0: Bringing PAM4 to PCIe, Tony Chen, Candence. [Электронный ресурс] // URL: https://www.cadence.com/content/dam/cadence-www/global/en_US/documents/tools/ip/design-ip/pushing-the-envelope-with-pcie-6-wp.pdf.

2. AN 835: PAM4 Signaling Fundamentals Intel. [Электронный ресурс] // URL: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/an/an835.pdf.

Если вам понравился материал, кликните значок - вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал - не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!