На текущий момент, наверное, никто не будет оспаривать тезис, что стрелка выбора базовой системной шины в промышленных компьютерах и встраиваемых решениях в системах автоматизации уверенно показывает на «вариации» шины PCI. Нельзя не заметить и то, что существующие на сегодняшний день требования к объёму обрабатываемой и передаваемой информации даже в системах управления общего назначения существенно возросли. Это обусловлено повышением требований к «качеству» обрабатываемой информации и связано не только с увеличением числа каналов обработки, но и, как правило, с необходимостью передачи больших массивов данных при обработке аудио- и видеоинформации. При этом требования к надёжности систем общего назначения неизменно увеличиваются, не говоря уже о системах управления для атомной энергетики или о системах для оборонного комплекса, в частности ВМФ. В то же время достаточно остро стоит вопрос снижения стоимости оборудования. В этой ситуации стандарт CompactPCI, являющийся интегральным воплощением лучшего из области технологий несущих конструктивов и магистральной системной шины на основе спецификации PCI, становится объективно востребованным техническим решением. Данная статья не ставит целью сделать очередную попытку сравнения CompactPCI с другими архитектурами (частым противопоставлением CompactPCI является VME) и убедить читателя в превосходстве архитектуры CompactPCI, речь идет о кратком изложении ключевых основ (описанию стандарта в целом посвящено немало статей) и текущего состояния этого стандарта с акцентом на те технические моменты, которые в своей идеологической основе позволяют обеспечивать решение возросших технических требований к информационно-управляющим системам, в том числе освещены и моменты, определяющие надёжность.

Отличный «генофонд»

Стандарт CompactPCI совместим со спецификацией PCI v2.1.

Что хорошего досталось от «родителя»?

-

Открытая многоплатформенная спецификация и, как следствие, независимость от типа используемого процессора и операционной системы, доступность элементной базы от большого числа независимых производителей.

-

Синхронная 33/66 МГц, с разрядностью 32/64 бита адреса/данных (A/D) шина с обеспечением контроля чётности.

-

Параллельная мультиплексируемая шина (A/D).

-

Иерархическая масштабируемость шины посредством PCI-мостов.

-

Поддержка автоконфигурирования (PnP).

-

Возможность организации мультимастерных систем.

Что стоит за открытой спецификацией? Серьёзное коллегиальное обсуждение проекта, как правило, гарантирующее выверенное и развивающееся техническое решение. Кроме того, это поддержка элементной базы многими производителями и, как объективное следствие, снижение себестоимости этой шины. Можно ли говорить, что у шины PCI удачная судьба? Безусловно! На текущий момент это самая востребованная шина в промышленной автоматизации, и надёжность этого технического решения подтверждена временем. Как один из «индикаторов», подтверждающих этот факт, можно назвать тотальный перевод компанией Advantech вновь разрабатываемых и поставляемых периферийных плат ввода-вывода на эту шину. За этим шагом стоит сухая прагматичная статистика.

Синхронность (читай — детерминированность) в любом случае работает на надёжность, так как позволяет просчитывать возможный временной баланс на шине.

Конечно, за всё нужно платить, и поэтому выдвигают жёсткие требования по рассогласованию линий CLK (отдельный подвод к каждому разъёму, так как рассогласование при частоте шины 33 МГц — не более 2 нс, для 66 МГц — не более 1 нс).

Вспомним и пропускную способность шины: умножим разрядность на частоту и получим 132/264 Мбайт и 264/528 Мбайт для возможных сочетаний частот и разрядности шины. Конечно, это теоретически максимально возможные величины, накладные расходы шины уменьшают реальные значения, и всё же это серьёзные показатели (при потоковых передачах) по отношению к значениям шины ISA. Но самым важным моментом спецификации PCI, отражённым в пункте 2, который, на мой взгляд, как-то часто остается в тени, является контроль чётности (используются сигналы шины PAR и PAR64). Эта «встроенная» возможность является одним из основных моментов, обеспечивающих высокую надёжность (достоверность данных) высокоскоростной шины PCI.

Технология мультиплексирования параллельной шины позволяет даже в случае использования 64-битовой шины A/D разрабатывать компактные решения (3U CompactPCI).

В автоматизации возможность масштабирования технического решения почти всегда является необходимым качеством грамотно спроектированной системы.

Системы c шиной PCI масштабируются путём использования мостов (PCI-to-PCI Bridge).

Понятно, что в силу необходимости выдерживания определённых временных диаграмм наращивание, в принципе, не может быть бесконечным процессом, но на текущий момент существуют системы с числом слотов 20.

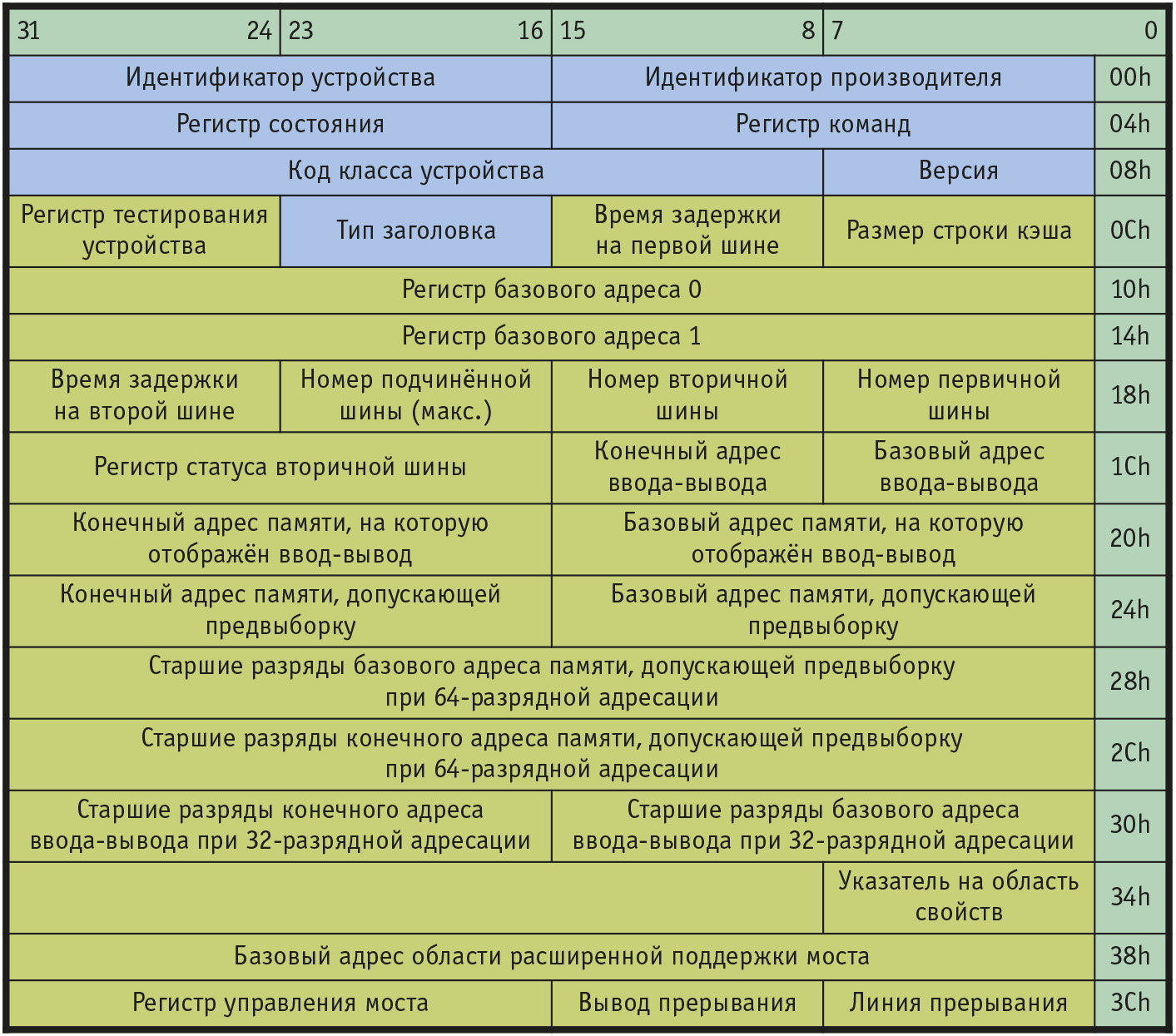

В шину PCI в силу архитектурных и программных требований спецификации заложены возможности конфигурирования (перераспределения) системных ресурсов, к которым относятся пространство адресов памяти, ввода-вывода и самый дорогой системный ресурс – прерывания. Независимый от аппаратной реализации механизм управления шиной PCI обеспечивается вызовом соответствующих функций PCI BIOS. В основном функции PCI BIOS (функции 0B1xxh, прерывание 1Ah) обеспечивают работу с конфигурационным пространством шины PCI (порядка 10 функций) и генерацию специальных циклов на этой шине (0B106h). Заголовок конфигурационного пространства устройства (функции) PCI изображён на рис. 1.

На рис. 1 голубым цветом выделена область заголовка конфигурационного пространства, обязательная для всех устройств, она присутствует всегда и не зависит от типа устройства. Зелёным цветом выделена область, значение которой определяется функциональностью конкретного устройства (определяется значением поля тип заголовка/Header Type: 0 – устройство, 01 — стандартный мост PCI-to-PCI, 02 – мост к одному из интерфейсов карт расширения) и розовым цветом — область, определяемая пользователем.

Чётко формализованный алгоритм автоконфигурирования (речь идёт о технологии PnP), безусловно, является положительным фактором, так как минимизирует требования к операционной системе (ОС), связанные с вопросами распределения системных ресурсов. В то же время поддержка в PCI BIOS всех необходимых режимов управления шиной PCI даёт возможность гибко подходить к этому вопросу и при необходимости позволяет ОС перераспределять области ввода-вывода и памяти с учётом специфики конкретной ОС. Для более точного понимания специфики положения, описанной в п. 6, необходимо подробнее напомнить основные детали архитектуры шины PCI и связанные с ней особенности инициализации систем на её основе.

Шина PCI (Peripheral Component Interconnected Local Bus) — это локальная шина, соединяющая периферийные компоненты. Подчеркнём, что понятие компонента включает в себя как микросхемы, напаянные на системной плате и являющиеся неотъемлемой её частью, так и дополнительные устройства, устанавливаемые в слот шины. Иногда при отсутствии разъёмов на плате разработчики как-то упускают из вида наличие этой внутренней шины на процессорной плате, а от её характеристик порой зависит, насколько полно система может обеспечить потенциальные возможности важнейших, например, коммуникационных характеристик процессорной платы. Если чип Gigabit Ethernet подключён к центральному процессору через шину PCI с разрядностью 32 бита и частотой 33 МГц, то скорее всего при обмене по этому интерфейсу вы не получите заявленных характеристик скорости канала Ethernet. Внутренняя шина будет принципиально «узким местом» и не позволит получить желаемые величины Гбит/с, даже если пользовательская программа будет заниматься только обслуживанием этого коммуникационного канала. Это лирическое отступление связано с большим потоком вопросов и необходимостью разъяснений именно данной ситуации. Продолжим. Каждая физическая шина PCI может объединять определённое количество устройств (задано спецификацией и для PCI равно 4), которые, в свою очередь, могут иметь несколько функций, как минимум, одну (её номер 0). Для увеличения количества устройств, подключённых непосредственно к этой шине, используется микросхема моста шины PCI (PCI-to-PCI Bridge). Мосты шины используются и в тех случаях, когда на одной плате, установленной в слот шины PCI, находится несколько микросхем (контроллеров), что равносильно увеличению числа устройств на шине PCI. В некотором приближении можно считать, что это «повторитель» шины PCI (это понятие знакомо большинству инженеров), хотя такое упрощение специфицирует только физическую часть интерфейса (мост — интеллектуальное, программно конфигурируемое устройство), и потому далеко не полным. Кроме того, если речь идёт именно об увеличении числа слотов для дополнительных устройств на шине PCI, то говорят о равноранговых мостах Peer-to-Peer Bridge, так как существуют мосты, выполняющие функции преобразования интерфейса, например, мост PCI-to-ISA/EISA. Шина PCI соединяется с ядром системы (процессор и память) посредством главного моста (Host bridge). В системе может существовать не одна цепочка шин PCI, объединённых мостами, но с ядром системы все они соединяются через главный мост (главных мостов в системе может быть несколько, но мы сейчас не будем останавливаться на этих случаях). Таким образом, в образованной древовидной иерархической структуре шин PCI в системе существует один «хозяин» (Host) — это вычислительное ядро, в функции которого входит конфигурирование всех подключённых к шине устройств, и в первую очередь мостов. Иерархия, в том числе, выражается в последовательности нумерации шин, которая начинается от главного моста. Каждый мост имеет первичную (Primary bus) и вторичную (Secondary bus) шину. Первичной является шина, расположенная ближе к вершине иерархической структуры (вычислительному ядру). Номером моста является номер вторичной шины. Вторичной шине главного моста (первичная шина соединена с ядром) присвоен номер 0, таким образом, номер главного моста также равен 0. Шины, подключённые к вторичному интерфейсу моста следующим мостом, называются подчинёнными (Subordinated bus). Главный мост, кроме функции «первого верстового столба», служит и целевым устройством при транзакциях на шине PCI, связанных с обращением устройств на шине к системной памяти. В то же время при обращениях центрального процессора к какому-либо устройству на шине PCI главный мост является инициатором (задатчиком) транзакции. Мост (или мосты) является важнейшим организующим элементом шины PCI, и на нём лежит ответственность за выполнение системообразующих функций на вторичном интерфейсе, как-то:

-

формирование аппаратного сброса;

-

поддержка карт ресурсов интерфейсов (рис. 2);

-

маршрутизация транзакций;

-

арбитраж и предоставление права на управление шиной;

-

генерация конфигурационных циклов;

-

определение аппаратных возможностей устройств на шине;

-

в соответствии с маршрутизацией транзакций выполнение роли целевого устройства и далее инициатора транзакций, в случаях когда запрошен обмен между устройствами на разных интерфейсах моста;

-

«парковка» шины.

Ещё одним замечательным качеством мостов является возможность обеспечения и согласования взаимодействия устройств с разными интерфейсами и разными характеристиками частоты (33/66 МГц) и разрядности (32/64 бита). Напомним, что в каждом сегменте шины PCI режим работы выбирается по самому «слабому» устройству, и простая перестановка устройств в слотах системы может существенно увеличить производительность в целом. Как уже говорилось, мосты — это программируемые элементы, и основной блок данных (рис. 2) содержит информацию об адресном пространстве памяти и ввода-вывода устройств обслуживаемой им шины. Эта информация и позволяет конкретному мосту и совокупности всех мостов системы в целом осуществлять маршрутизацию запросов. Наличие мостов, реализующих указанные функции, для участников обмена на разных шинах незаметно, или прозрачно, именно поэтому подобный режим работы (и сами мосты) носит название прозрачного (transparent).

С точки зрения программного обеспечения, важнейшим преимуществом системы, построенной с использованием только прозрачных мостов, является отсутствие необходимости в каких-либо специфических драйверах устройств на шине PCI. Достаточно стандартных, как правило, ориентированных на плоскую модель распределения (не перекрывающихся) адресов памяти и ввода-вывода для устройств в системе.

В системе на основе шины PCI существуют и мосты, работающие в так называемом непрозрачном режиме, которые называются непрозрачными (non-transparent bridge). Как и в случае с прозрачными, название непрозрачные мосты отражает особенность основной функции – трансляции транзакций в соответствии с распределением адресного пространства и пространства ввода-вывода в системе. Непрозрачные мосты работают с раздельным адресным пространством ресурсов (в этом режиме у них две области конфигурационных регистров, в том числе и с разделяемыми регистрами), внутренним и внешним, поэтому при обращении на внешнюю (системную) шину выполняется преобразование адреса. Это свойство непрозрачных мостов служит основой для возможности построения на шине PCI мультипроцессорных систем или интеллектуального ввода-вывода.

CompactPCI: преемственность и отличный генезис

Кратко напомним основные достоинства этой спецификации:

-

совместимость со спецификацией PCI (v. 2.1);

-

дополнительные сигналы, в том числе улучшающие анализ состояния системы (SYSEN#, BD_SEL#, DEG#, FAL#, ENUM# и т.д.);

-

использование еврокарт (форм-фактор 3U и 6U), надёжные 7-рядные разъёмы с шагом контактов 2 мм;

-

на дополнительных разъёмах (или контактах основных разъёмов) возможность организации интеграции со специализированными шинами (например, для CompactPCI 6U шина компьютерной телефонии Н.110);

-

использование как подключения через разъёмы передней панели, так и тыльного ввода-вывода; расширение через мезонины;

-

увеличение до 8 слотов на одном сегменте в системе без использования мостов и до 20 слотов с мостами (на рис. 3 показан пример такой системы — отказоустойчивый корпус 12U MIC-3082A производства компании Advantech);

-

«горячая» замена (Hot Swapping);

-

стандарт PICMG 2.16, достоинства которого будут рассмотрены далее.

Классические методы повышения производительности в системах CompactPCI

Известно, что одним из классических вариантов увеличения производительности системы в целом является разбиение и распределение решаемой задачи между несколькими подсистемами. При этом могут варьироваться варианты разбиения, когда одна из подсистем выполняет только специфическую обработку входных данных и результаты передаются следующей подсистеме, или подсистема решает конкретную задачу целиком. В первом случае имеет место классическая конвейерная обработка данных, второй случай чаще всего совмещается не только с расчётом законченной задачи, но и параллельно c получением входных (исходных) данных для расчётной части этого блока программы. При построении системы по конвейерному принципу необходимо учитывать большую загрузку шины, так как промежуточные расчёты не являются окончательными и имеет место передача между подсистемами больших массивов данных. Второй случай обеспечивает меньшую загрузку шины. Системы CompactPCI являются идеальным вариантом для обеспечения технической реализации классических вариантов построения систем. Нельзя забывать и о программной поддержке этих архитектурных построений, а именно о том, что сама программа должна быть построена по линейному либо модульному принципу. Если речь идёт о конвейерной обработке, то в системе, кроме ведущего процессора, в слоты расширения устанавливаются платы процессоров общего назначения или DSP-процессора. Во втором случае обеспечение установки на процессорные модули (как правило, это полнофункциональные процессорные модули) через расширение PMC (PCI Mezzanine Card) специализированных модулей (например, быстродействующих АЦП) позволяет реализовать распределённый ввод/вывод и локальную обработку с получением конечного результата. Для осуществления распределённого ввода/вывода существуют и специализированные контроллеры интеллектуального ввода/вывода (I2O), построение подобной архитектуры возможно благодаря существованию открытого стандарта, поддерживаемого консорциумом ведущих производителей, как для микросхем самих контроллеров (например, Intel 80960RM I/O Processor), так и для соответствующего программного обеспечения (Microsoft, WindRiver). Шина CompactPCI, проявляющая самые высокие показатели пропускной способности именно при пакетных передачах, отлично подходит для конвейерного варианта, широкий выбор мезонинных модулей расширения гарантирует возможность решения задачи по вводу сигналов с произвольными характеристиками. При этом локальный ввод/вывод с PMC-модулем обеспечивается опять же по скоростной 33/66 МГц 32/64-разрядной шине PCI.

На основе возможности поддержки шиной PCI различных скоростей работы устройств в разных сегментах можно существенно повысить производительность системы, сосредоточив в одном сегменте взаимодействие с оператором (ввод и отображение информации), при этом ведущий процессор сегмента будет работать под операционной системой, отвечающей требованиям графических приложений (Windows 2000/XP), а в другом сегменте (с более высокой скоростью на шине) будет реализована подсистема ввода/вывода, при этом на ведущем процессоре этого сегмента может использоваться операционная система реального времени (Windows CE, QNX).

Сегменты системы соединяются мостом (в качестве которого может выступать и контроллер I2O), обеспечивающим согласование временной диаграммы сегментов при обмене данными. Такой вариант построения максимально эффективно использует пропускную способность шины и позволяет строить аппаратно-программные комплексы, работающие в режиме реального времени.

Возможности и особенности построения надёжных систем на основе CompactPCI

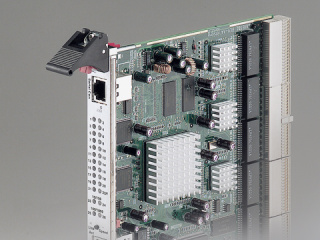

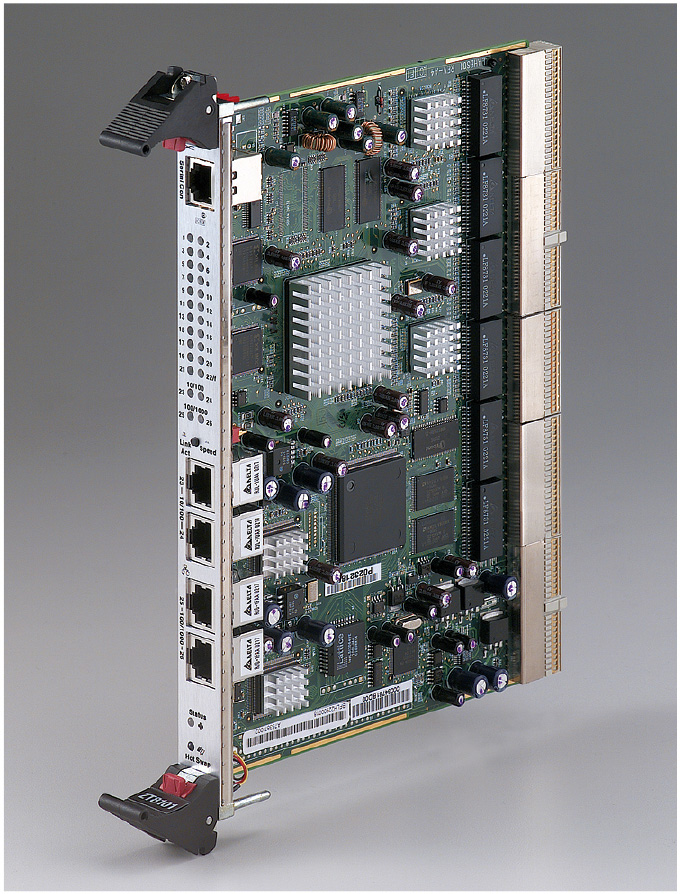

Один из способов повышения надёжности управляющих вычислительных систем базируется на принципах построения более производительной вычислительной системы, в основе которой лежит многопроцессорная мультимастерная система. В разделе, посвящённом базовым характеристикам шины PCI, не зря было уделено столько внимания одному из основополагающих элементов систем на базе шины PCI — мосту. В случае создания многопроцессорной системы ему отводится одна из ключевых функций — исключение конфликтов на шине в момент начальной инициализации всей системы CompactPCI. При подаче питания ведущий процессор (Host) на шине PCI выполняет сканирование шины и инициализацию всех её элементов для обеспечения бесконфликтного разделения системных ресурсов. При наличии в системе не одного, а, скажем, двух равноправных процессоров (второй установлен в периферийный слот системы) совершенно очевидно, что возникла бы конфликтная ситуация. Только наличие непрозрачного моста на процессоре, который изолирует внутренние ресурсы процессора от системных на первичной шине, позволяет избежать этого конфликта. Процессорные платы, для которых указан тип Slave, имеют непрозрачный мост и предназначены именно для установки в периферийный слот. После старта системы (окончания этапа инициализации устройств на шине) процессору Slave доступны установленные в системе платы расширения, но доступ к ним через стандартные драйверы невозможен. В то же время при написании собственного драйвера это вполне осуществимо. Существуют процессорные платы универсального типа (Master/Slave), например, CPC501 — 6U CompactPCI процессорная плата производства Fastwel (рис. 4), которые в зависимости от значения на входе SYSEN# (в системном слоте логический 0) работают в том или ином режиме.

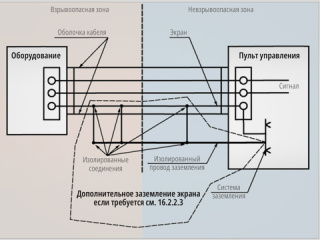

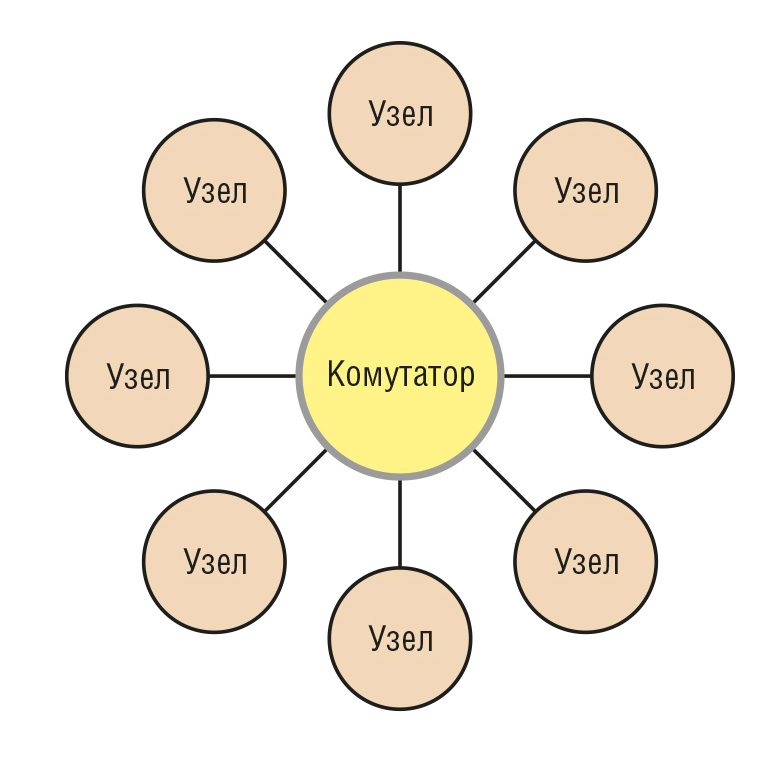

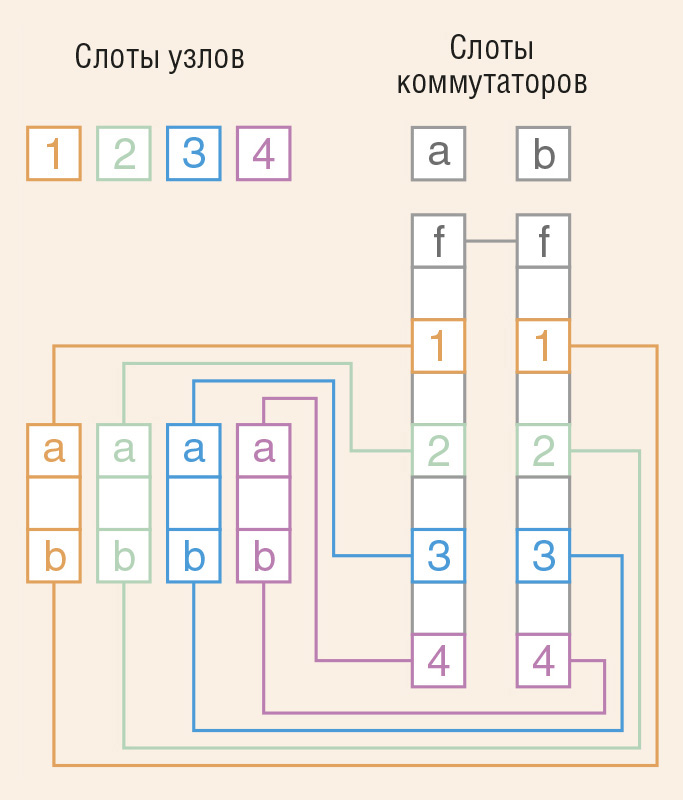

На этих процессорных платах установлен универсальный мост, в случае CPC501 это PCI 6254 (HB6) Dual Mode Universal PCI-to-PCI Bridge, с возможностью работы в двух режимах (прозрачном или непрозрачном). Учитывая обстоятельства изначальной иерархической несимметричности организации системной шины CompactPCI, при которой функции ведущего системного процессора и Slave-процессора различны (синхронизация на шине, обработка прерываний осуществляется из системного слота), говорить о возможности полнофункционального резервирования на одном сегменте вычислителей нельзя. В то же время в общем случае возможно объединение двух сегментов систем CompactPCI через непрозрачный мост с реализацией перекрестного доступа к ресурсам объединённых сегментов и построения надёжной дублированной системы. Доступ к ресурсам через непрозрачный мост может вызвать определённые вопросы у программистов, но есть одно замечательное обстоятельство, которое существенно облегчает задачу внутри- и межсегментного обмена, — речь идет о спецификации PICMG 2.16 (CompactPCI/ Packet Switching Backplane). На мой взгляд, это одно из значительных явлений, можно сказать, революционное, обеспечивающее использование традиционных сетевых технологий на приборном уровне и представляющее собой смелый шаг от традиционных представлений о Ethernet как системообразующем интерфейсе верхнего уровня. Давайте вспомним, о чём идет речь. Стандарт PICMG 2.16 затрагивает вопросы организации системной шины на объединительной панели, основой которой является классическая схема построения Ethernet — сети «звезда» (рис. 5).

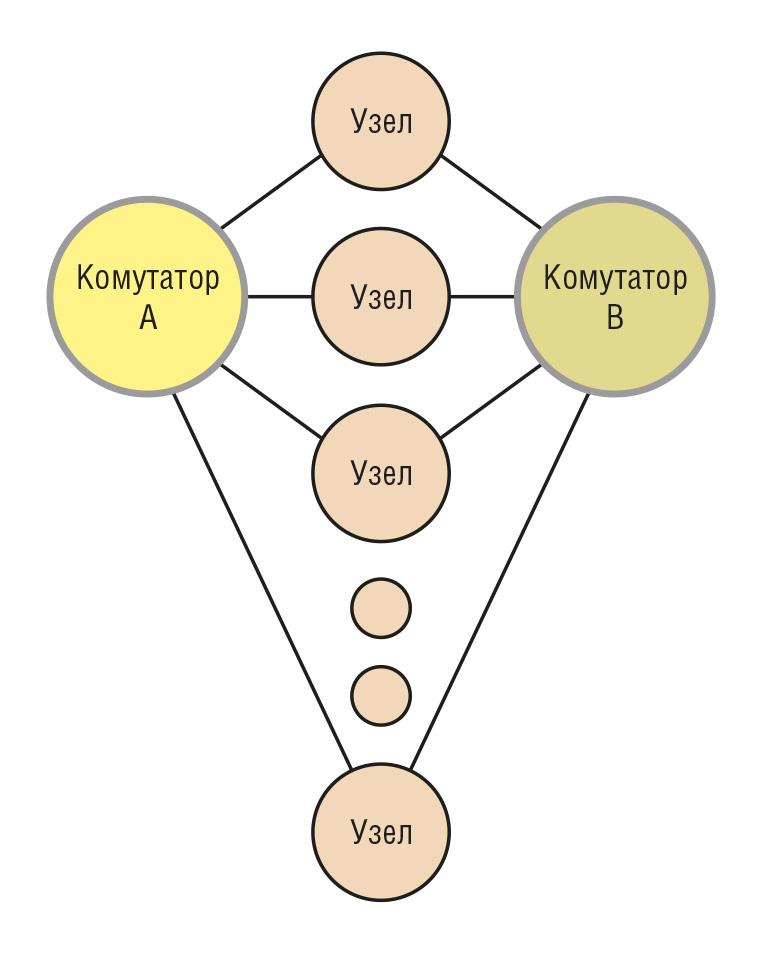

Теперь представим, что каждый узел имеет два канала связи и объединяется не через один коммутатор, а через два, этот вариант соединения изображён на рис. 6.

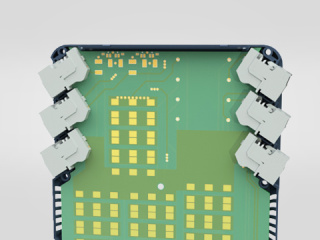

Полученная топология — двойная звезда — обеспечивает избыточность. Собственно, физическая реализация топологии двойной звезды на объединительной панели CompactPCI и является сутью спецификации 2.16. На объединительной панели системы CompactPCI с поддержкой спецификации 2.16 появляются дополнительные слоты, куда устанавливаются коммутаторы. Все слоты узлов на разъёме P3 имеют две группы контактов и соединяются со слотами коммутаторов на печатной плате, образуя дублированную связь Gigabit Ethernet. Для наглядности функциональная схема связи для четырёх узловых слотов и двух слотов коммутаторов приведена на рис. 7.

Полученная локальная сеть на кросс-плате имеет все преимущества стандартной и хорошо известной программистам инфраструктуры на основе Ethernet: простота масштабируемости и возможность решения общей задачи повышения надёжности системы с позиции распределённой архитектуры. Кроме того, имеющаяся сеть лишена наиболее проблемных элементов стандартных сетей Ethernet – протяжённых кабелей и разъёмных соединений. В спецификации 2.16, предусматривающей до 20 Gigabit Ethernet каналов в системе с двумя коммутаторами, выходим на теоретически возможную пропускную способность узла 40 Гбит/с. Большая пропускная способность резервированного канала связи и большое число узлов в одной 19" системе позволяют создавать мощные кластерные системы. Если мы говорим о построении надёжной резервированной системы управления, то при использовании объединительной панели с несколькими независимыми сегментами, поддерживающей спецификацию 2.16, даже на базе одного 19" конструктива можно строить как дублированные, так и троированные системы (есть варианты готовых решений с дублированным источником питания). Передача информации между подсистемами для сравнения входных и выходных данных каждого отдельного сегмента может обеспечиваться по дублированному Ethernet-каналу (плюс ещё один информационный канал через непрозрачный мост). Чтобы подобная система была до конца последовательным надёжным решением, было бы неплохо иметь в арсенале технических средств коммутаторы с цилиндрическими разъёмами с резьбовым сочленением для обеспечения надёжного соединения системы с внешней сетью. Такое решение есть! Это изделие фирмы Fastwel MIC-8101D (на основе изделия MIC-8101-A, рис. 8).

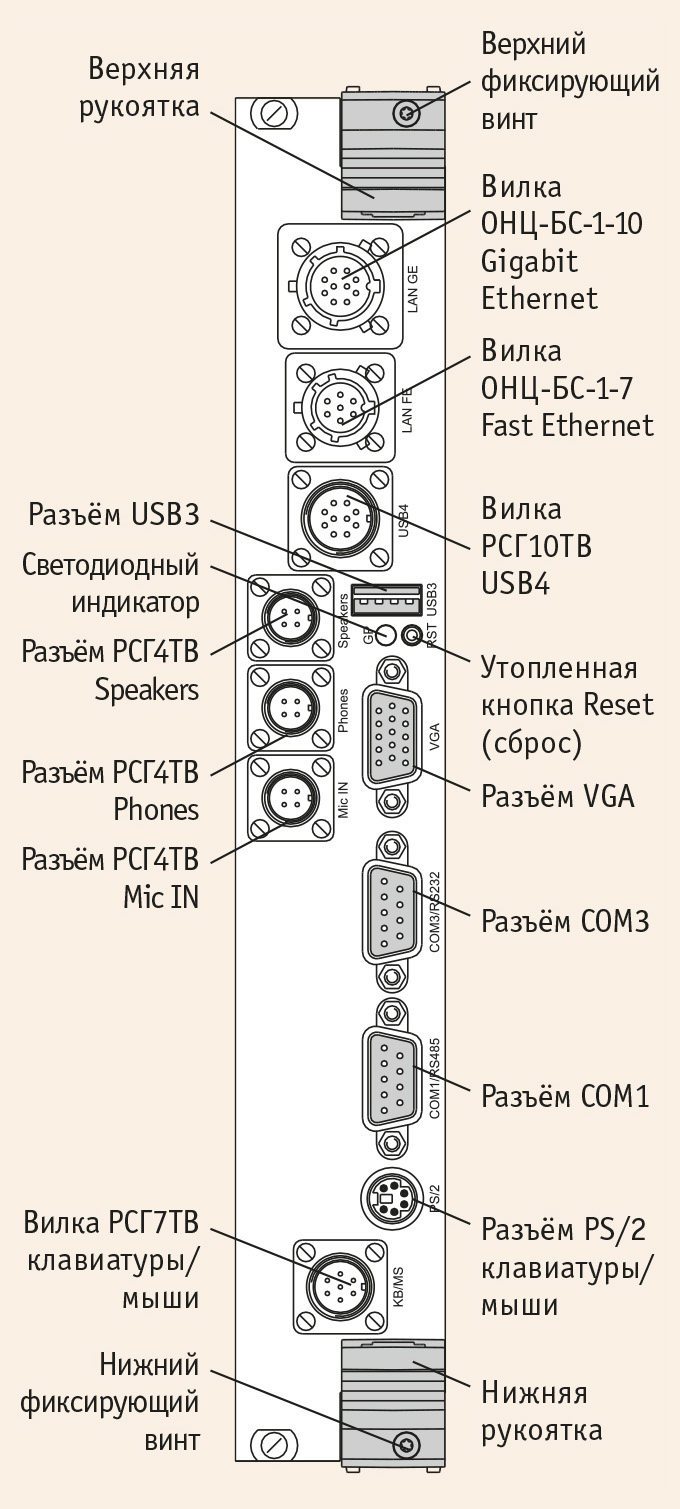

К слову сказать, для процессорных плат фирмы Fastwel CPC501 также существует набор плат тыльного ввода-вывода RIO586 (RIO586-01, рис. 9), где все соединения внешних интерфейсов выполнены, исходя из требований обеспечения жёсткой фиксации, цилиндрическими соединителями с байонетным или резьбовым сочленением.

Оптимистические выводы

Рассмотренные базовые технические характеристики, лежащие в основе спецификации систем CompactPCI, и современные расширения этой спецификации позволяют уверенно говорить о возможности построения надёжных систем с высоким коэффициентом готовности на технических решениях данной платформы. При этом есть возможность практически без изменений перенести и эффективно использовать программные наработки системного уровня и минимизировать затраты на инфраструктуру межблочных коммуникаций. Несмотря на относительную молодость стандарта CompactPCI, технология доказала свою состоятельность и востребованность на рынке технических решений. На текущий момент она имеет в своем арсенале большое разнообразие как процессорных плат, так и плат периферийного ввода-вывода (не говоря уже о возможном использовании PMC-модулей), что позволяет решать практически любую техническую задачу, при этом большое число производителей гарантирует возможность выбора и тем самым возможность ценовой оптимизации проектируемой системы. ●

Автор — сотрудник фирмы ПРОСОФТ

Телефон: (812) 448-0444

Факс: (812) 448-0339

E-mail: valera@spb.prosoft.ru

Если вам понравился материал, кликните значок - вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал - не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!