Предисловие

Уважаемые читатели, коллеги. Первой статьёй о библиотеках HDL-тестов для систем моделирования цифровой аппаратуры мы открываем серию статей по работе с отечественной системой цифрового моделирования. В статьях мы расскажем о развитии системы за последние годы, а также о пользовательском опыте, особенностях и взаимодействии компании и разработчиков ПЛИС и СБИС по оптимизации функциональности системы. Авторы серий статей:

- Малышев Никита Максимович – ведущий разработчик Delta Design Simtera компании ЭРЕМЕКС;

- Поляков Аркадий Константинович – кандидат технических наук, доцент кафедры «Вычислительные машины, системы и сети» Московского энергетического института (НИУ), лауреат премии Фонда развития МЭИ «Почёт и признание поколений», в конце 90-х и начале 2000-х годов – ведущий инженер компаний SEVA и INTRINSIX в Кремниевой долине США.

Благодаря активному взаимодействию авторов на протяжении трёх лет, начиная с выхода первых альфа-версий Delta Design Simtera, накопилось множество материалов, которыми мы решили поделиться и рассказать о сложностях разработки САПР и альфа-тестирования системы.

Введение

Подавляющее число систем цифрового моделирования, базирующихся на HDL-языках описания аппаратуры (VHDL, Verilog, SystemVerilog), разработаны в США фирмами Synopsys, Cadence, MentorGraphics, Xilinx, Aldec и др.

Если в СССР в своё время имелось несколько систем моделирования, базировавшихся на отечественных высокоуровневых языках моделирования цифровой аппаратуры типа МОДИС-ВЕС, Алгоритм и др., то после распада страны в 90-х годах работы в этой области почти не велись.

Система цифрового моделирования Delta Design Simtera (далее Simtera) компании ЭРЕМЕКС [1] является первой из отечественных систем, базирующихся на HDL-языках описания аппаратуры (VHDL, Verilog, SystemVerilog) и их расширениях, ориентированных на моделирование аналоговых систем: Verilog-AMS.

Simtera в самом начале пути своего развития позиционировался как модуль цифрового моделирования в составе программного пакета Delta Design – комплексной среды сквозного проектирования электронных устройств и в том числе печатных плат. Она включает в себя множество отдельных модулей – начиная от ведения библиотек и заканчивая подготовкой данных для производства. Развитие программного пакета Simtera началось ещё в начале 2010-х годов (сам DeltaDesign и топологический роутер TopoR – ещё десятилетием ранее), до первых западных санкций. Тогда Simtera представлял из себя отдельный программный пакет по моделированию VHDL-кода. С тех пор позиционирование этого продукта изменилось в сторону расширения функциональности ввиду спроса и внешних обстоятельств. Это и расширение набора поддерживаемых HDL, и подключение системы синтеза и имплементации проектов на ПЛИС. В настоящее время использовать Simtera можно как отдельно, если мы говорим о проектировании конфигурации ПЛИС и архитектуры микросхем, так и в составе Delta Design – здесь этот модуль можно использовать для моделирования цифровых блоков в составе проектируемого радиоэлектронного изделия.

Одним из важнейших требований к системам, подобным Simtera, является отсутствие ошибок – параметр, зависящий в том числе от полноты тестирования (верификации) и устойчивости в работе.

Библиотека тестов

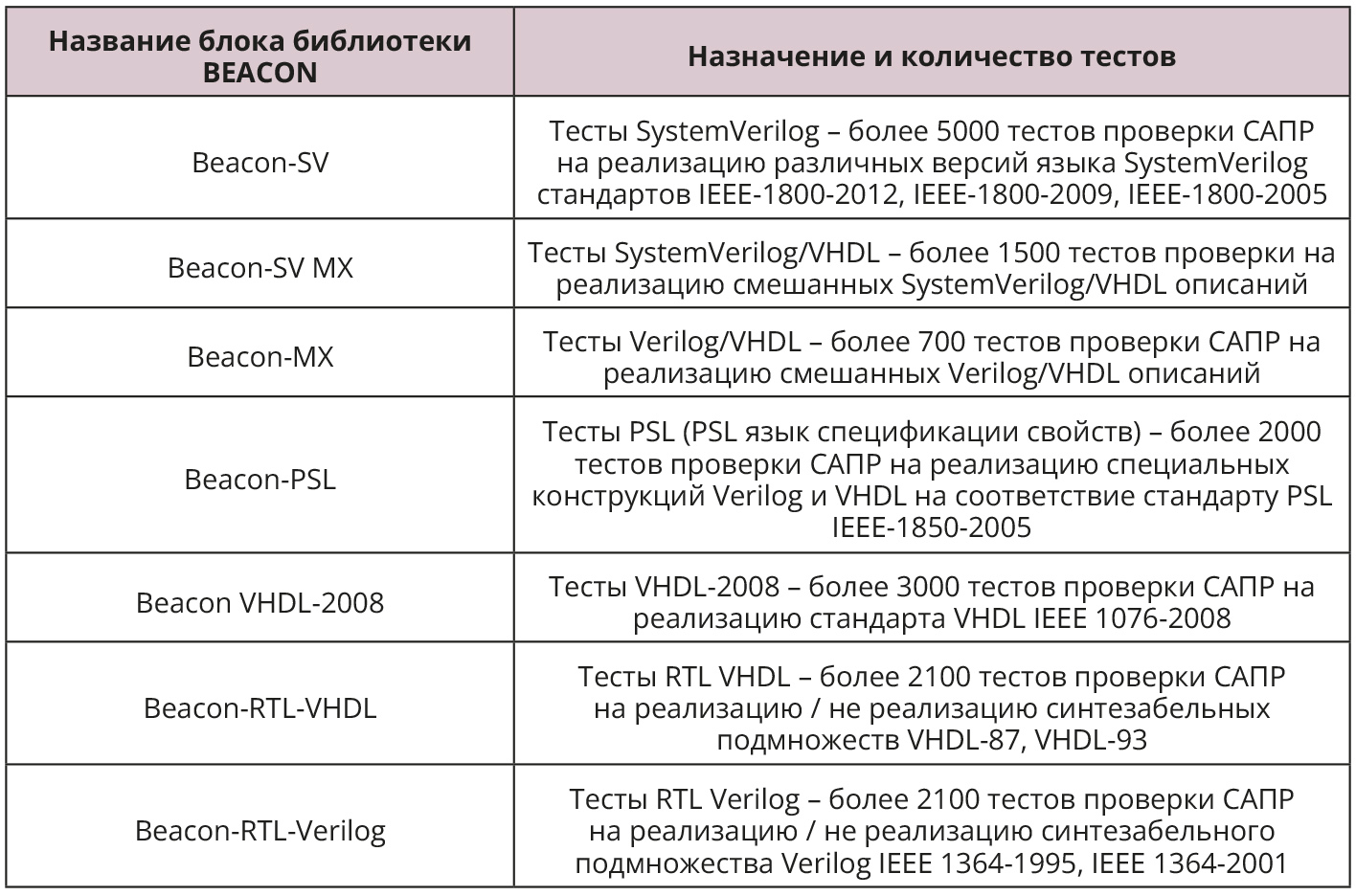

Объём работ, связанных с разработкой библиотек тестов для верификации HDL-систем цифрового моделирования, можно проиллюстрировать параметрами коммерческой библиотеки BEACON компании InterraSystems [2], представленными в табл. 1.

Если считать, что в среднем каждый тест содержит 10–20 строк HDL-кода, то общий объём таких библиотек 200 000–400 000 строк. Следует учесть, что обычно отдельный простой тест проверяет САПР на реализацию только одной из конструкций языка. Соответственно, необходимы наборы более сложных тестов, проверяющих реализацию совокупности конструкций языков, контролирующих предельные размеры HDL-описаний, объём занимаемой моделями памяти инструментальных ЭВМ и т.п.

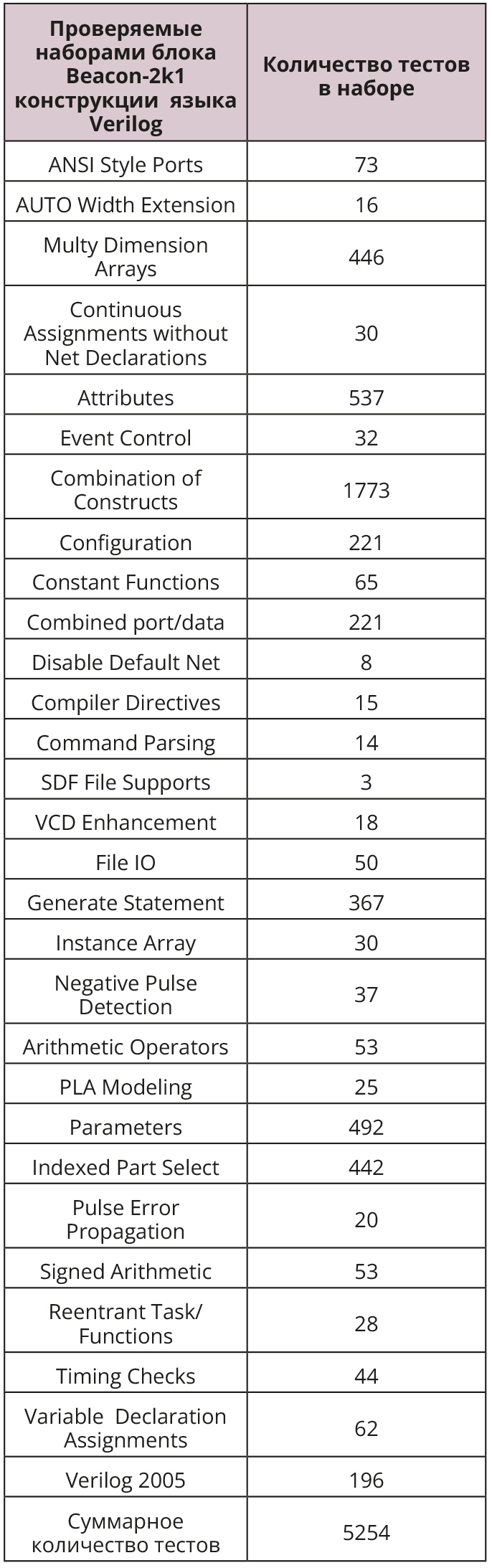

Что касается самих тестов, то кроме обычных требований простоты и наглядности HDL-описаний, наличия как позитивных, так и негативных тестов, полноты покрытия конструкций языка и т.п. также учитывается требование возможности интеграции тестов в тестовые наборы, так называемые регрессионные тесты, простоты настройки на изменения стандартов языка и др. Как пример, в табл. 2 представлены параметры набора Verilog-тестов Beacon-2k1 компании InterraSystems.

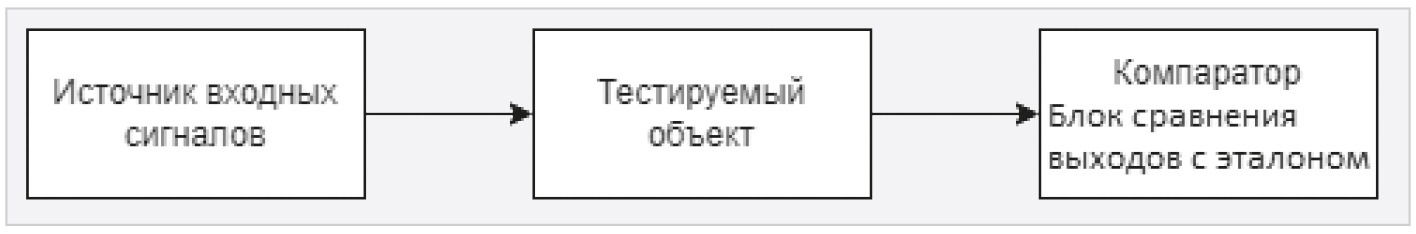

Она включает модель источника входных сигналов, модель тестируемого объекта и компаратора.

Простые тесты

Простейший тест, используемый для верификации системы моделирования, обычно не содержит отдельный блок – источник входных сигналов, а состоит из операторов, включающих исследуемую на реализуемость конструкцию языка и модель компаратора – блока проверки совпадения выходов тестируемого объекта с эталоном.

Такой подход к организации тестов реализован, например, в свободно распространяемом наборе Verilog-тестов IVLTests, использовавшемся при разработке системы моделирования IcarusVerilog [3]. Набор содержит примерно 2000 тестов, что гораздо меньше, чем в наборе Beacon-2k1. Тесты организованы как одномодульные тестбенчи, внутри которых все компоненты представлены последовательностями HDL- операторов. Каждый тест – это отдельный файл, название которого отражает проверяемую конструкцию языка и её вариант.

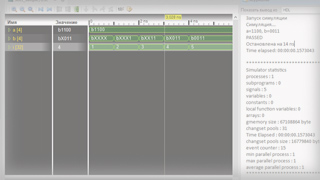

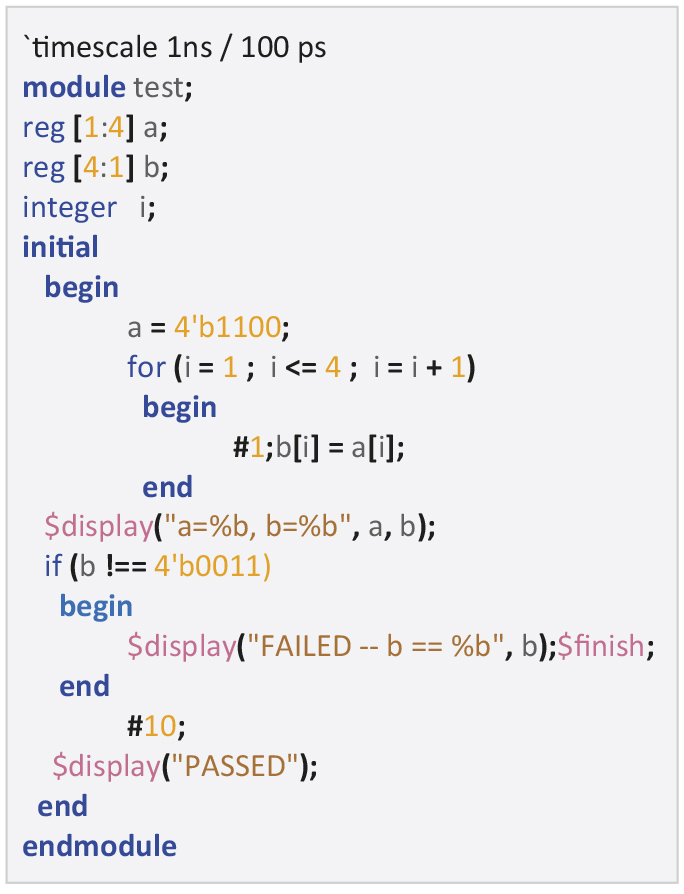

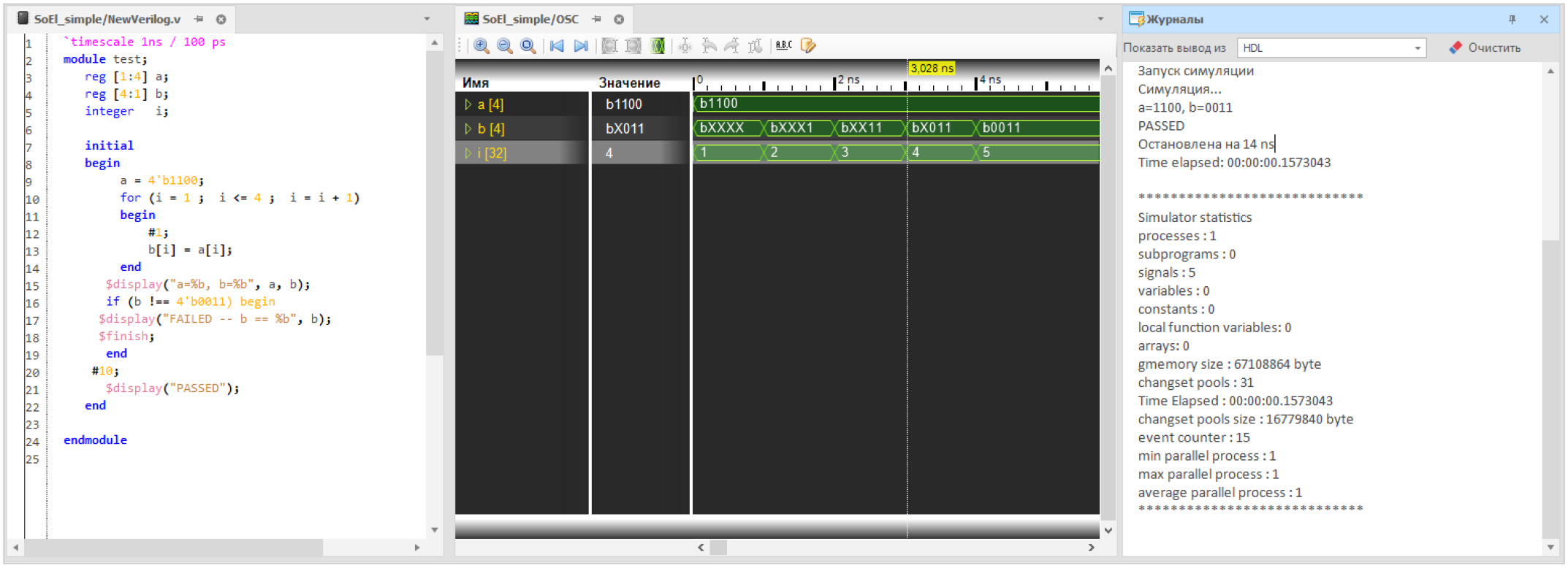

Как пример, ниже приведён один из файлов библиотеки IVLTests – файл bitsel2.v. Это тест проверки правильности выполнения верифицируемой САПР операции с разрядами векторов. Разряды четырёхразрядного вектора a = 1100 в обратном порядке должны быть переписаны в вектор b, и в результате b должно быть равно 0011. Если результат не такой, на консоль выдаётся сообщение FAILED, значение b и происходит останов моделирования, иначе в конце моделирования выдаётся сообщение PASSED (рис. 2).

Результаты прогона теста bitsel2.v на Simtera с временны́ми диаграммами (осциллограф) и данными на консоли (справа) представлены на рис. 3.

Для верификации самих HDL-тестов разработчиками Simtera в основном как эталонные используются системы «большой тройки» – Siemens, Cadence, Synopsys, и в некоторых случаях система моделирования XSIM, встроенная в САПР ПЛИС Vivado от Xilinx.

Сложные тесты

Помимо наборов тестов, предназначенных для проверки системы моделирования Simtera и покрывающих язык Verilog, приходится разрабатывать тесты, охватывающие синтезабельное подмножество языка, по типу Beacon-RTL-Verilog. Такие тесты пригодны также для верификации систем синтеза и имплементации логических схем. В таких тестах в виде отдельных модулей, а также отдельных файлов, разделяются описания синтезируемого объекта и использующего его тестбенча.

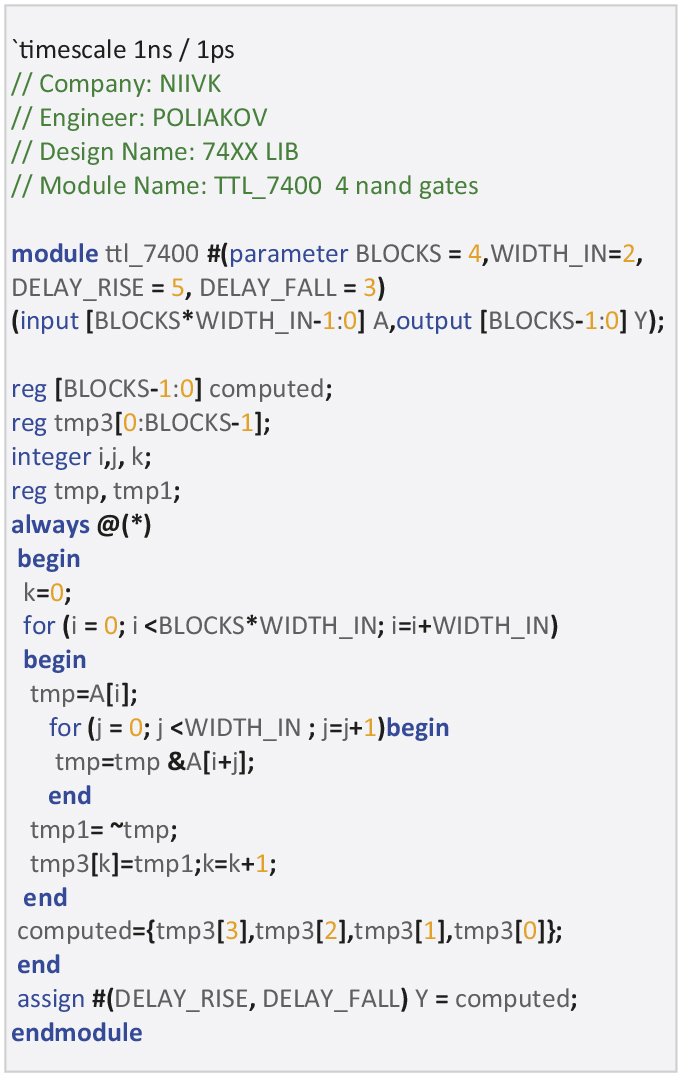

В качестве примера ниже (рис. 4) приводится модифицированное (оригинал – тест из библиотеки IceChipsТима Руди [4]) описание микросхемы из четырёх элементов 2 ИНЕ (микросхема 4-2ИНЕ, в серии 74 обозначаемая как 7400) и её тестбенча (соответственно файлы ttl_7400.v и ttl_7400_tb.v). Описание микросхемы 7400 параметризировано, что позволяет при желании настраивать модель на значения задержек разных серий микросхем при поведенческом моделировании. Подобные модели, например, можно включать в библиотеку схемотехнического моделирования Simtera и Delta Design [5].

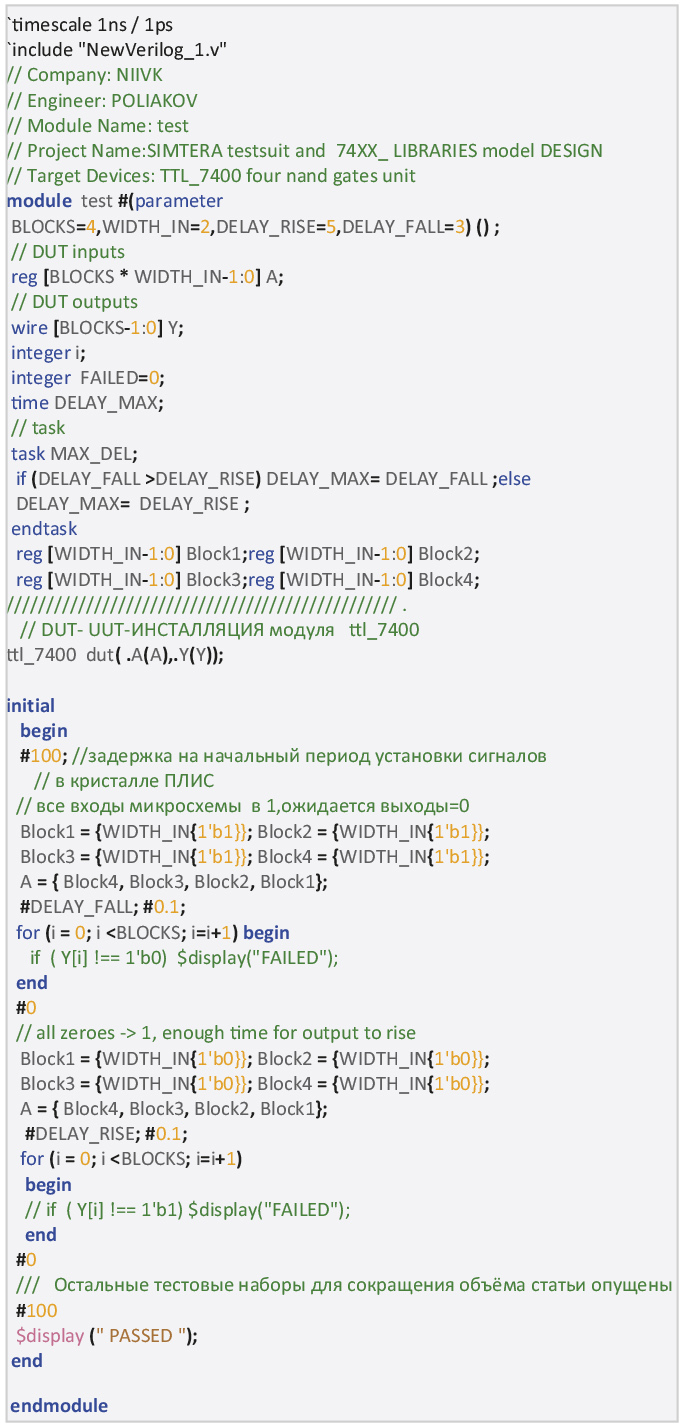

Приведённый ниже тестбенч (рис. 5) нами параметризирован и может использоваться не только для верификации системы моделирования Simtera, но и для верификации синтеза и имплементации. В последнем случае при временном или посттрассировочном моделировании параметры задержек DELAY_RISE = 5, DELAY_FALL = 3 схемы 4-2ИНЕ заменяются в тестбенче на задержки, рассчитываемые САПР после трассировки сигналов в имплементируемой схеме.

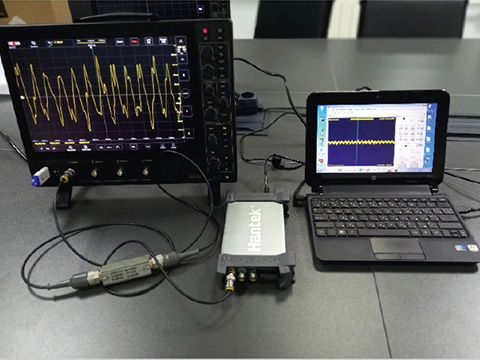

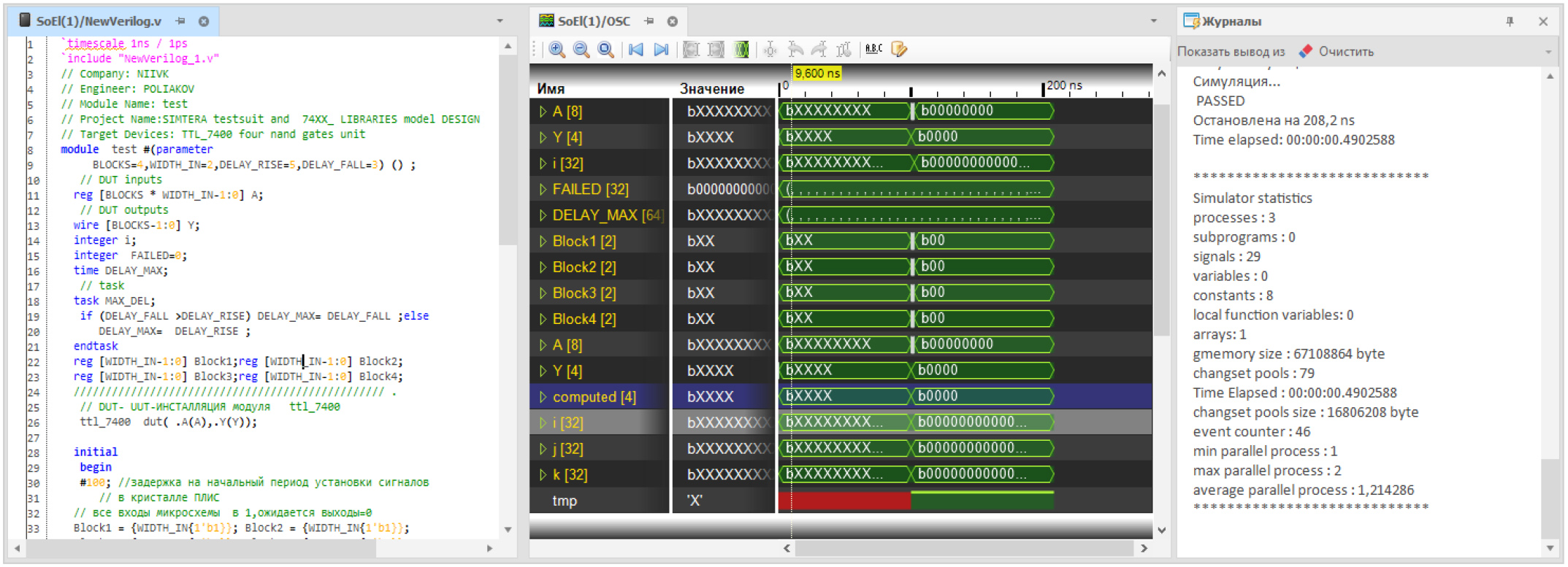

Результаты прогона теста на Simtera выведенными (осциллограф) временными диаграммами и данными на консоли представлены на рис. 6.

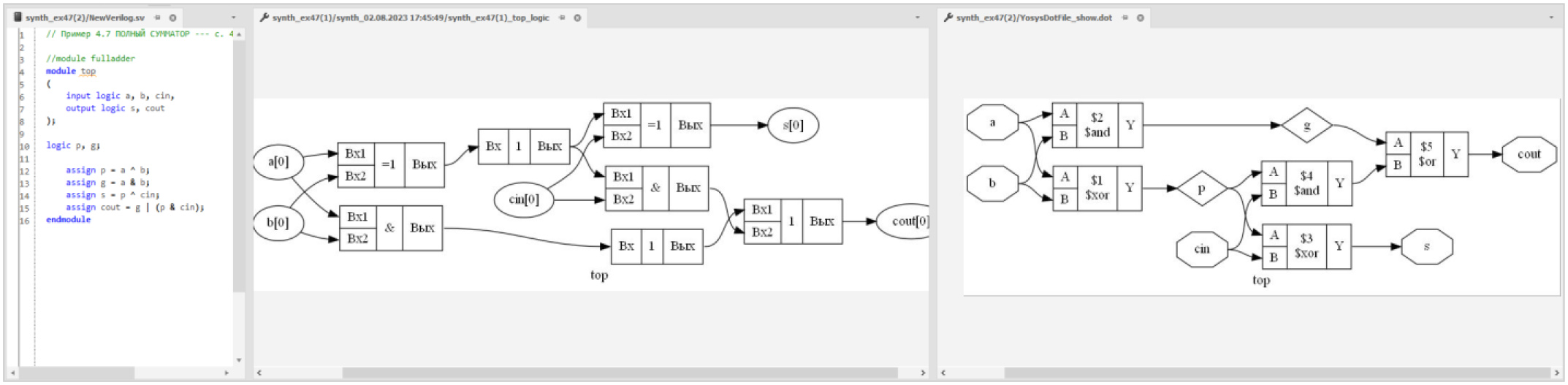

На момент написания статьи синтез ttl_7400.v ещё не поддерживался в Simtera, тем не менее в системе регрессионного тестирования заложены тесты поведенческого и логического синтеза. На рис. 7 представлены результаты синтеза поведенческого Verilog описания полного сумматора (test ex4_7.v) (описание заимствовано из книги Дэвида и Сары Харриссов [6]) с использованием двух синтезаторов – синтезатора, встроенного в Simtera, HDL операторов синтезатора с открытым кодом.

Заключение

Система моделирования Delta Design Simtera в настоящее время находится на стадии бета-тестирования подсистем поведенческого моделирования и синтеза на базе языков Verilog и SystemVerilog.

Учитывая большой объём работ по созданию отечественной библиотеки HDL-тестов, разработчики САПР Delta Design Simtera будут весьма признательны всем читателям, которые смогут прислать им самопроверяющиеся тесты.

Напоминаем также, что открыто бета-тестирование Delta Design Simtera, и получить версию системы можно, написав на адрес info@eremex.ru или в Telegram-сообществе.

Литература

- Малышев Н. Цифровое моделирование цифровых и цифро-аналоговых узлов в системе Delta Design Simtera // Современная электроника. 2021. № 1. С. 60–61.

- URL: http://www.interradesign.com/hdl_test_suits.php.

- Icarus Verilog Test Suite. URL: https://sourceforge.net/projects/ivtest/.

- TimRudy/ice-chips-verilog. URL: https://github.com/TimRudy/ice-chips-verilog.

- Смирнов А., Гимеин А. Схемотехническое моделирование Delta Design SimOne // Современная электроника. 2021. № 9. С. 34–36.

- Харрис Дэвид М., Харрис Сара Л. Цифровая схемотехника и архитектура компьютера. 2-е изд. Morgan Kaufman. С. 451.

Если вам понравился материал, кликните значок — вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал —не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!