16-разрядные микроконтроллеры и цифровые сигнальные контроллеры (DSC) находят применение в оборудовании и изделиях самого различного назначения. Компания Microchip выделяет ряд целевых областей применения своих продуктов данной категории: высокопроизводительные надёжные встраиваемые устройства, встраиваемые устройства с малым энергопотреблением, системы управления двигателями, цифровые системы управления питанием, системы функциональной безопасности. Важной особенностью 16-разрядных микроконтроллеров компании является их технологическая совместимость с 8-разрядными PIC-микроконтроллерами, что позволяет достаточно просто модернизировать ранее разработанные устройства и приборы, выполненные на их основе с целью улучшения качественных характеристик аппаратуры.

В каталоге Microchip 2022 года представлена большая номенклатура 16-разрядных устройств в следующих группах:

- цифровые сигнальные контроллеры dsPIC33C DSC;

- цифровые сигнальные контроллеры dsPIC33EV 5V DSC;

- микроконтроллеры PIC24F MCU.

Приборы dsPIC33C выпускаются в двухъядерном (dsPIC33CH) и одноядерном (dsPIC33CK) вариантах, в обоих вариантах представлено по несколько семейств микросхем с различным объёмом флеш-памяти (64К, 128К, 256К, 512К, 1024К). Рассмотрим особенности двухъядерных сигнальных контроллеров семейства dsPIC33CH128MP508. Микросхемы этого семейства позиционируются как 16-разрядные двухъядерные цифровые сигнальные контроллеры с ШИМ и CAN FD интерфейсами высокого разрешения, выполненные в 28/36/48/64/80-выводных корпусах. Микросхемы семейства характеризуются широким набором функциональных возможностей, высоким быстродействием и малым энергопотреблением.

Условия эксплуатации микросхем при напряжении питания 3…3,6 В определяются диапазоном рабочих температур и достижимым быстродействием процессорных ядер. В диапазоне рабочих температур от –40 до +125°С достижимое быстродействие ведущего ядра может достигать 100 MIPS, в диапазоне температур от –40 до +150°С быстродействие не превышает 60 MIPS. Микросхемы обеспечивают управление режимами малого энергопотребления (спящий, бездействия, «дремлющий»/Sleep, Idle, Doze), сброса при включении и выключении питания.

Далее рассмотрим основные особенности процессорного ядра микросхем семейства:

- работа в ведущем и ведомом режимах (Master/Slave) с независимой периферией для обоих режимов;

- объём встроенной программируемой флеш-памяти 64…128 КБ, ОЗУ – 16 КБ (Master core), 24 КБ память программ и 4 КБ памяти данных (Slave Core);

- окна связи между ведущим и ведомым ядрами (MSI);

- архитектура с эффективным кодом (C и Assembler), 40-битные аккумуляторы, поддержка 32-битного умножения;

- пять наборов регистров и аккумуляторов для быстрого реагирования на прерывания.

Блоки синхронизации микросхем содержат внутренние тактовые генераторы с программируемой ФАПЧ и выходами тактовых импульсов Master Clock и Slave Clock, резервный генератор (Back-Up Internal Oscillator), схемы быстрого включения (Fast Wake-up/Start-up), LC-генератор с малым энергопотреблением (LPRC-Oscillator).

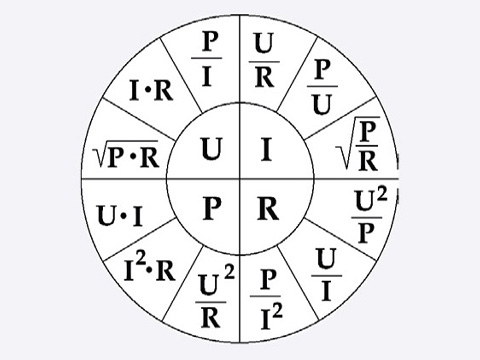

Микросхемы семейства обеспечивают работу с ШИМ-интерфейсами высокого разрешения с точным положением фронтов импульсов. Блок устройств с ШИМ содержит 8 каналов (4/8 Master/Slave) с разрешением 250 пс. В блок ШИМ также входят: DC/DC- и AC/DC-преобразователи, источник бесперебойного питания (UPS), драйверы двигателей различного типа (BLDC, PMSM, SR, ACIM).

В таймерную секцию микросхем входят два 16-разрядных таймера общего применения, 12 модулей SCPP с режимами таймера, захвата, сравнения и ШИМ (SCCP – Signaling Capture Compare PWM) и модуль периферийного генератора триггеров PTG для обеспечения координации работы периферийных устройств.

Микросхемы семейства обеспечивают выполнение ряда аналоговых и аналого-цифровых функций, обеспечиваемых следующими устройствами:

- четыре модуля 12-разрядных АЦП (один для ведущего ядра, три – для ведомого), обеспечивающие до 18 каналов преобразования со скоростью 3,5 Мбит/с;

- четыре модуля 12-разрядных ЦАП с аппаратной компенсацией наклона (один модуль для ведущего ядра, три модуля – для ведомого);

- три модуля усилителей с программируемым усилением (PGA) для ведомого ядра с возможностью взаимодействия с АЦП ведущего ядра;

- общий выход для ЦАП и аналоговых компараторов, выход PGA.

Для обеспечения связи с внешними устройствами в микросхемах семейства предусмотрены следующие интерфейсы: три модуля UART с поддержкой протоколов DMX и LIN/J2602; три 4-проводных модуля SPI/I2S, модуль CAN с гибкой скоростью передачи данных (FD), три модуля I2C с поддержкой шины SMBus. Микросхемы семейства обеспечивают и целый ряд других функций и возможностей:

- прямой доступ к памяти (DMA) – шесть каналов для ведущего ядра и два канала для ведомого ядра;

- поддержка разработки отладки (Debugger Development Support);

- функции безопасности (сторожевой таймер, код исправления ошибок, двухскоростной пуск и др.);

Также ряд микросхем семейства оснащён шинами SENT (Single-Edge Nibble Transmission), используемой для передачи сигналов датчиков в системах управления различного назначения,

в том числе автомобильных.

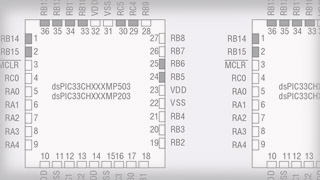

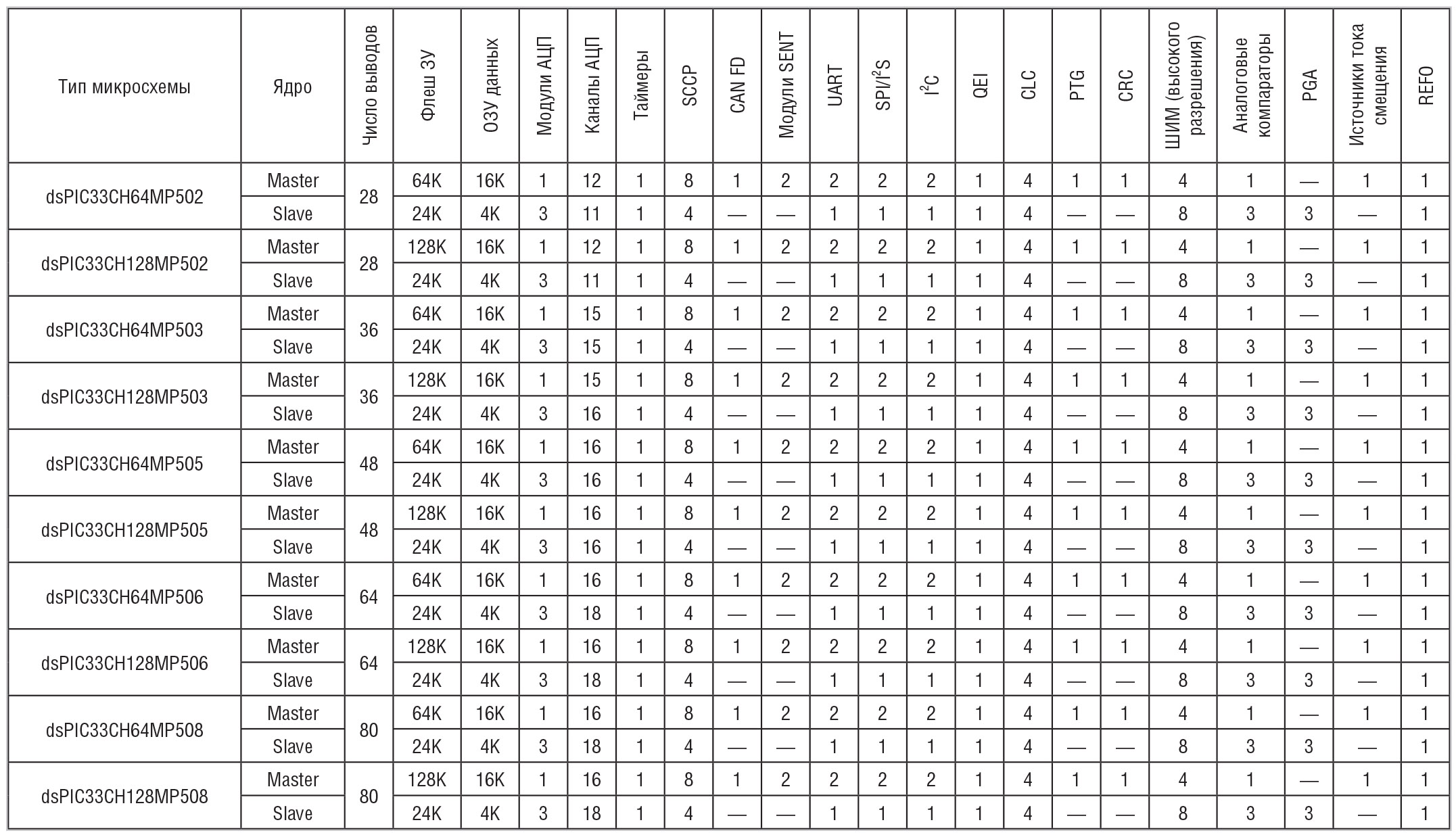

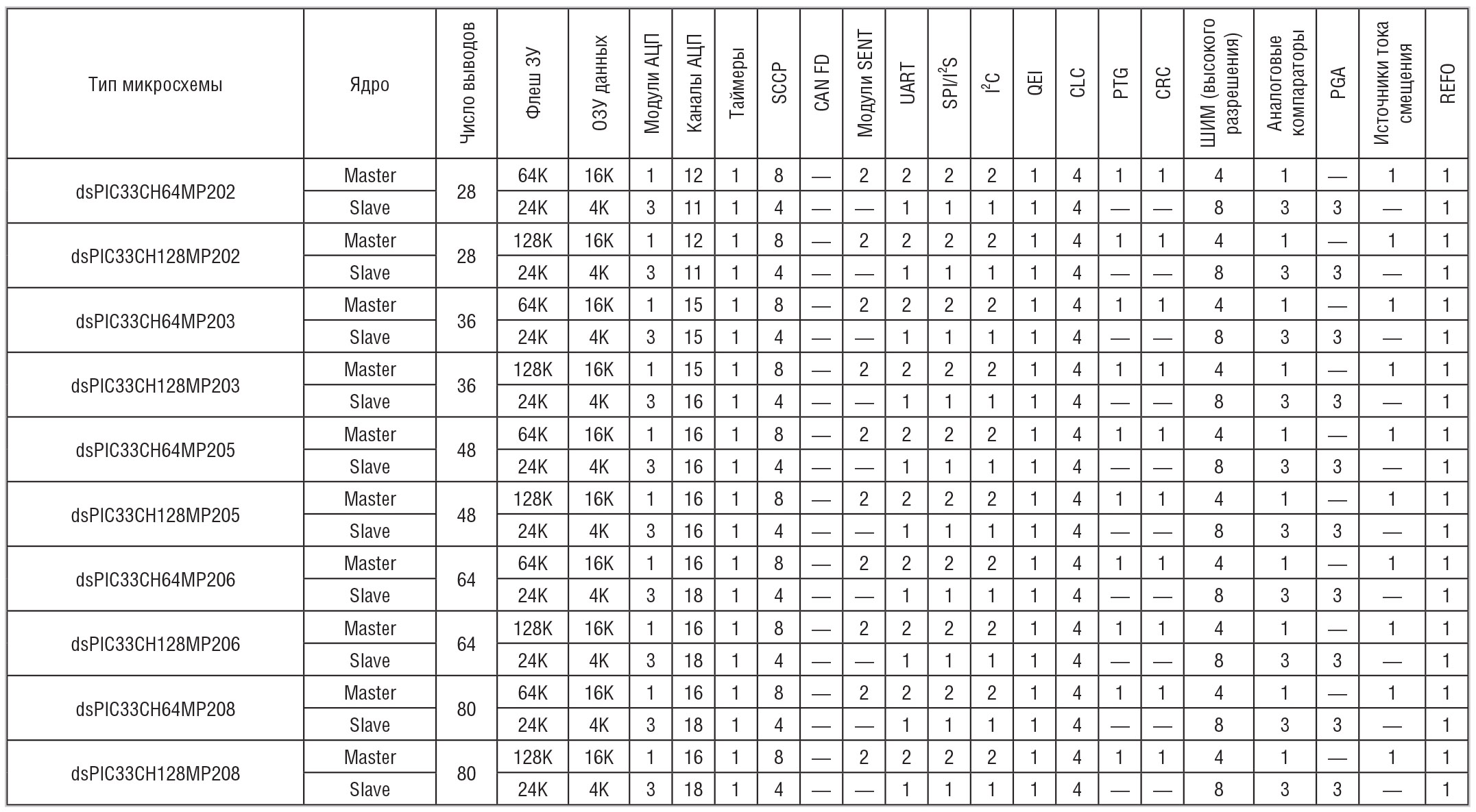

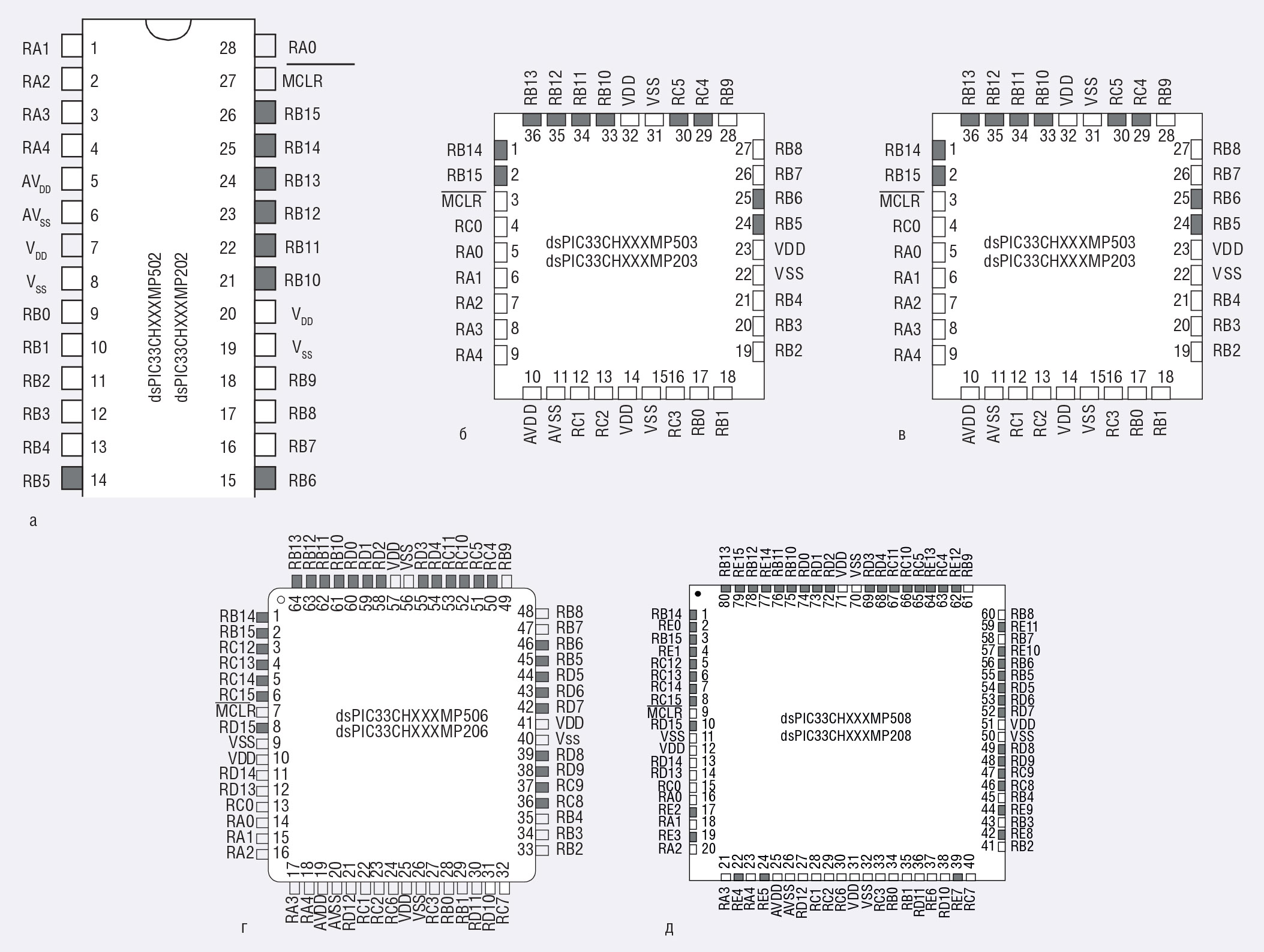

В состав семейства входит две группы по 10 микросхем в каждой – dsPIC33CHxxxMP50x и dsPIC33CHxxx20x (без интерфейса CAN). Конкретные микросхемы отличаются типами корпусов, объёмов памяти, количеством различных устройств и каналов, основные характеристики микросхем группы ххх50х приведены на рис. 1, группы ххх20х – на рис. 2. На рис. 3 (а, б, в, г, д) приведены цоколёвки микросхем рассматриваемого семейства в корпусах SSOP28, UQFN36, TQFР48/UQFN48, TQFP64/QFN64, TQFP80. Следует отметить, что на рисунке приведены условные обозначения выводов микросхем RA, RB, RC, RD, RE, реальное назначение этих выводов может быть различным и устанавливается при отладке микросхем. Описание процесса отладки приведено в спецификациях и руководствах по применению микросхем.

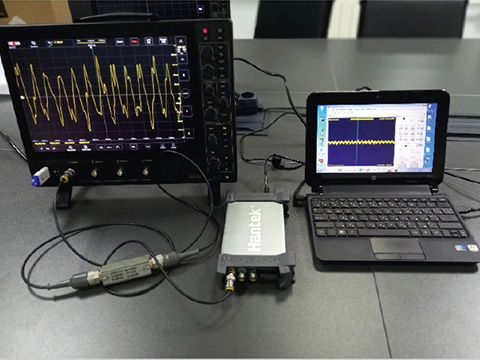

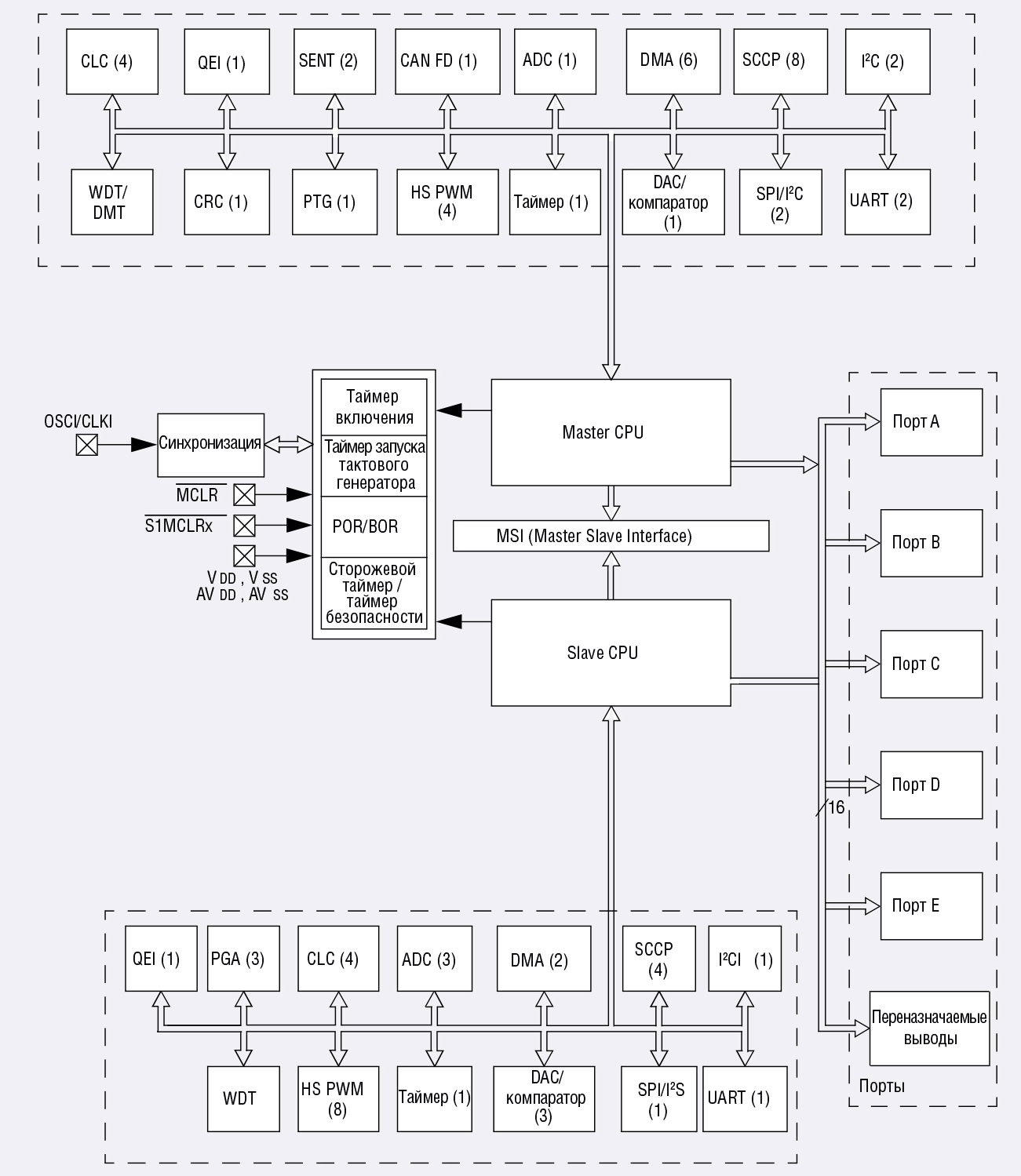

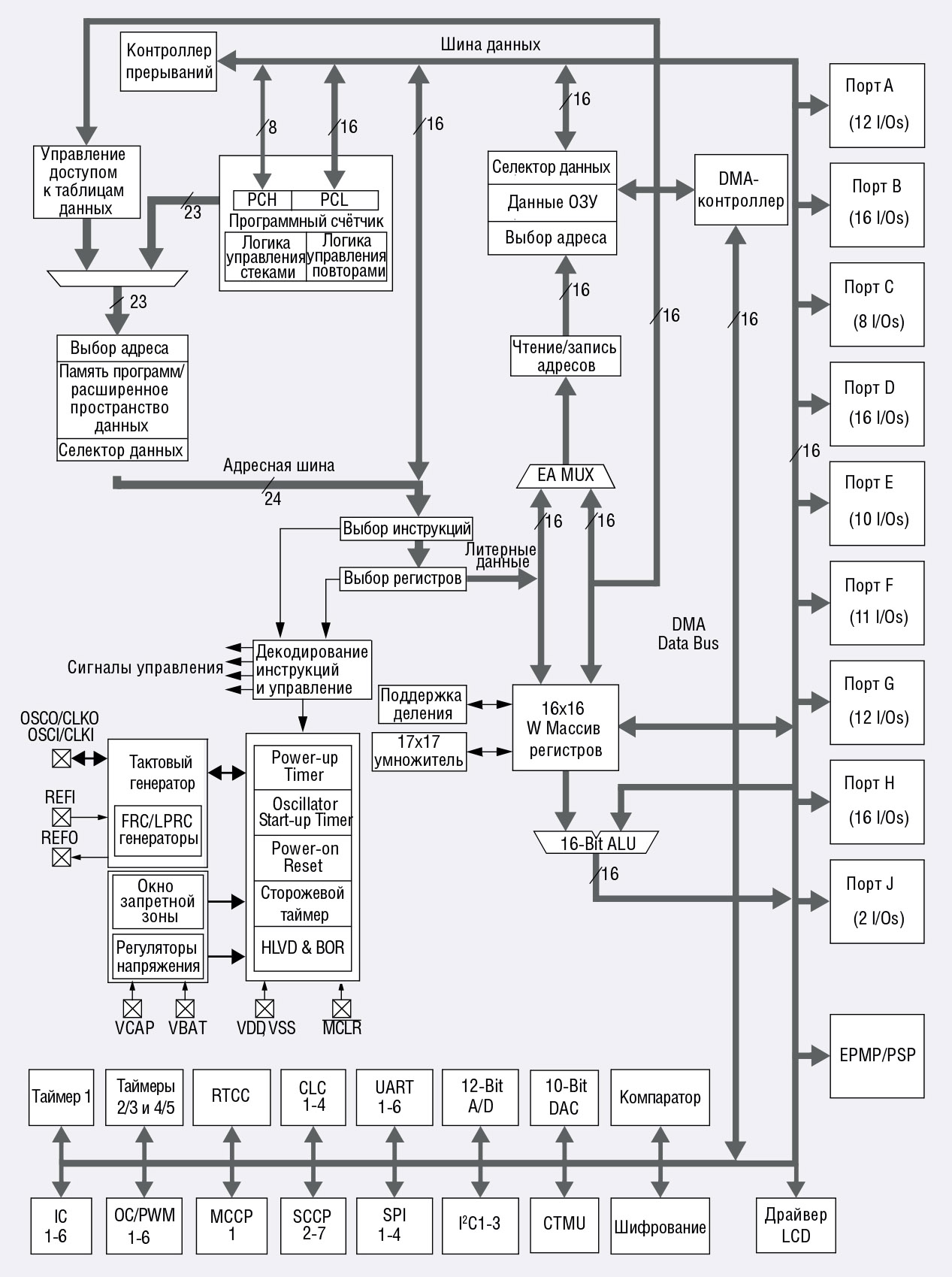

Цифровые сигнальные контроллеры компании по сравнению с сопоставимыми цифровыми сигнальными процессорами (DSP) характеризуются большей функциональностью и оснащённостью интерфейсами и интегрированными устройствами. Ядра Master и Slave микросхем могут работать и отлаживаться отдельно друг от друга. Обе подсистемы имеют свои собственные контроллеры прерываний, генераторы тактовых импульсов, логику портов, мультиплексоры ввода/вывода. В результате микросхемы dsPIC33CH эквивалентны двум DSC на одном кристалле, при этом ведущее ядро выполняет код из программной флеш-памяти (PFM), а ведомое ядро – из программной оперативной памяти (PRAM). Обобщённая структурная схема микросхем семейства dsPIC33CH128MP508, а также других семейств серии dsPIC33CH, например dsPIC33CH512MP508, приведена на рис. 4, цифры в скобках на рисунке означают количество устройств.

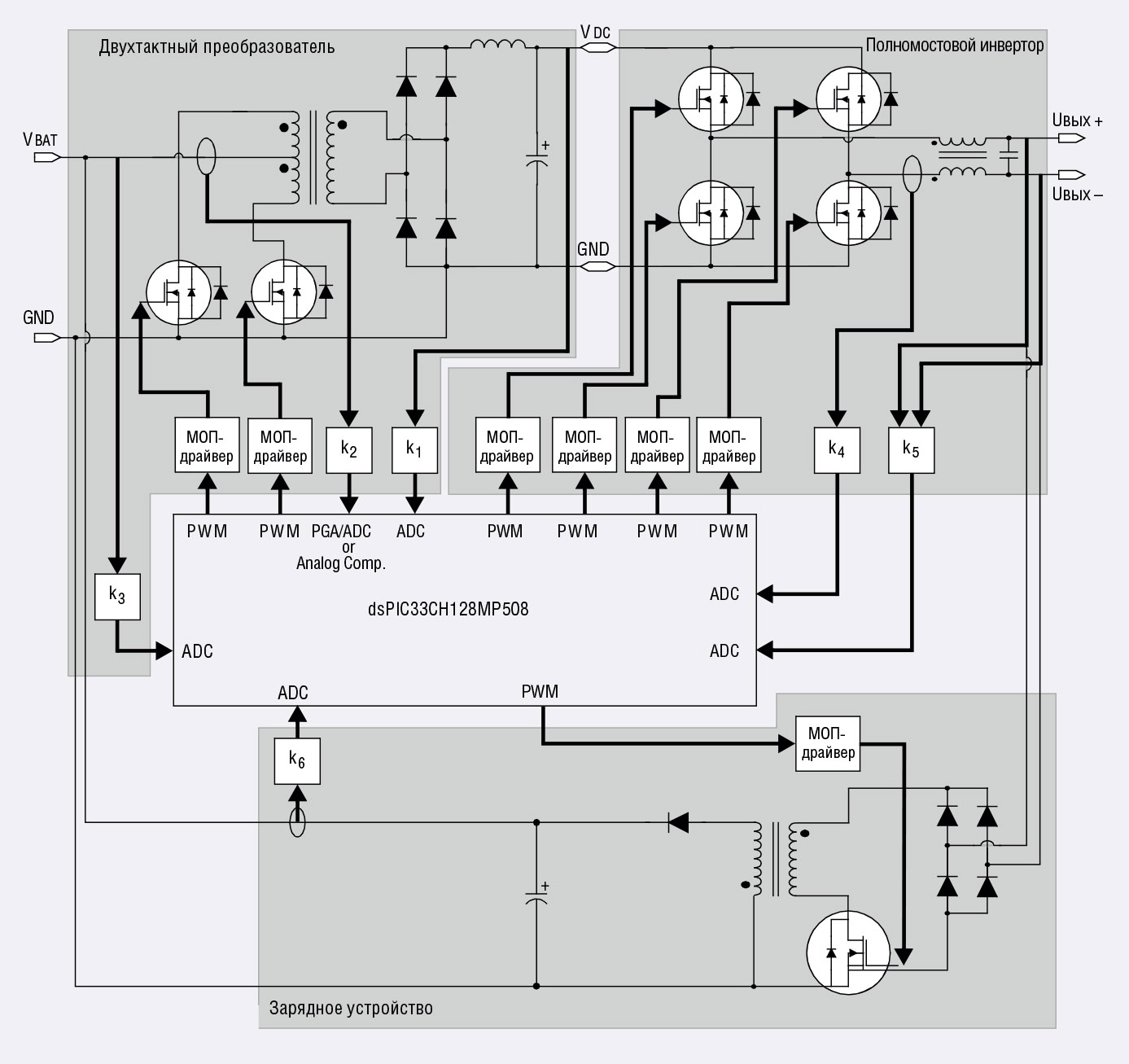

Одной из областей применения микросхем рассматриваемых семейств являются интеллектуальные системы питания (Intelligent Power), такие как AC/DC-, DC/DC-, DC/AC-преобразователи, беспроводные зарядные устройства, солнечные панели, системы управления батарейным питанием и цифровые системы управления питанием. Для примера на рис. 5 приведена схема бесперебойного источника питания на основе микросхемы семейства dsPIC33CH128MP508. Микросхема обеспечивает преобразование сетевого переменного напряжения в постоянное, обратное преобразование постоянного напряжения от выпрямителя или аккумулятора и, при необходимости, его подзарядка.

Компания выпускает широкую номенклатуру 16-разрядных микроконтроллеров под общим названием PIC24F с высоким быстродействием для гибких и инновационных проектов с высоким уровнем интеграции периферийных устройств. Микроконтроллеры PIC24F обеспечивают поддержку таких периферийных устройств и интерфейсов, как UART, USB, SPI, I2C, ШИМ и таймеры, а также специализированные периферийные устройства для графических сегментных ЖК-дисплеев и аудиоприложений (АЦП, ЦАП, компараторы и ОУ). Кроме того, микроконтроллеры содержат независимые от ядра периферийные устройства, такие как конфигурируемые логические ячейки (CLC), схемы прямого доступа к памяти (DMA) и криптографические ускорители. Ряд микросхем семейства PIC24F предназначен для эксплуатации в жёстких условиях в системах промышленной автоматизации и автомобильных приложениях.

В каталоге компании 2022 года представлено несколько групп микроконтроллеров PIC24F, разделённых на семейства (PIC24F’GB, PIC24F’GL, PIC24F’GD, PIC24F’GU и другие).

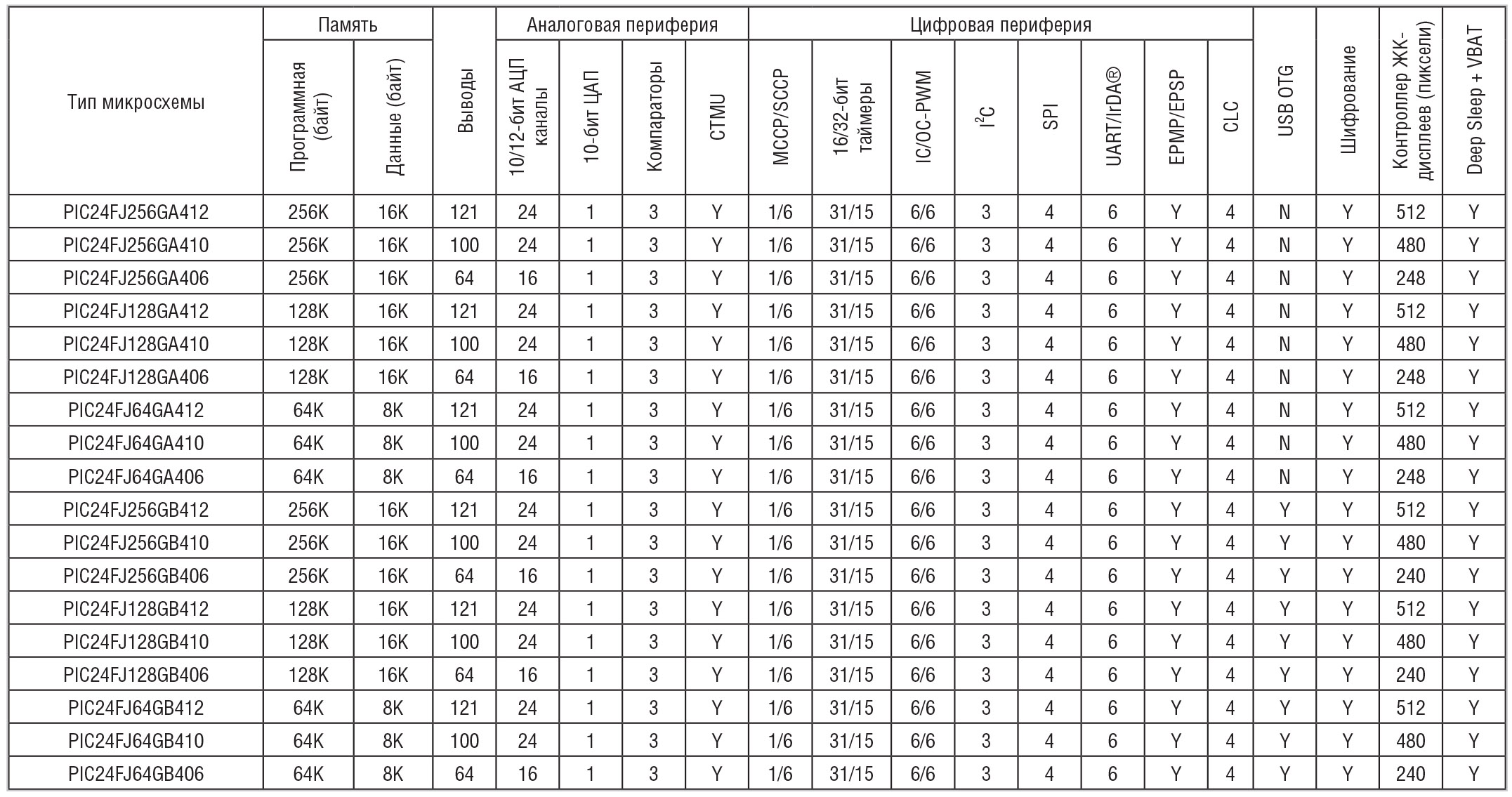

В каждое семейство входит несколько подсемейств микроконтроллеров, отличающихся между собой в основном объёмом флеш-памяти. Рассмотрим особенности микроконтроллеров PIC24F на примере семейства PIC24FJ256GA412/GB412. Микросхемы позиционируются как 16-разрядные микроконтроллеры с криптографическим устройством, сдвоенной флеш-памятью, поддержкой XLP, ЖК-дисплеев и USB OTG. Состав микросхем семейства и их функциональность приведены на рис. 6.

Центральным элементом всех микросхем рассматриваемого семейства является 16-разрядная Гарвардская архитектура, впервые применённая в dsPIC-контроллерах компании. Ядро

- центрального процессора микросхем семейства предлагает широкий спектр новых возможностей, в том числе:

- 16-разрядные данные и 24-разрядные адресные пути с возможностью перемещения информации между данными и пространствами памяти;

- линейная адресация до 12 МБ (программное пространство) и до 32 КБ (данные);

- 16-элементный массив рабочих регистров со встроенной поддержкой программного стека;

- аппаратный множитель 17×17 с поддержкой целочисленных вычислений;

- аппаратная поддержка преобразования 32-разрядных данных в 16-разрядные;

- набор инструкций, поддерживающий несколько режимов адресации, оптимизированный для языков высокого уровня, таких как «С»;

- операционная производительность до 16 MIPS.

Микросхемы данного и других семейств серии PiC24F могут с успехом применяться в устройствах с экстремально низким энергопотреблением XLP (Extreme Low-Power). Семейство микросхем включает в себя значительно расширенный набор режимов работы для максимального энергосбережения, в том числе новых:

- Retention Sleep (удержание спящего режима) – в этом режиме основные устройства получают питание от отдельного низковольтного стабилизатора;

- Deep Sleep («глубокий сон») – режим без часов реального времени (RTCC) для минимально возможного энергопотребления (RTCC – Rial Time Clock/Calendar);

- Vbat Mode – режим резервного питания с часами реального времени (или без них), при котором питание производится от резервной батареи в случаях отключения от нормы штатного напряжения питания.

Микроконтроллеры семейства также поддерживают стандартные режимы энергосбережения, например, в режиме Doze поддерживается работа тактового генератора. Отличительной особенностью микросхем рассматриваемого семейства является применение флеш-памяти с двумя разделами (Dual Partition Flash), что позволяет микроконтроллерам семейства использовать ряд новых возможностей, недоступных ранее:

- работа с двумя разделами памяти, при которой два разных приложения могут храниться в их собственных разделах кода;

- обновление в реальном времени, которое позволяет основному приложению продолжать работу, пока перепрограммируется второй раздел флеш-памяти;

- прямое программирование во время обработки данных из ОЗУ с возможностью их сжатия;

- возможность объединения разделов флеш-памяти для увеличения общего объёма и использования более сложных приложений;

- у всех микроконтроллеров семейства предусмотрено пять вариантов реализации тактовых генераторов, как на основе внутренних схем, так и с подачей внешних тактовых сигналов.

Независимо от объёма памяти все микроконтроллеры семейства имеют одинаковый набор периферийных устройств, что позволяет легко модернизировать конечные устройства для работы с более сложными приложениями путём простой замены конкретных микросхем на другие с бо́льшим объёмом памяти.

Криптографические модули микроконтроллеров семейства предоставляют эффективный набор параметров безопасности данных. Используя собственный автономный математический движок, модули могут независимо выполнять стандартное шифрование и дешифрование данных независимо от центрального процессора. Криптографический алгоритм поддерживает симметричное блочное шифрование по стандартам AES, DES/3DES в пяти режимах с длиной слов от 128 бит до 256 бит. Дополнительные функции включают генерацию истинного случайного числа (TRNG) внутри ядра, несколько вариантов хранения ключей шифрования/дешифрования и безопасную обработку данных, которая предотвращает компрометацию данных в ядре при внешнем чтении.

Интерфейс USB микроконтроллеров семейства обеспечивает функцию OTG (On-The-Go / «на ходу»), обеспечивающую соединение двух приборов по стандарту USB2.0 без промежуточного хоста. Благодаря применению протокола согласования USB-хоста HNP (Host Negotiation Protocol) возможно динамическое переключение между работой в режиме хоста или периферии. Это позволяет использовать гораздо более широкий спектр приложений с поддержкой USB.

Микроконтроллеры семейства обеспечивают работу в режиме прямого доступа к памяти DMA (Direct Memory Access), действующего совместно с центральным процессором, что позволяет перемещать данные между памятью данных и периферийными устройствами без вмешательства ЦП. Применение DMA увеличивает пропускную способность каналов передачи данных и уменьшает время выполнения операций. Шесть независимо программируемых каналов позволяют обслуживать несколько периферийных устройств практически одновременно, при этом каждое из устройств может выполнять разные операции с разными протоколами передачи данных.

Встроенный контроллер ЖК-дисплеев микросхем семейства включает в себя множество функций, упрощающих интеграцию дисплеев в приложения с низким энергопотреблением, для чего имеются встроенные регулятор напряжения с подкачкой заряда (ГПЗ/Charge Pump) и резистивная «лестница» (Resistor Ladder) для управления ЖК-дисплеями в режимах с открытым коллектором/стоком.

Для обеспечения внешних связей в рассматриваемых микроконтроллерах имеется несколько устройств с последовательной передачей данных, каждое из которых содержит шесть независимых каналов UART со встроенными кодерами/декодерами сигналов стандартов irDA, используемых для организации инфракрасных каналов связи. Микросхемы также содержат три независимых модуля для шины I2C с поддержкой режимов Master/Slave, а также три модуля для сигналов стандарта SPI с поддержкой звукового формата I2S.

Все микроконтроллеры рассматриваемого семейства оснащены аналоговыми и аналого-цифровыми модулями – 12-разрядными АЦП, компараторами, схемами измерения времени заряда батарей CTMU (Charge Time Measurement Unit), а также часами и календарём реального времени RTCC.

Микросхемы семейств выпускаются в различных корпусах и с различным числом выводов: 64-TQFP/QFN, 100-TQFP, 121-TFBGA, обобщённая структурная схема микроконтроллеров семейства приведена на рис. 7. Различное число выводов корпусов микроконтроллеров объясняется различным числом встроенных устройств, интерфейсов и каналов – таймеров, UART, USB OTG, АЦП, компараторов и др., а также числом возможных функций выводов микросхем, назначаемым при программировании.

Литература

- Официальный сайт Microchip // URL: https://www.microchip.com/en-us/products/microcontrollers-and-microprocessors/16-bit-mcus.

Если вам понравился материал, кликните значок — вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал —не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!