Введение

При проектировании печатных плат (ПП), предназначенных для передачи высокоскоростных сигналов между цифровыми микросхемами устройства, инженерам-конструкторам приходится решать ряд специфических задач. Одной из таких задач является синхронизация цифровых сигналов. Применительно к САПР ПП решение задачи одновременной доставки сигнала от источника к приёмнику разбивается на ряд последовательных шагов. Первый шаг – это создание полного описания библиотечного представления цифровых микросхем. Учёт таких параметров, как тип контакта и задержка на контакте. Второй шаг – формирование групп высокоскоростных сигналов в схемотехническом редакторе. Третий шаг – задание ограничений на длину соответствующих печатных проводников в редакторе правил. И четвёртый шаг – трассировка проводников с попаданием в доверительный временной интервал в редакторе ПП. Все эти шаги быстро осуществляются с помощью инструментария, ставшего доступным пользователям в версии 3.0 САПР Delta Design.

Шаг 1. Библиотечное представление цифровых микросхем

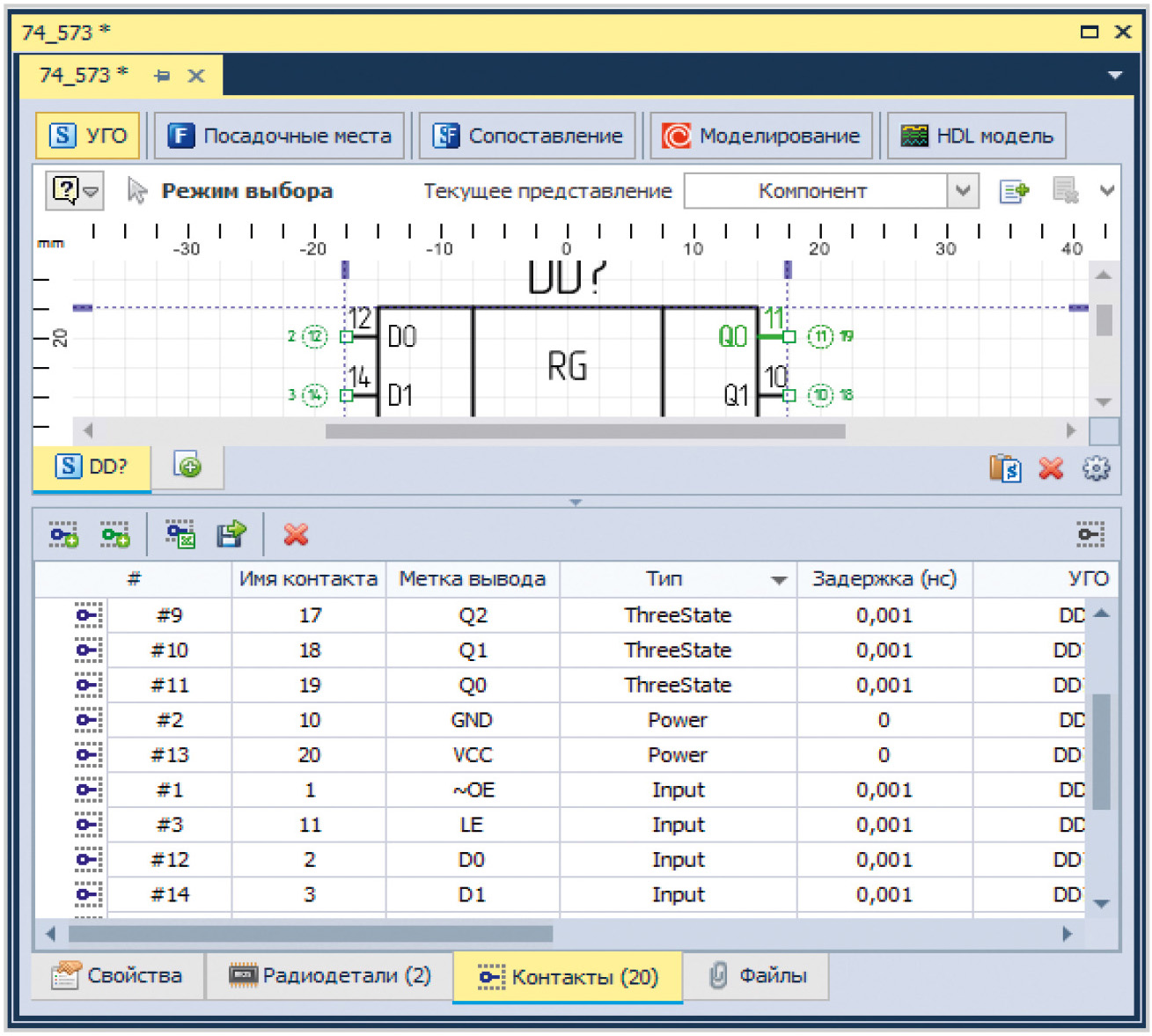

На этапе создания библиотечного описания компонента пользователю предлагается заполнить типы контактов и ввести значение задержки распространения сигналов (см. рис. 1).

Типы контактов помогают контролировать правильность подключения компонентов на схеме. Если инженер-схемотехник соединил несовместимые контакты микросхем, то ERC-проверка (проверка электрических правил) найдёт и проинформирует пользователя об этом. Также типы контактов используются системой при автоматическом формировании нового объекта «сигнал». Об этом подробнее будет рассказано далее. В столбце «Задержка» вводится значение длины пути, который цифровой сигнал проходит внутри и снаружи корпуса микросхемы. Значение задержки на контакте учитывается при расчёте общей длины пути, по которому сигнал распространяется на ПП.

Шаг 2. Цепь, сигнальная цепь, сигнал, группа сигналов

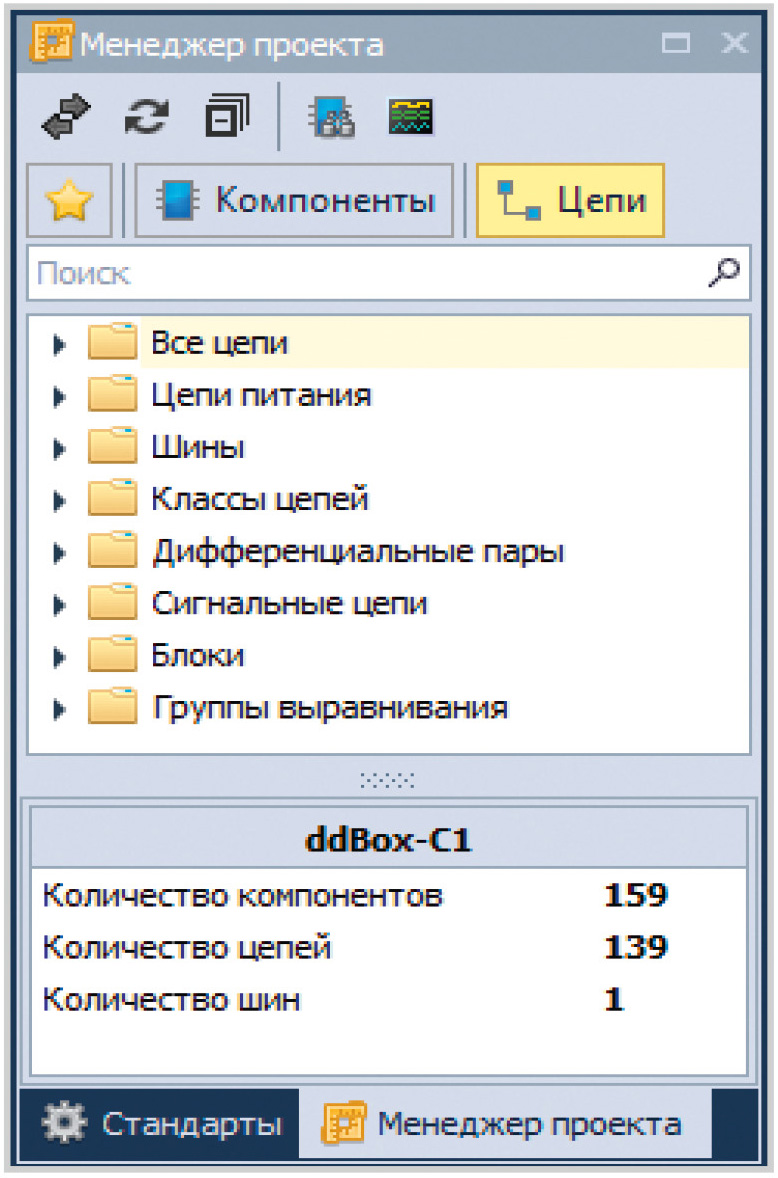

После создания схемы будущего устройства и запуска ERC-проверки в схемотехническом редакторе нужно задать четыре типа системных объектов: «цепь» → «сигнальная цепь» → «сигнал» → «группа выравнивания сигналов». Указанные объекты логически связаны друг с другом и отображаются в панели «Менеджер проекта» (см. рис. 2). В панели происходит и основное редактирование объектов: добавление, удаление, переименование, навигация к объектам в рабочем окне проекта.

Цепь. Цепь автоматически назначается каждому электрическому соединению, с помощью которого инженер-схемотехник объединяет выходы и входы различных компонентов на схеме. Каждая новая цепь схемы добавляется в общий список «Все цепи». Если цепь дополнительно помечается как цепь питания или если добавляется в шину, класс цепей, дифференциальную пару, то она также дублируется в соответствующих узлах «Цепи питания», «Шины», «Классы цепей», «Дифференциальные пары» (см. рис. 2).

Сигнальная цепь. В отличие от обычной цепи сигнальная цепь не появляется в системе сразу, а требует дополнительных операций по своему формированию. В иностранных САПР аналогом сигнальной цепи является расширенная или составная цепь (от англ. Extended net – Xnet). В общем случае сигнальная цепь является объединением n-го количества обычных цепей. В сигнальную цепь объединяются обычные цепи, по которым происходит распространение цифрового сигнала. Цепи питания в сигнальную цепь не добавляются. При этом обычные цепи могут объединяться через пассивные компоненты: резисторы, конденсаторы, индуктивности.

Создавая сигнальную цепь, пользователь формирует возможную область распространения цифрового сигнала. Под областью подразумеваются списки цепей и контактов компонентов, которые объединены данными цепями.

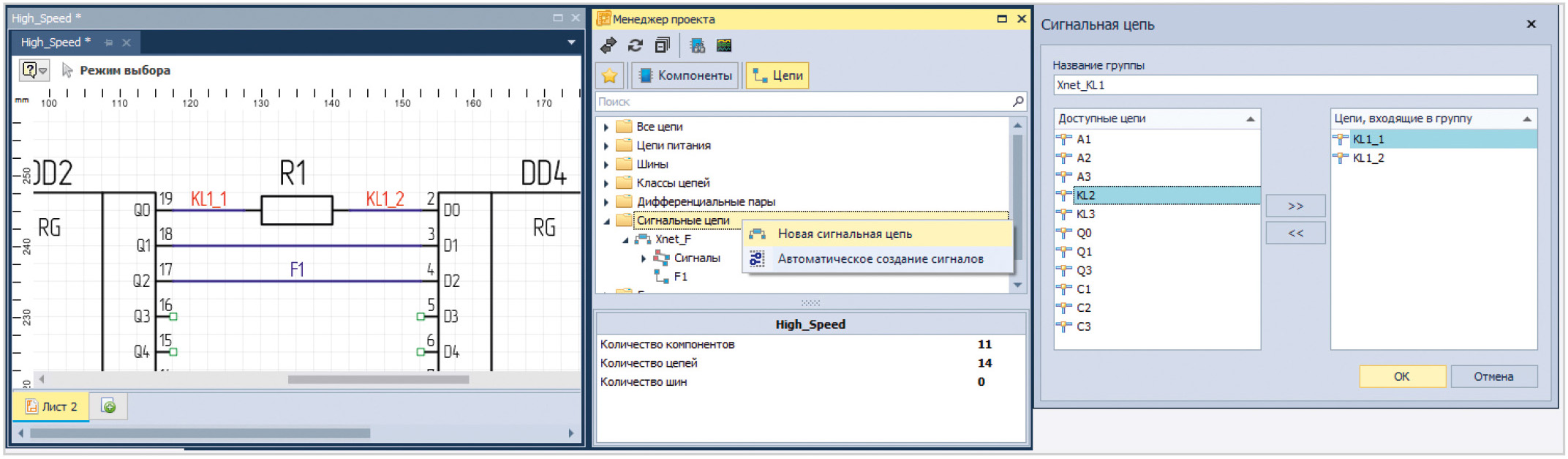

На рисунке 3 показан фрагмент схемы из двух цифровых микросхем с позиционными обозначениями DD2 и DD4. Чтобы показать область, в которой происходит распространение цифрового сигнала, в менеджере проекта была создана новая сигнальная цепь «Xnet_KL_1». При создании сигнальной цепи была сформирована следующая последовательность объектов:

контакт DD2.19 → цепь «KL1_1» → контакт R1.1 → резиcтор R1 → контакт R1.2 → цепь «KL1_1» → контакт DD4.2.

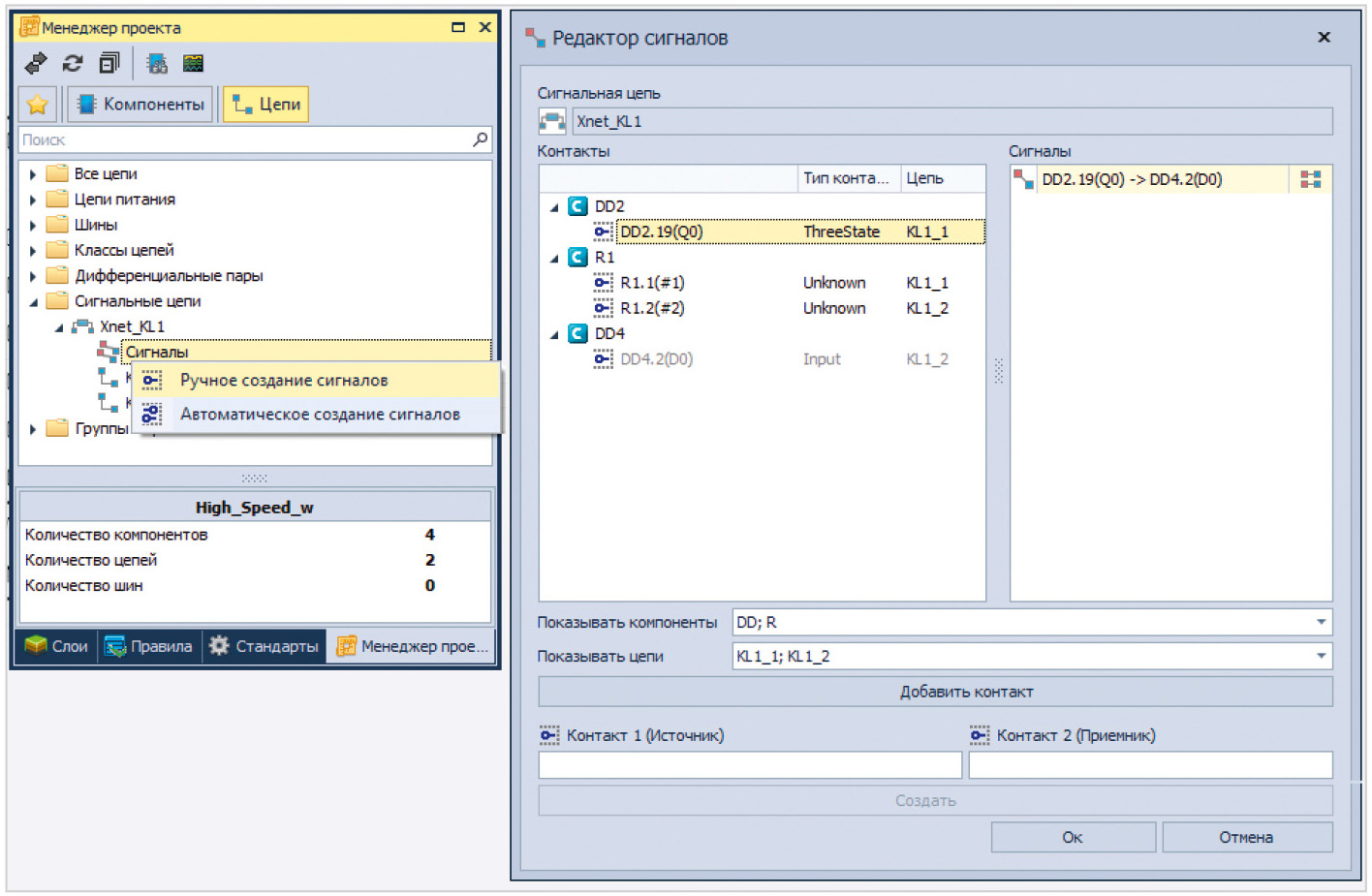

Сигнал. Объект «сигнал» располагается внутри сигнальной цепи и создаётся с помощью команд «Ручное создание сигналов» или «Автоматическое создание сигналов» (см. рис. 4). Если применяется ручное создание, то в «Редакторе сигналов» последовательно выбираются два контакта. Первым выбирается контакт «источник сигнала», вторым – «приёмник сигнала». В приведённом ранее примере это два контакта: DD2.19 (Q0) и DD4.2 (D0) (см. рис. 4)

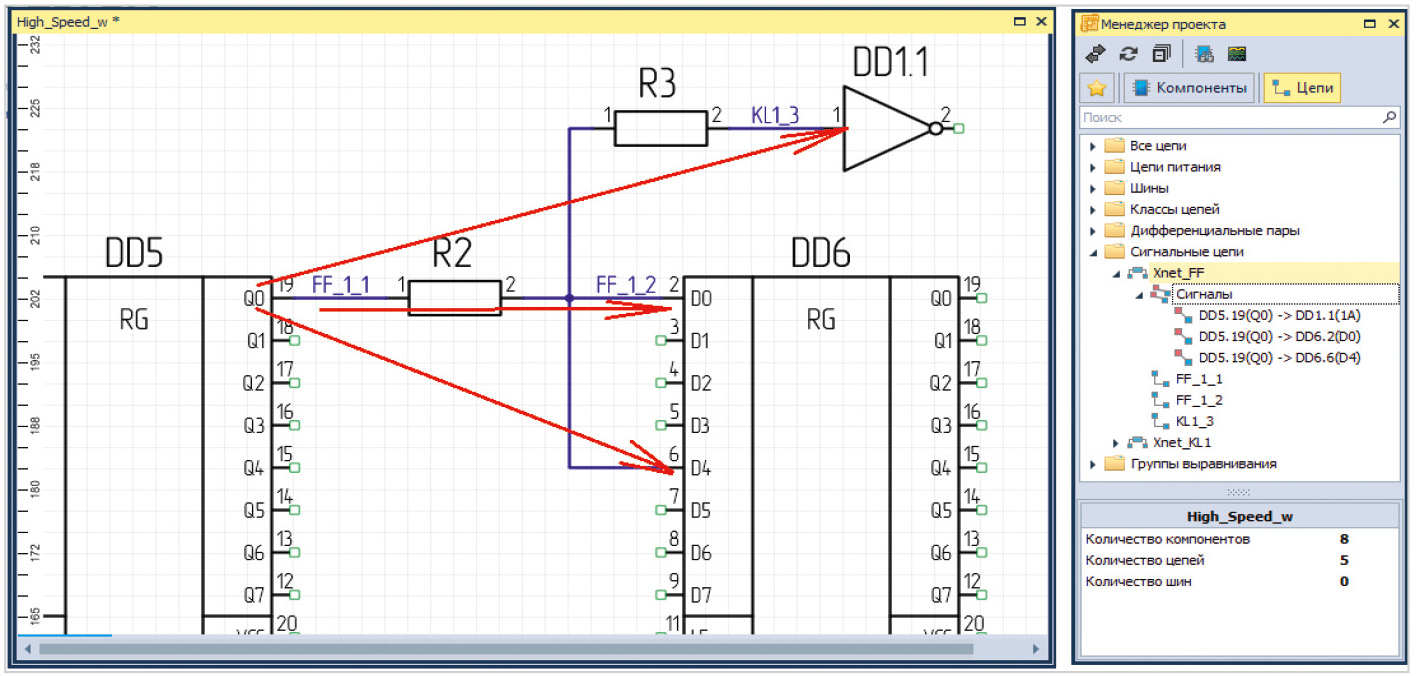

Отличие сигнала от сигнальной цепи. Для понимания отличия сигнала от сигнальной цепи обратимся к рисунку 5. На рисунке показан фрагмент схемы, на котором цифровой сигнал с выхода микросхемы DD5 подаётся на входы микросхем DD1 и DD6. Если проследить последовательность компонентов и обычных цепей, через которые происходит логическое распространение цифрового сигнала, то можно увидеть три цепочки:

- контакт DD5.19 → цепь «FF1_1» → контакт R2.1 → резиcтор R2 → контакт R2.2 → цепь «FF1_2» → контакт R3.1 → резиcтор R3 → контакт R3.2 → контакт DD1.1.1;

- контакт DD5.19 → цепь «FF1_1» → контакт R2.1 → резиcтор R2 → контакт R2.2 → цепь «FF1_2» → контакт DD6.2;

- контакт DD5.19 → цепь «FF1_1» → контакт R2. → резиcтор R2 → контакт R2.2 → цепь «FF1_2» → контакт DD6.6.

В такой сложной схеме подключения цифровых и пассивных компонентов сигнальная цепь «Xnet_FF_1» предоставляет пользователю возможность указать все пути распространения сигнала. Однако чтобы осуществлять в дальнейшем контроль над каждым цифровым сигналом по отдельности, в системе нужен дополнительный объект. Роль такого объекта и выполняет сигнал. У сигнала также есть другое название – пин-пара (от англ. pin-pair).

Вместо длинных последовательностей, представленных ранее, получается следующий набор сигналов (см. рис. 5):

- DD5.19 (Q0) → DD1.1 (1A);

- DD5.19 (Q0) → DD6.2 (D0);

- DD5.19 (Q0) → DD6.6 (D0).

Контроль создания сигнальных цепей и сигналов

Для того чтобы упростить процесс выбора нужной цепи и избежать создания неправильных сигнальных цепей, в системе существует ряд вспомогательных контролирующих механизмов. Например, все цепи из узла «Цепи питания» (см. рис. 2) фильтруются и не отображаются в списке доступных цепей окна «Сигнальная цепь» (см. рис. 3). Также из списка доступных будут исключены все цепи, которые уже входят в состав других сигнальных цепей.

В системе также реализована возможность автоматического создания сигналов. Если пользователь выбирает данную команду (см. рис. 4), то все описанные операции ручного создания сигналов за него будут сделаны в автоматическом режиме. Это позволяет экономить время на создание сигналов в больших сложных схемах. Однако эффективно и правильно автоматическое создание будет работать только в том случае, если изначально были определены типы каждого из контактов микросхем (см. рис. 1). Система создаст сигналы автоматически только в тех случаях, когда в сигнальной цепи присутствуют контакты с типом «Выход» и «Вход». Также автоматическое создание будет возможно, если в сигнальной цепи присутствуют контакты с типом «Выход» и «Двунаправленные». Если эти условия не будут выполнены, то автоматического создания сигналов не произойдёт, а в панели «Журналы» будет сформировано информационное сообщение. В сообщении будут указаны типы контактов, которых не хватает в конфигурации сигнальной цепи.

Если на схеме используется цифровая микросхема без описания типа контакта, то определить тип возможно в схемотехническом редакторе. Другой способ – обновление библиотечного представления компонента и последующая синхронизация схемы и библиотеки.

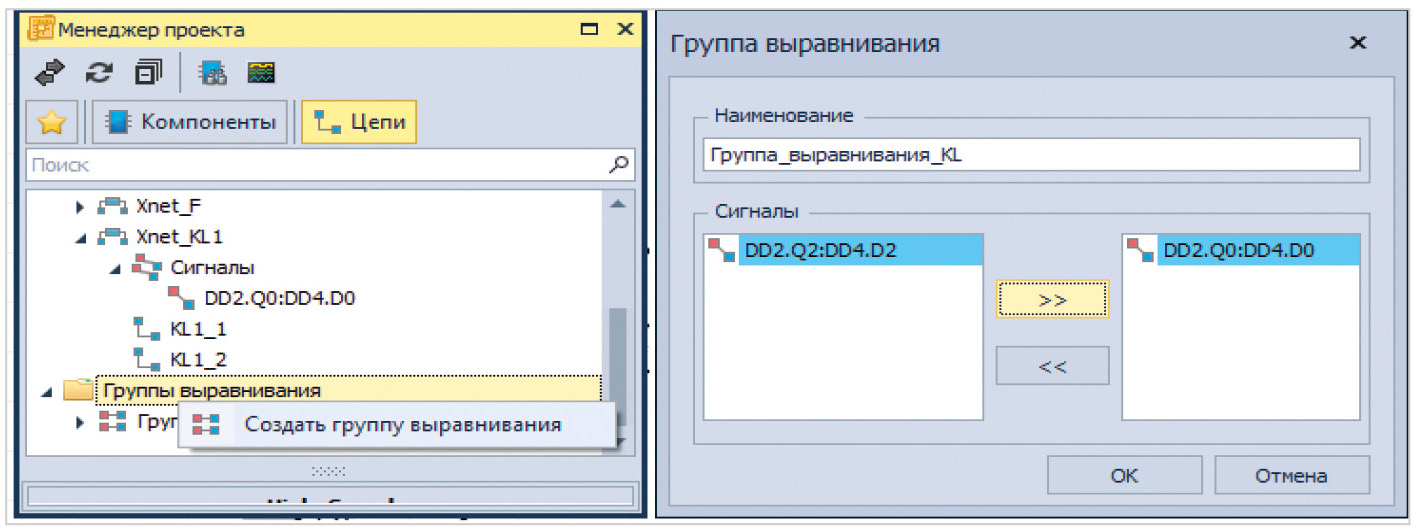

Группа выравнивания

Аналогично тому, как инженеры объединяют цепи, печатные проводники которых схожи по своим физическим характеристикам (допустимым ширине и зазорам между ними), в классы цепей, все созданные сигналы также могут быть объединены в «группы выравнивания». Чтобы создать новую группу выравнивания сигналов, в панели «Менеджер проекта» необходимо выбрать папку «Группы выравнивания» и вызвать контекстное меню (см. рис. 6).

В открывшемся диалоговом окне в поле «Наименование» вводится имя группы, и из общего списка всех сигналов формируется короткий список, отражающий специфику группы. Например, сигналы данных, адресов и т.д.

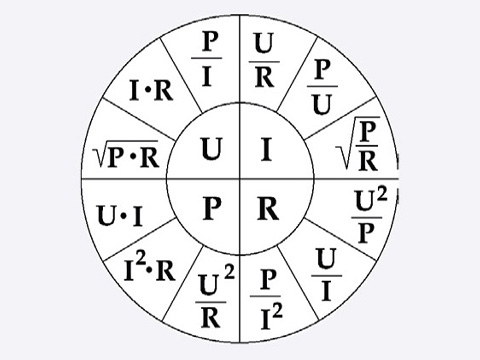

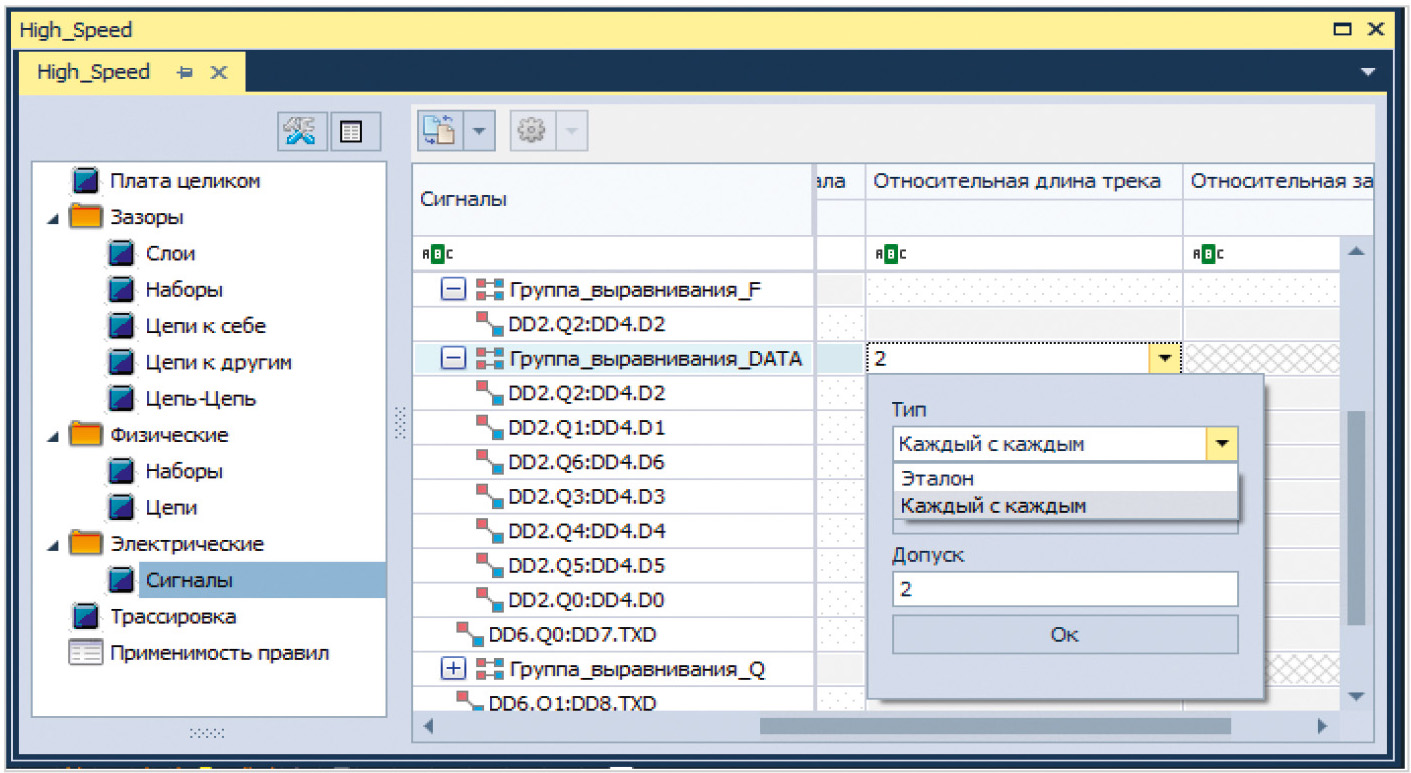

Шаг 3. Временны¢е ограничения

В редакторе правил в разделе «Электрические» → «Сигналы» представлен полный список сигналов и их групп выравнивания, созданный на предыдущем шаге. Временные ограничения в редакторе правил задаются двумя способами: ограничения накладываются на распространение каждого сигнала в отдельности или на группу сигналов. Ограничения на конкретный сигнал задаются в абсолютных величинах (мм или пс). Ограничения в группе задаются либо через сравнение каждого сигнала с каждым, либо через сравнение с эталоном. Доверительный интервал, в который должны попадать длины печатных проводников, также задаётся в мм или пс (см. рис. 7).

Как задержки задаются в системе

Электрическое распространение сигнала от источника к приёмнику осуществляется не только по медным печатным проводникам на плате. В многослойных платах путь распространения сигнала может значительно увеличиваться за счёт межслойных переходов. Необходимо также учитывать и габаритные размеры корпусов микросхем.

В системе Delta Design задержка распространения сигнала, обусловленная габаритными размерами корпуса, может быть определена в двух местах. Как уже упоминалось, значение задержки можно указать на этапе создания библиотечного представления компонента (см. рис. 1). Если величина задержки является значительной и ею нельзя пренебречь, а библиотечное описание компонента не содержит данного значения, то существует возможность отредактировать величину задержки непосредственно в схемотехническом редакторе. Для этого необходимо выбрать контакт или группу контактов на УГО компонента, а в панели «Свойства» → «Задержки» ввести требуемую величину.

Задержка сигнала, обусловленная геометрическими размерами контактной площадки (КП), вычисляется системой автоматически. Задержка зависит от того, каким способом трек был подключён к КП. Если трек был подключён к центру КП, то габаритные размеры КП не учитываются. Если же при прокладке печатного проводника пользователь выбирает режим подключения по периметру КП, то происходит вычисление кратчайшего пути от места подключения трека до центра КП.

Также автоматически в системе учитываются задержки, связанные с переходом сигнала с одного слоя на другой. Важным здесь является правильное формирование стека слоёв разрабатываемой платы. Для этого в системе реализован редактор слоёв, в котором разработчик может отобразить реальную конструкцию платы и учесть толщину каждого слоя.

Шаг 4. Трассировка печатных проводников

Способы трассировки высокочастотных цепей во многом зависят от навыков и опыта инженера-конструктора печатных плат. Однако в общем случае можно предположить, что трассировка будет происходить в несколько этапов: выбор группы сигналов, подсветка их в проекте платы, проведение треков с одновременным выравниванием длины, корректировка длины ранее проложенных треков.

В «Менеджере проекта» и «Редакторе правил» реализована возможность выбора и подсветки группы сигналов на схеме и плате, что позволяет быстро находить нужную группу сигналов и работать с ними.

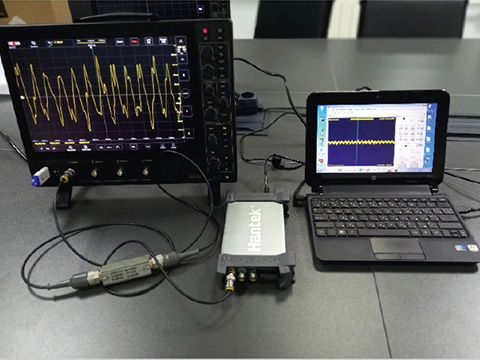

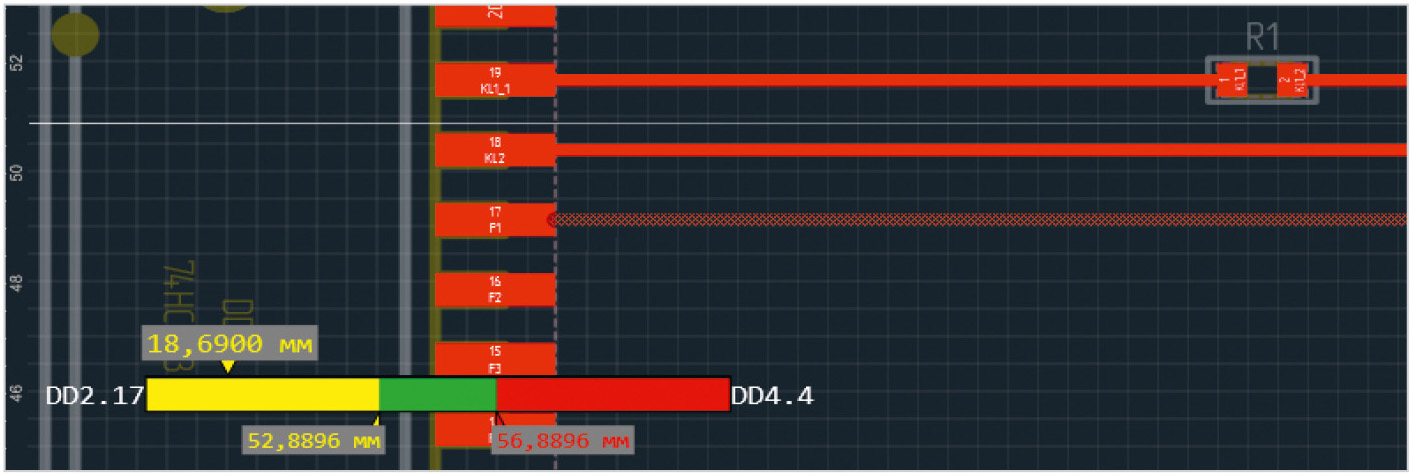

В процессе интерактивной трассировки в рабочем окне проекта отображается специализированная шкала длин сигналов (см. рис. 8).

Включение и выключение отображения шкалы длин происходит на панели управления: «Редактор печатных плат» → «Трассировка» → «Отображать шкалу длины трека». Шкала состоит из трёх зон. Жёлтая зона говорит о том, что длина трека не укладывается в допустимый диапазон длин, зелёная зона – трек попадает в доверительный интервал, в котором задержки соответствуют допуску, красная зона – длина трека выходит за допустимый диапазон длин (см. рис. 8).

Кроме расцвеченных зон на шкале также отображается и дополнительная информация: сверху отображается бегунок с меткой текущей длины трека, снизу отмечаются границы доверительного интервала, также на шкале отображаются имена источника и приёмника сигнала (см. рис. 8).

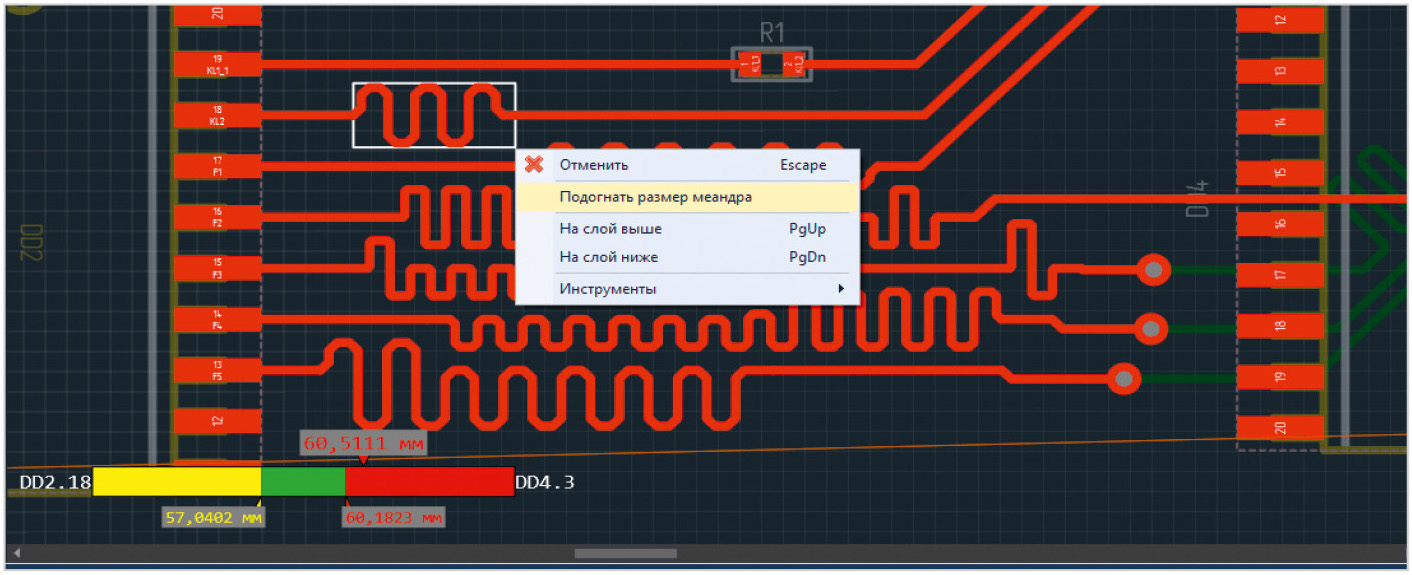

Использование меандров

Вероятность того, что все треки сигналов уложатся в доверительный интервал с первого раза, крайне мала. Поэтому в Delta Design реализован специализированный инструмент выравнивания – «Меандр». Данный инструмент позволяет пользователю нарисовать описывающий прямоугольник, внутри которого формируется меандр. Одновременно с построением меандра на треке в проекте также отображается и шкала контроля длины трека. Размер и форма меандра определяются размером и формой описывающего прямоугольника.

Так как построение полуволн меандра осуществляется дискретно, то для подгонки длины трека и попадания в зелёную зону в системе реализована команда «Подогнать размер меандра». Перед вызовом данной команды рекомендуется сформировать меандр с небольшим превышением длины, чтобы бегунок текущей длины на шкале контроля вышел за диапазон зелёной зоны и попал в красную зону. Вызов команды приведёт к тому, что система перестроит меандр так, чтобы длина трека попала точно в середину зелёной зоны (см. рис. 9).

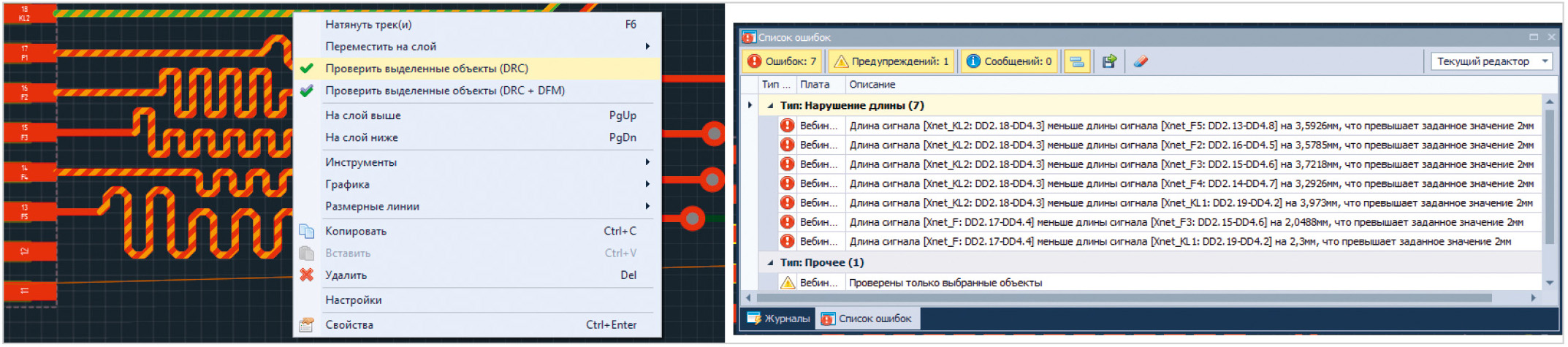

Запуск DRC-проверки

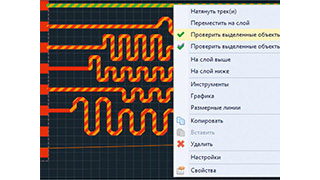

Для того чтобы убедиться в правильности созданной топологии печатных проводников, необходимо выполнить DRC-проверку платы. Проверка может быть запущена по всем объектам платы или же только по тем, которые были предварительно выбраны (см. рис. 10). Если длины треков цепей не укладываются в заданный диапазон, то в панели «Список ошибок» будет сформирован список с нарушениями длины.

После размещения на треке меандр продолжает оставаться единым объектом. Это позволяет быстро изменять размеры описывающего его прямоугольника и количество полуволн внутри прямоугольника. Тем самым можно быстро увеличивать или уменьшать суммарную длину всего трека. В системе реализован быстрый переход из панели «Список ошибок» в рабочее окно редактора ПП. Анализируя список ошибок и переключаясь между панелью ошибок и рабочим окном редактора ПП, разработчик может переходить к нужному треку (см. рис. 10) для его редактирования.

Заключение

В системе Delta Design версии 3.0 реализован широкий набор инструментов, который позволяет пользователям быстро разрабатывать проекты печатных платы высокоскоростных цифровых устройств. Успех применения разработанного инструментария во многом определяется выполнением рекомендаций для каждого этапа проектирования платы: создание библиотечного представления компонента, создание сигналов, наложение временных ограничений, выравнивание длин треков.

Если вам понравился материал, кликните значок — вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал —не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!