Выражение составных частей при помощи доступных имитатору базовых моделей

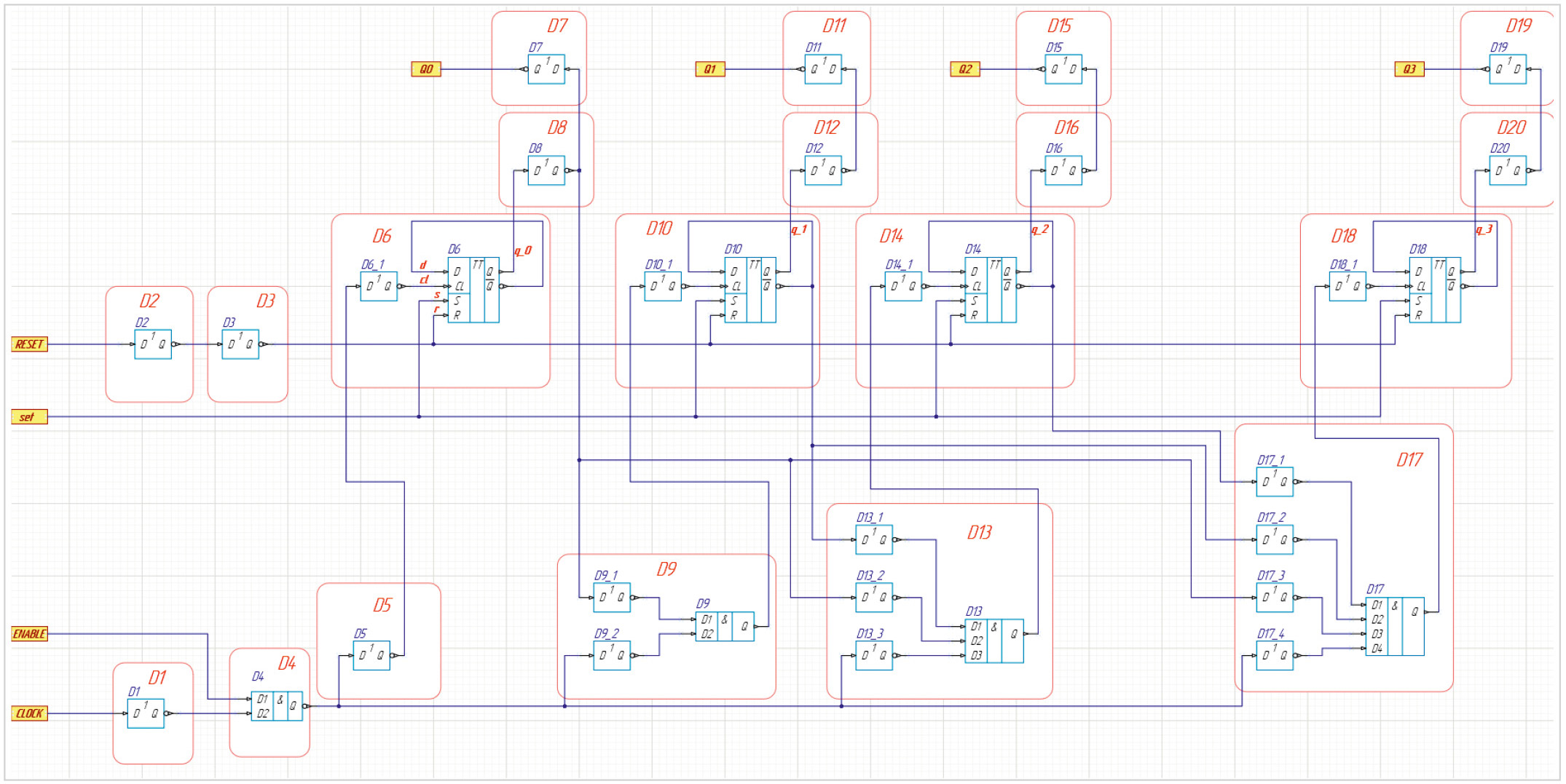

Буферные элементы с инверсией на входе и инверсией на выходе D1, D2, D3, D5, D7, D8, D11, D12, D15, D16, D19 и D20 эквивалентны между собой (см. рис. 1 [5]). Такие элементы можно реализовать моделью d_inverter.

Элементы D9, D13 и D17 (2НЕ–И, 3НЕ–И, 4НЕ–И) можно представить как суперпозиции инверторов и элементов 2И, 3И и 4И соответственно. Элементы 2И, 3И и 4И можно реализовать одной моделью d_and, так как эта модель имеет возможность векторного расширения входов.

Элементы D-триггеры (D6, D10, D14 и D18) можно представить моделями d_dff и инвертором для входа синхронизации, так как модель d_dff управляется положительным фронтом на входе синхронизации.

В имитаторе Altium Designer существуют две модели D-триггеров: d_dlatch – одноступенчатый D-триггер (защёлка) и d_dff – двухступенчатый D-триггер с динамической синхронизацией. Согласно техническому описанию микросхема MC14520B построена на основе двухступенчатых триггеров (D flip-flops) с динамической синхронизацией (edge-clocked) отрицательным фронтом сигнала.

Таким образом, логическая структура микросхемы должна быть немного преобразована (см. рис. 9): красными контурами и текстовыми метками красного цвета указаны элементы исходной схемы, представленной на рисунке 1 [5].

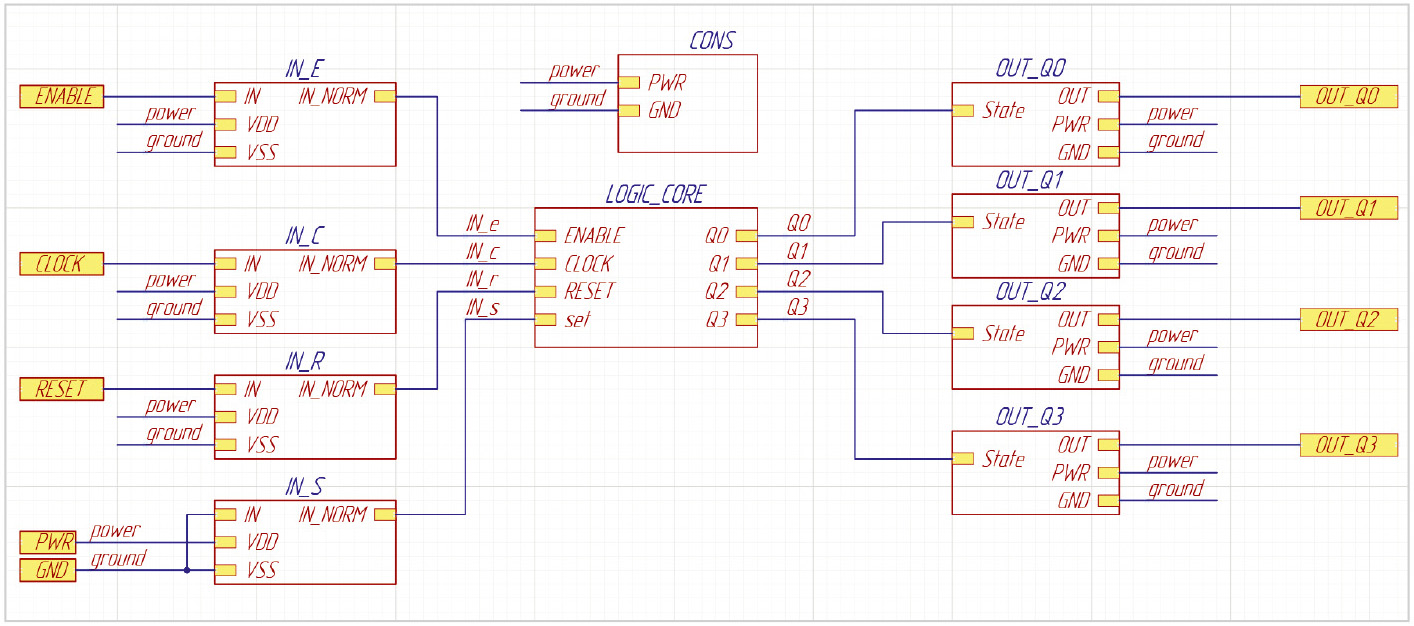

Структурная схема модели в иерархической форме представлена на рисунке 10.

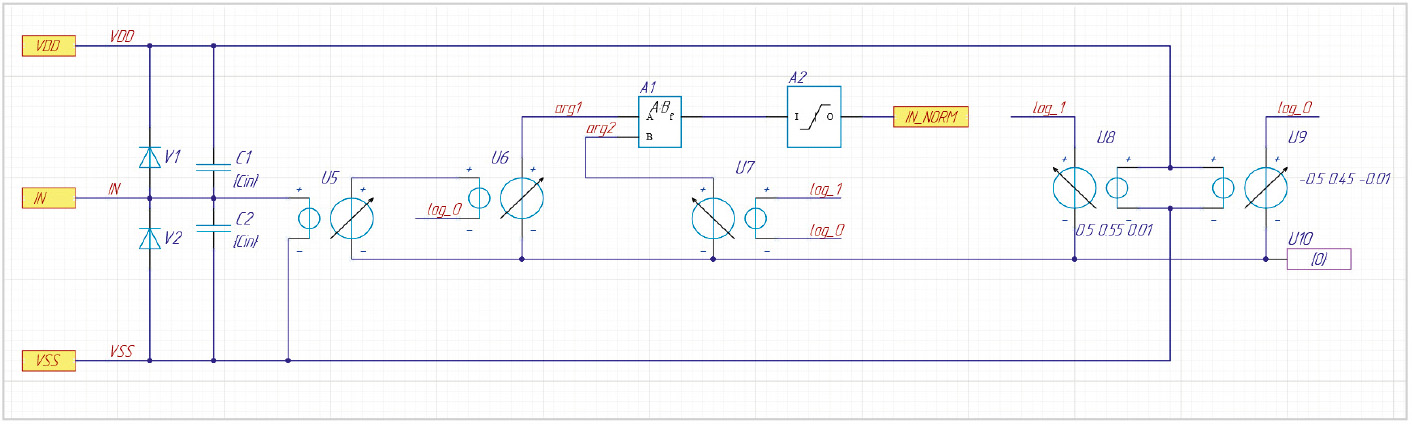

Функциональные группы IN_E, IN_C, IN_R, IN_S реализуют входные каскады микросхемы, схема замещения входного каскада представлена на рисунке 3 [5]. Функциональная группа CONS реализует узел регулирования зависимости потребления тока питания, схема замещения представлена на рисунке 8 [5]. Функциональная группа LOGIC_CORE реализует логическую структуру микросхемы, схема замещения представлена на рисунке 9. Функциональные группы OUT_Q0, OUT_Q1, OUT_Q2, OUT_Q3 реализуют выходные каскады микросхемы, схема замещения представлена на рисунке 5 [5].

Параметризация модели

Параметризация модели – это формирование зависимости функциональных качеств модели от определённых внешних параметров. В качестве элемента параметризации модели микросхемы следует определить возможность изменять значение входной ёмкости. Причина этого заключается в том, что в спецификации указано предельное значение для входной ёмкости, которое, как часто бывает, превосходит величину ёмкости в реальной микросхеме. Возможность менять входную ёмкость делает модель более гибкой и позволяет предоставить пользователю больше вариантов в применении модели. Это позволяет выполнить расчёты как для модели прибора предельного случая, так и для модели, приближенной к нормальной.

Рассмотрение параметризации модели не является строго необходимым процессом в случае рассматриваемой микросхемы MC14520B, однако может быть чрезвычайно важным для построения серии связанных моделей, например для целой серии логических микросхем. Параметризация модели в таком случае позволяет изменить функциональные характеристики без необходимости углубляться в редактирование файлов определения модели. В данном случае параметризация входной ёмкости микросхемы рассматривается в качестве примера.

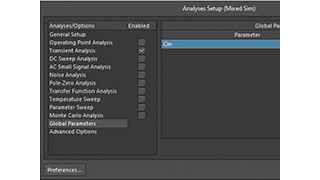

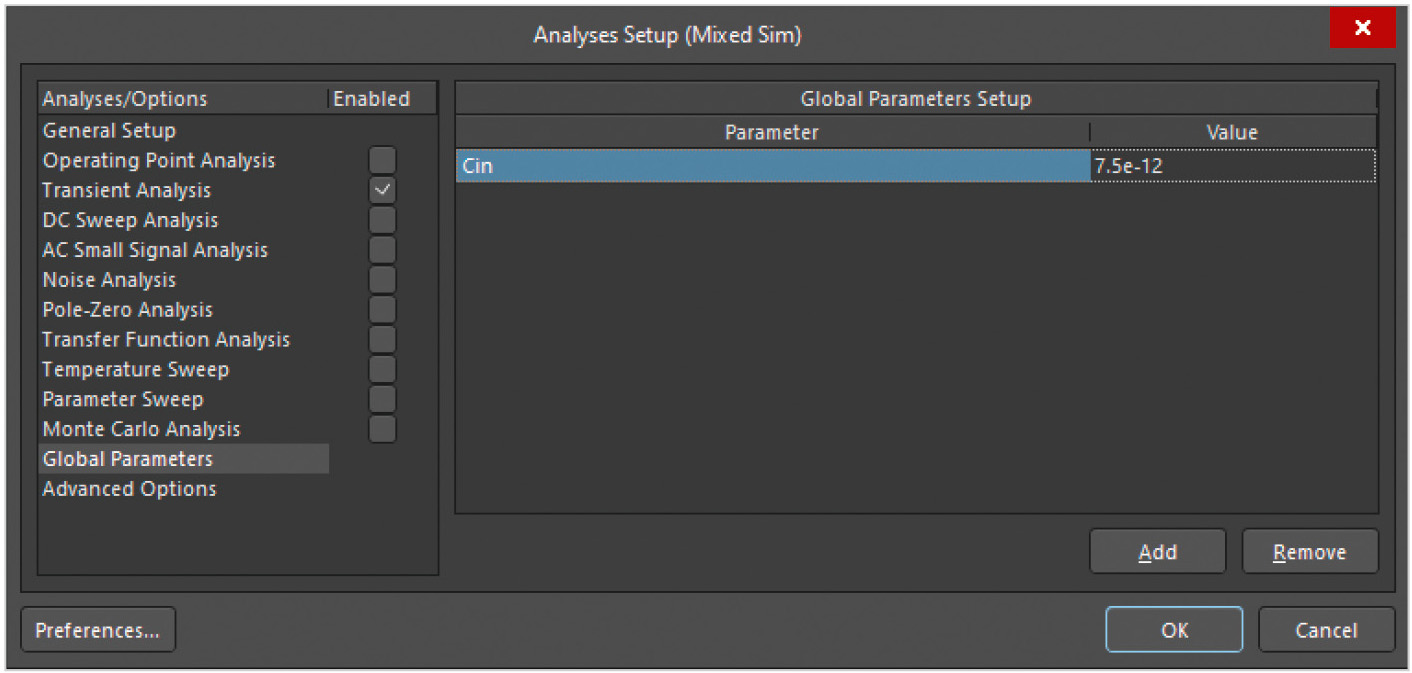

Выберем параметр Cin в окне Analyses Setup на вкладке Global Parameters со значением 7,5×10–12, что соответствует 7,5 пФ (см. рис. 11). Определим параметрическую зависимость конденсаторов C1 и C2 входного каскада, указав в качестве значения {Cin} (см. рис. 12). Теперь при необходимости изменить входную ёмкость достаточно будет переопределить значение ссылочного параметра без изменения схемы. Наибольший эффект параметризация даст при переходе от схемы замещения к SPICE-коду, что будет показано далее.

Идентификация параметров модели

Идентификация параметров модели сводится к определению параметров на основании доступных сведений из спецификации моделируемого устройства или результатов измерений.

В настоящем случае известно значение максимальной входной ёмкости из спецификации микросхемы. Ранее эти сведения уже были использованы для определения параметра Cin.

Верификация модели

Верификация модели подразумевает проверку её функциональных качеств с помощью внешних воздействий. В данном случае следует проверить характеристики функциональных групп каждого вида, которые участвуют в построении структуры модели микросхемы: функциональные группы входа, выхода, узла регулирования тока питания и логической структуры.

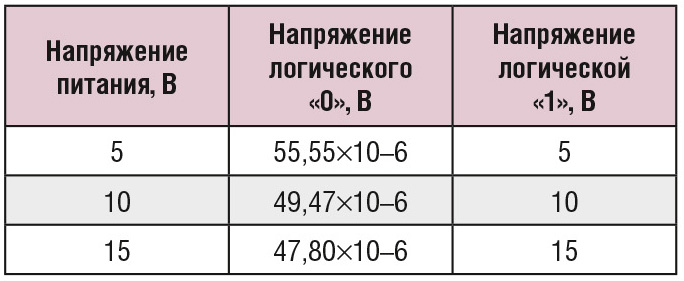

Для верификации схемы удобно воспользоваться иерархической формой представления схемы включения и представить микросхему в виде самостоятельной функциональной группы (см. рис. 13).

Верификация функциональной группы входа микросхемы

Верификации функциональной группы входа подлежит зависимость напряжения логического «0» и логической «1» от напряжения питания.

Из спецификации известны значения предельных напряжений срабатывания для напряжения питания 5, 10 и 15 В. Верификацию входа удобно выполнять в режиме расчёта постоянного тока (DC Sweep). В качестве варьируемого источника следует указать источник G1.

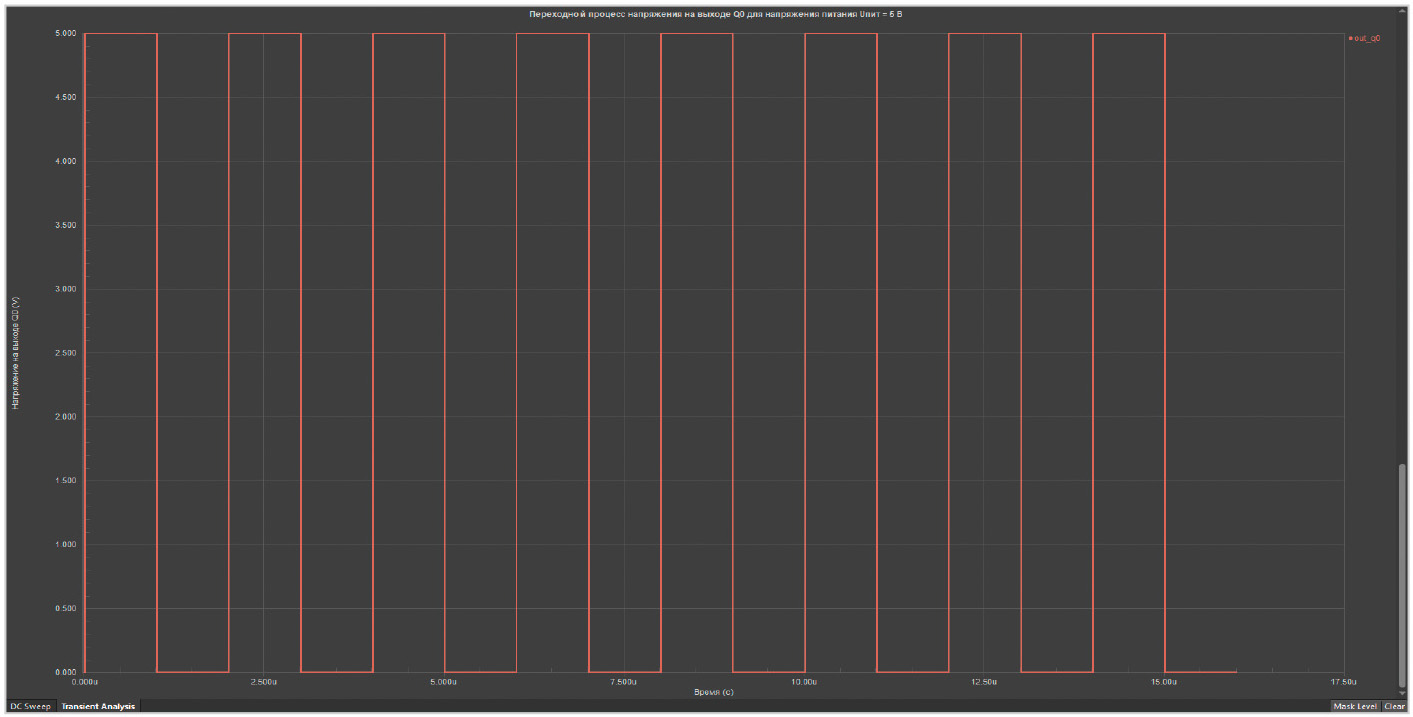

Результаты расчёта сведены в таблице 8. Если сравнить таблицы 2 [5] и 8, то можно увидеть, что существует совпадение исходных и достигнутых значений зависимости входного напряжения от напряжения питания. На этом основании верификацию функциональной группы входа следует считать положительной.

Верификация функциональной группы выхода микросхемы

Верификации функциональной группы выхода подлежат два типа характеристик:

- зависимости выходного напряжения для разомкнутой цепи выхода при логическом «0» и логической «1» на выходе для напряжения питания 5, 10 и 15 В;

- зависимости выходного тока от напряжения для замкнутой цепи при логическом «0» и логической «1» на выходе для напряжения питания 5, 10 и 15 В.

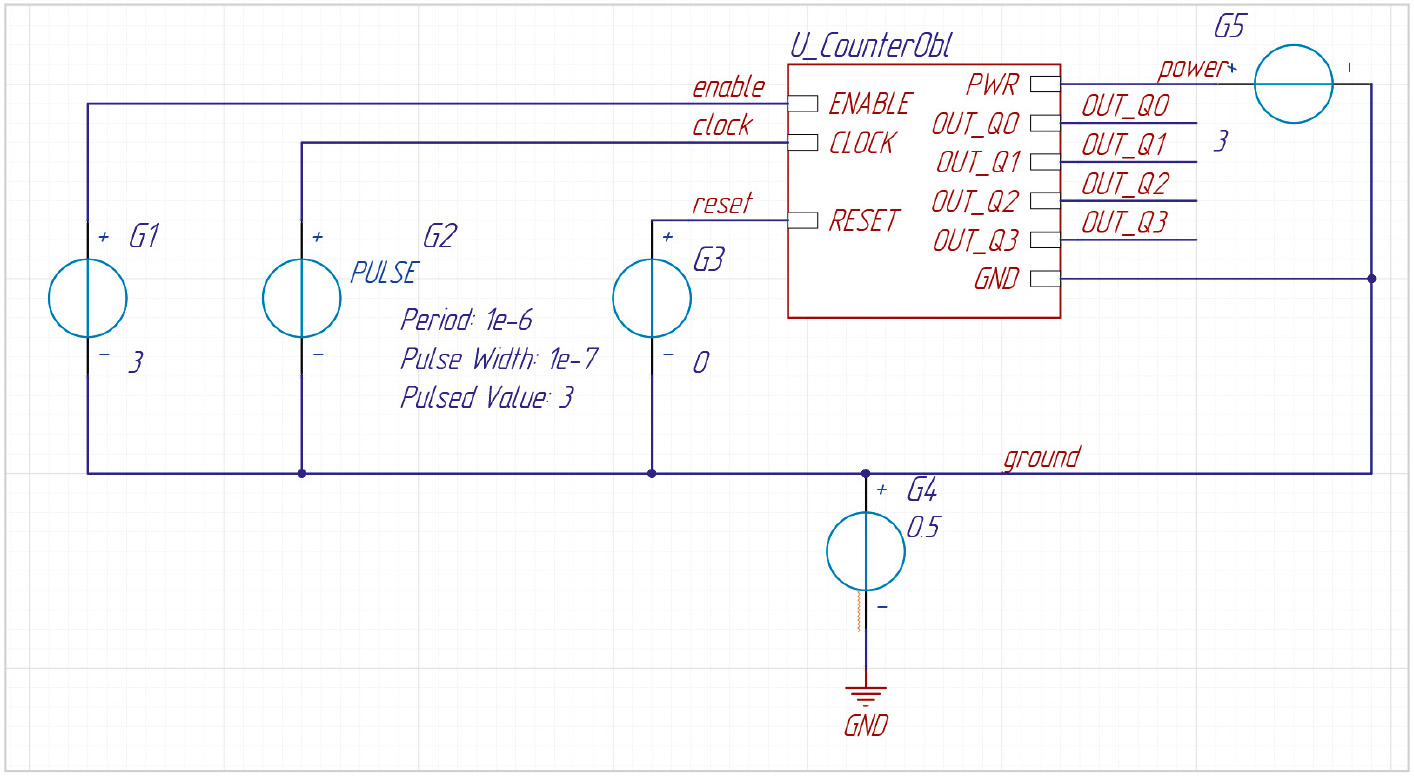

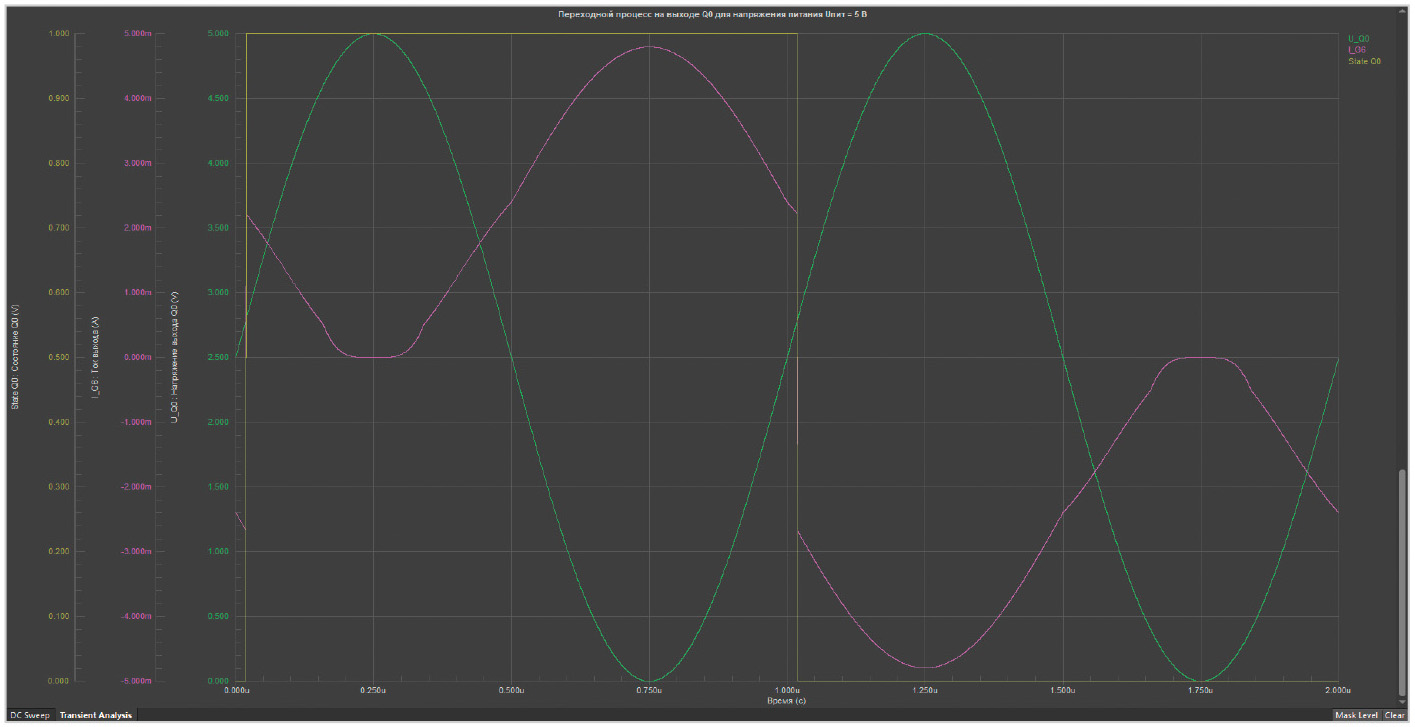

Для проверки первого пункта воспользуемся схемой включения, которая приведена на рисунке 13. В данном случае удобно использовать расчёт переходного процесса для просмотра и отображения характеристики выходного напряжения, максимальное напряжение источников G1, G2 и G3 должно соответствовать источнику G5. Вычисленная характеристика переходного процесса выходного напряжения выхода Q0 для напряжения питания 5 В приведена на рисунке 14 (для напряжения питания 10 и 15 В форма графиков похожа).

Результаты измерений для указанных характеристик для напряжения питания 5, 10 и 15 В соответственно можно свести в таблицу 9.

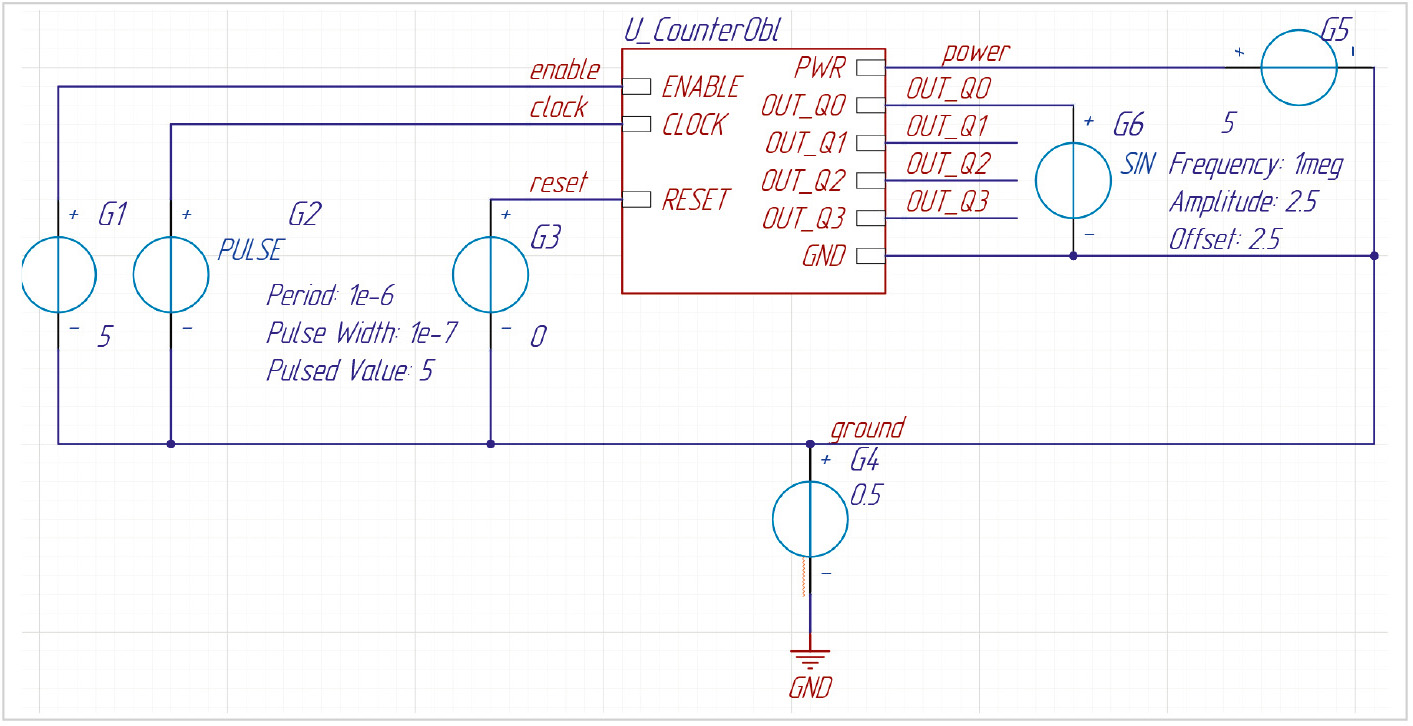

Для проверки второго пункта немного модифицируем схему включения, добавив источник переменного напряжения к выходу Q0 микросхемы (см. рис. 15).

В данном случае для верификации удобно использовать расчёт переходного процесса. Выходные характеристики выхода микросхемы для напряжения питания 5 В представлены на рисунке 16 (для напряжения питания 10 и 15 В графики различаются только значениями параметров).

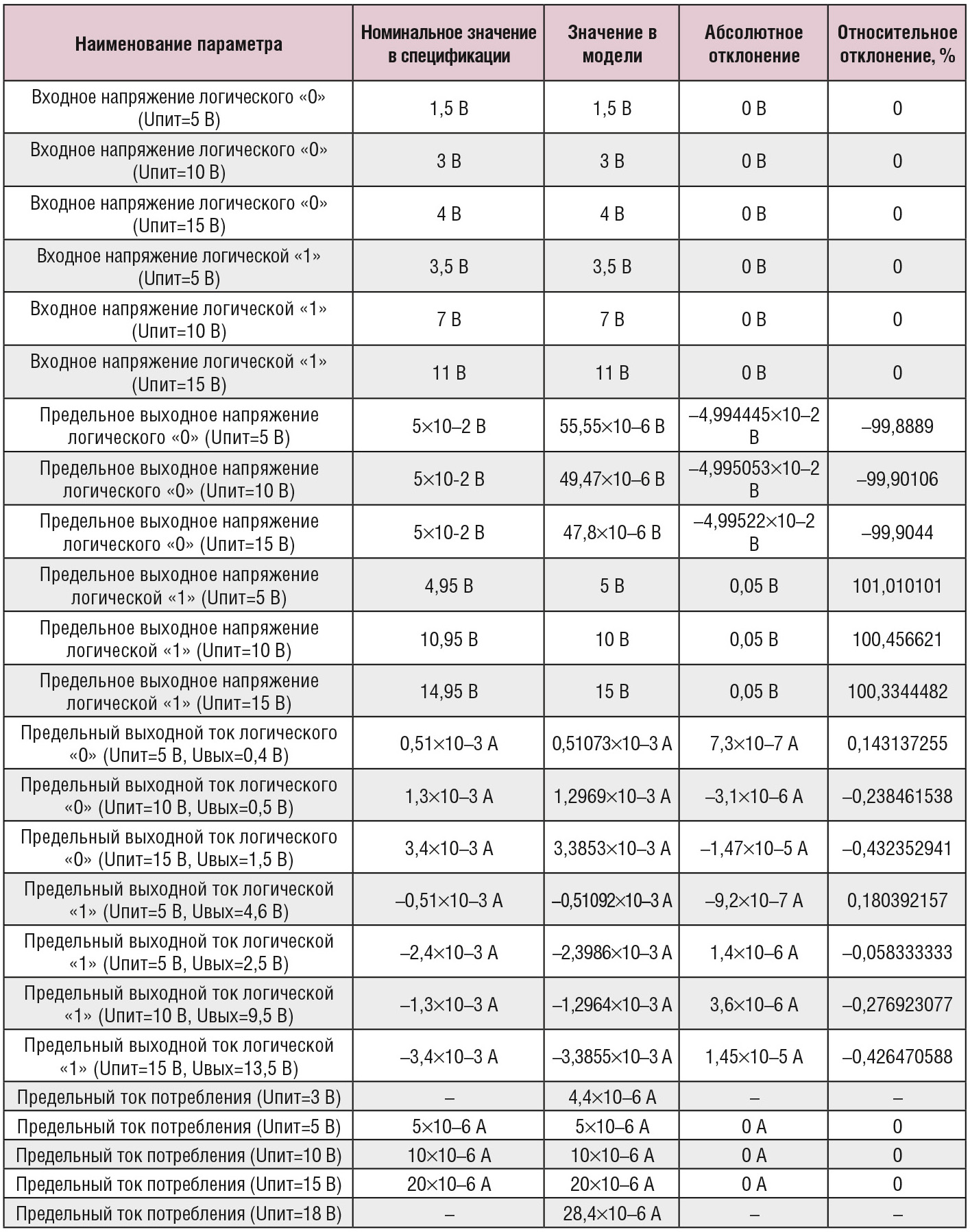

С использованием средств измерения Sim Data для анализа результатов расчётов имитатора электрических цепей Altium Designer получены результаты для условий, приведённых в таблице 4 [5]. Результаты измерений удобно представить в таблице 10.

Если сравнить таблицы 4 [5] и 10, то можно увидеть, что достигнутые значения предельных выходных напряжений близки к границам, указанным в спецификации микросхемы, но различаются по знаку. Причина различия в том, что источник напряжения G6, используемый в схеме включения в качестве датчика тока, показывает положительный ток при его втекании через контакт положительной полярности и, наоборот, отрицательный ток при истекании из вывода положительной полярности. На этом основании верификацию функциональной группы выхода следует считать положительной.

Верификация функциональной группы узла регулирования тока питания

Рассмотрим верификацию функциональной группы узла регулирования тока питания. Верификации подлежит предельный ток потребления питания в статическом режиме без нагрузки на выходах.

Результаты измерений можно свести в таблицу 11.

Данные таблицы 11 полностью повторяют данные таблицы 7 [5], поскольку электрическая схема узла регулирования тока потребления питания полностью определяется заложенной функциональной зависимостью одного элемента – зависимого источника тока. В случае другой реализации электрической цепи узла регулирования тока питания целевые и результативные данные могут не совпадать в точности из-за влияния других элементов. Так, на основании совпадения данных таблиц 7 [5] и 11 верификацию функциональной группы узла регулирования тока питания можно считать положительной.

Формирование паспорта модели

Паспорт модели – это сводка, отражающая достигнутые в модели характеристики, а также условия применения модели – её потребительские качества.

В случае разработанной модели микросхемы MC14520B следует указать, что модель разработана без учёта влияния температуры на характеристики, не отражает временны¢е характеристики задержки передачи сигнала от входа к выходу (их достаточно просто настроить в функциональной группе логической структуры, поэтому не изложено в статье), также могут быть даны статистические оценки (если есть достаточно большой объём входных данных).

Как правило, в паспорт модели следует поместить сравнительные значения для исходных данных и достигнутые моделью результаты (см. табл. 12).

Сведения таблицы 12 можно распространять несколькими способами: поместить в отдельный файл и распространять с файлом модели или поместить непосредственно в файл модели. Во втором случае следует учесть, что использование символов кириллицы, вероятнее всего, вызовет проблему при чтении файла имитатором, поэтому следует использовать символы латинского алфавита: слова перевести на английский язык (если модель может быть распространена за пределы стран СНГ) или реализовать с помощью транслита – написания русских слов с использованием букв латинского алфавита.

В третьей части статьи будет подробна описана разработка компонента интегрированной библиотеки.

Литература

- Леган Ю. Разработка модели цифрового компонента в Altium Designer. Часть 1. Современная электроника. 2020. № 7.

- Библиотека базовых моделей Sim Lib GOST. URL: https://www.altium-ru.com/sites/default/files/attachments/Sim%20Lib%20GOST.zip.

- Расширение функциональных возможностей Altium Designer. URL: https://www.altium.com/ru/documentation/altium-designer/extending-altium-designer.

- Altium Mixed Sim. Руководство пользователя Altium Designer. URL: https://resources.altium.com/sites/default/files/2020-05/Altium Mixed Sim - Руководство пользователя Altium Designer.pdf.

- MC14518B, MC14520B. Dual up counter. Сайт компании On Semiconductor (лист спецификации в формате pdf): https://www.onsemi.com/pub/Collateral/MC14518B-D.PDF.

Если вам понравился материал, кликните значок - вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал - не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!