Введение

Основной задачей моделирования смешанных электрических цепей с помощью имитатора является расчёт переходного процесса и анализ результатов. Расчёт переходного процесса имеет несколько параметров: начальное время, конечное время и шаг времени переходного процесса.

При выборе параметров расчёта переходного процесса следует руководствоваться следующими критериями: искомый переходный процесс должен быть представлен на временно¢й оси, шаг моделирования должен быть минимум в 2 раза меньше времени самого быстротекущего явления переходного процесса. Требование к шагу моделирования диктуется теоремой Котельникова.

Возможности Altium Designer для имитации смешанных электрических цепей

Altium Designer имеет интегрированный имитатор электрических цепей со смешанными сигналами, который реализуется дополнительным системным модулем Mixed Simulation. Дополнительность системного модуля говорит о том, что модуль доступен для установки, однако при начальной установке Altium Designer может быть исключён из программы инсталляции. Системный модуль имитатора электрических цепей может быть установлен в любой момент при доступе к установщику Altium Designer. Дополнительную установку системного модуля [1] можно сделать как с помощью пакета офлайн-инсталляции, так и при подключении к учётной записи AltiumLive через сеть Интернет.

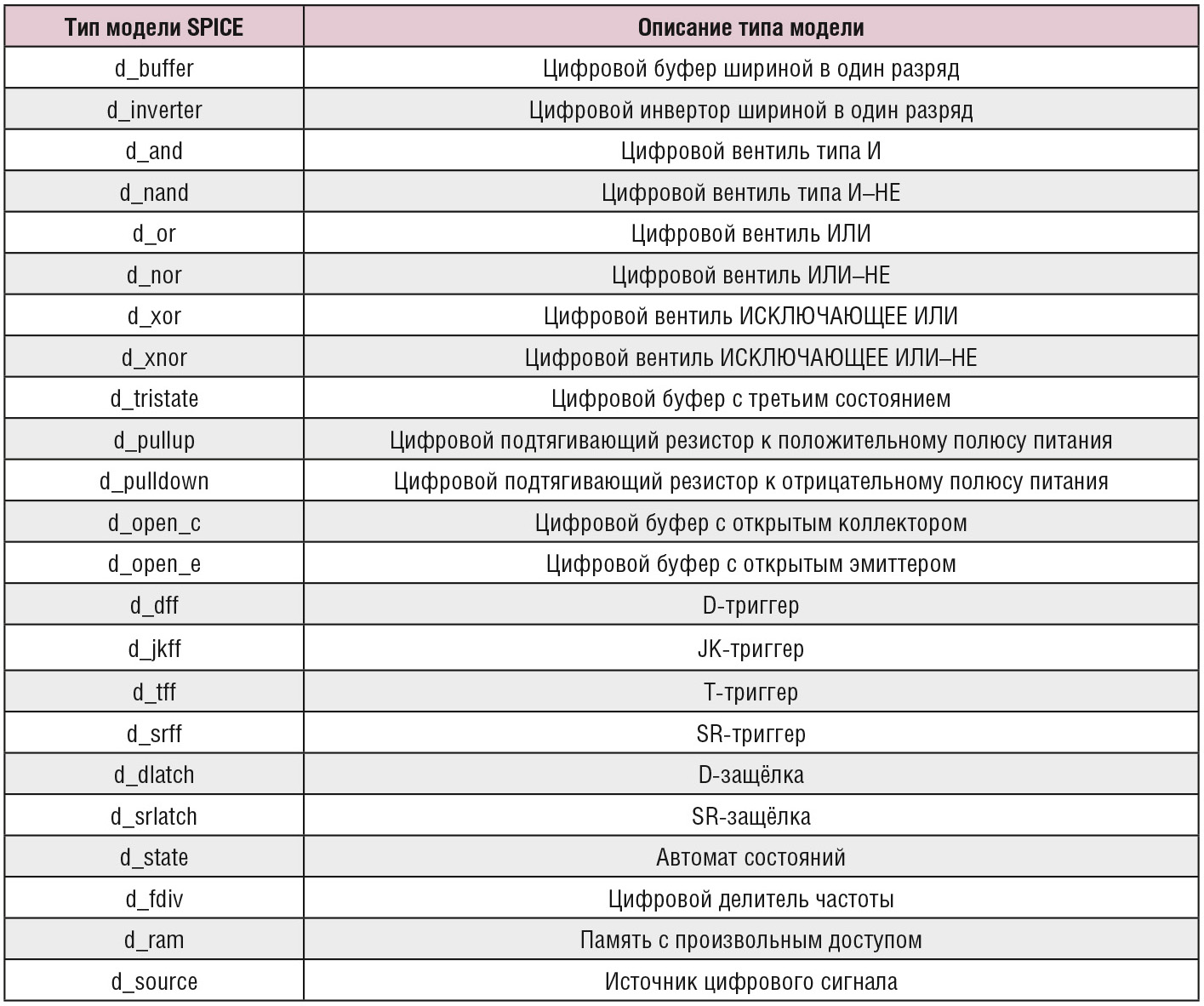

Имитатор электрических цепей Altium Designer позволяет выполнять моделирование цепей со смешанными сигналами, имеет встроенную поддержку моделей логических устройств. Перечень базовых моделей логических устройств имитатора приведён в таблице 1.

С полным перечнем поддерживаемых моделей имитатора электрических цепей Altium Designer можно ознакомиться в руководстве пользователя имитатора Altium Mixed Sim на русском языке [2].

Модели более сложных логических устройств должны быть построены на основе перечисленных базовых моделей.

Описание процесса разработки модели четырёхразрядного счётчика

Рассмотрим процесс разработки модели логического устройства – микросхемы четырёхразрядного счётчика Motorola MC14520B. Процесс разработки составной (сложной) модели состоит из нескольких этапов:

- поиск информации;

- построение структуры модели;

- выражение составных частей через модели имитатора;

- параметризация модели;

- идентификация параметров модели;

- верификация модели;

- формирование паспорта модели;

- разработка компонента интегрированной библиотеки.

Поиск информации

Началом разработки модели является сбор и анализ информации об объекте моделирования. Основой для разработки моделей могут стать открытые источники информации о компонентах, например спецификация фирмы изготовителя. От разработчика модели требуется: определить структуру составных частей модели, выразить составные части при помощи доступных имитатору базовых моделей, выполнить параметризацию модели (если требуется), выполнить идентификацию параметров модели, произвести верификацию, сформировать паспорт модели для её пользователей.

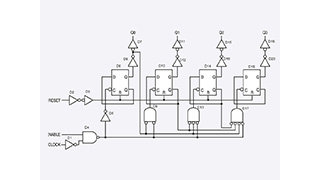

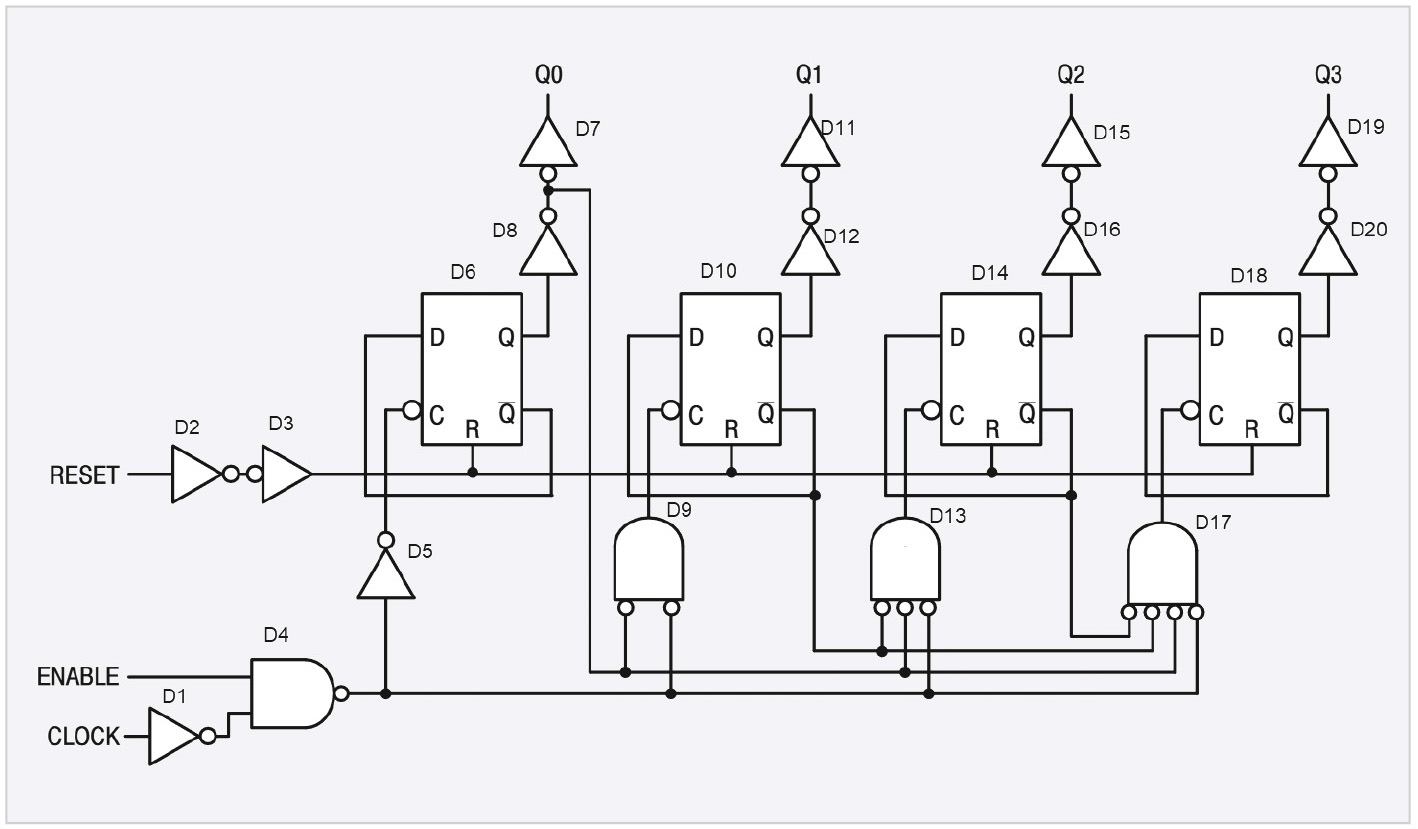

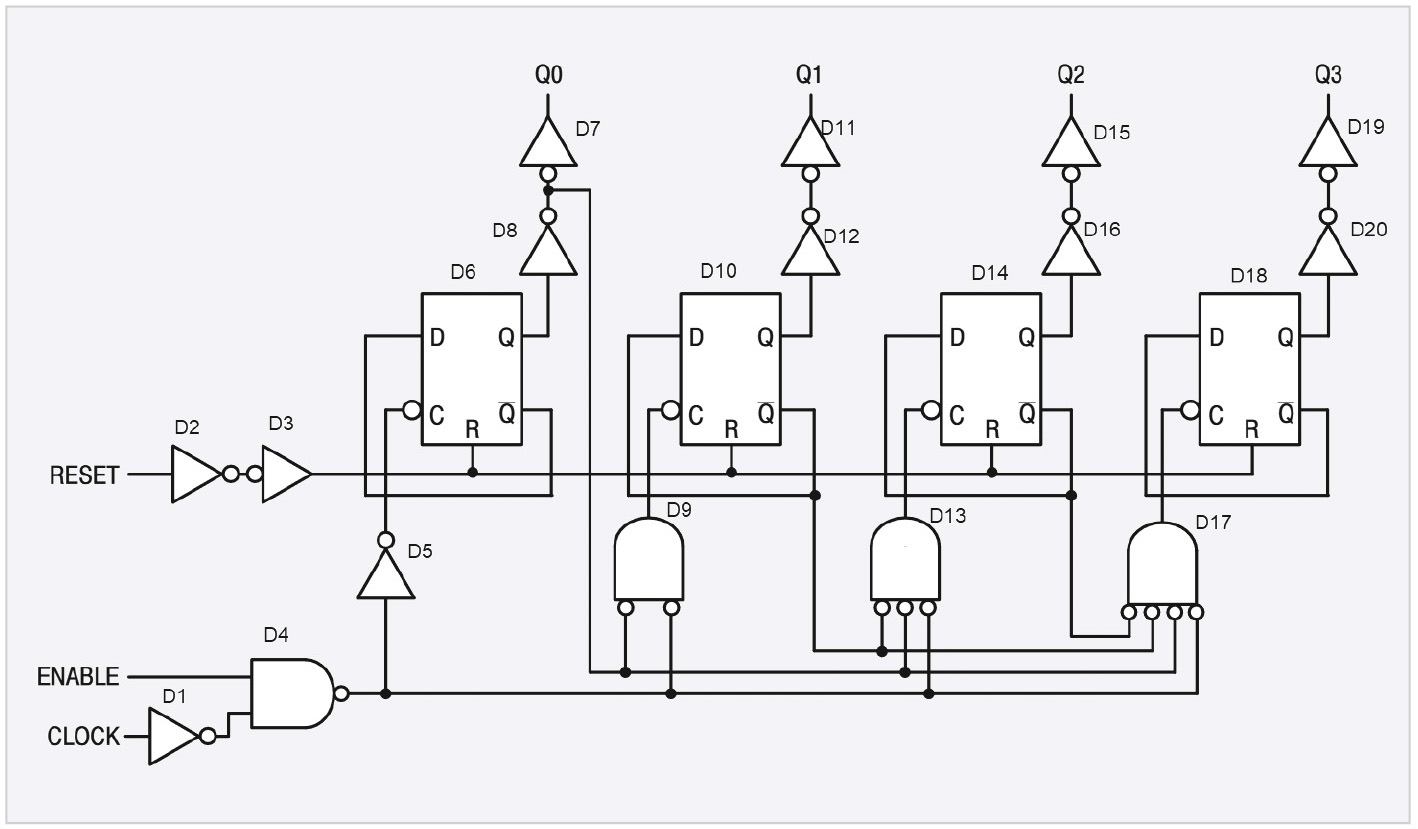

В спецификации микросхемы MC14520B [3] указано, что она представляет собой сдвоенный четырёхразрядный счётчик импульсов с входами сброса и установки. На рисунке 1 представлена логическая схема половины счётчика. Этот рисунок будет являться основой для построения структуры модели счётчика.

Построение структуры модели

Логическая структура

Логическая структура, предлагаемая в спецификации, содержит следующие элементы:

- инвертор с инверсией на выходе;

- инвертор с инверсией на входе;

- элемент 2И–НЕ;

- элемент 2НЕ–И;

- элемент 3НЕ–И;

- элемент 4НЕ–И;

- динамический D-триггер с инверсией на входе C.

Необходимо выразить элементы логической структуры через базовые логические элементы, поддерживаемые имитатором. Рисунок, приведённый в спецификации, не содержит условных текстовых обозначений элементов, поэтому для улучшения изложения введём обозначения D1…D20 (см. рис. 1), а логическая схема будет выражена в виде принципиальной электрической схемы в Altium Designer.

Поскольку прямые соответствия некоторым элементам логической схемы среди базовых моделей логических устройств имитатора установить невозможно, то придётся выразить таковые элементы через композицию базовых моделей. Это несколько меняет логическую схему, что может повлиять на задержки сигналов, поскольку в имитаторе каждая модель логического устройства имеет ненулевую задержку распространения. Для парирования дополнительной задержки распространения в электрической цепи можно применить один из двух приёмов: уменьшить задержку последующего элемента по пути распространения сигнала или добавить аналогичные элементы задержки в параллельные участки электрической цепи. Первый способ позволяет явно парировать задержку, второй способ предоставляет возможность выполнить выравнивание задержки на параллельных участках. При выполнении компенсации задержки следует отдать приоритет первому способу по той причине, что он связан с изменением параметров существующих элементов и не требует добавления дополнительных элементов, что снижает временные издержки на выполнение расчёта, так как не приводит к излишнему увеличению сложности электрической цепи.

При разработке структуры модели рекомендуется ориентироваться на допустимые значения электрических и временны¢х параметров, соответствующих рабочей температуре +25°C. В спецификации указано, что типичные значения электрических параметров не должны использоваться при решении задач проектирования, а указаны для демонстрации потенциальной производительности микросхемы.

Структура входов

Информация о технологии изготовления и внутреннем устройстве микросхемы может быть использована для формирования структуры входов и выходов микросхемы.

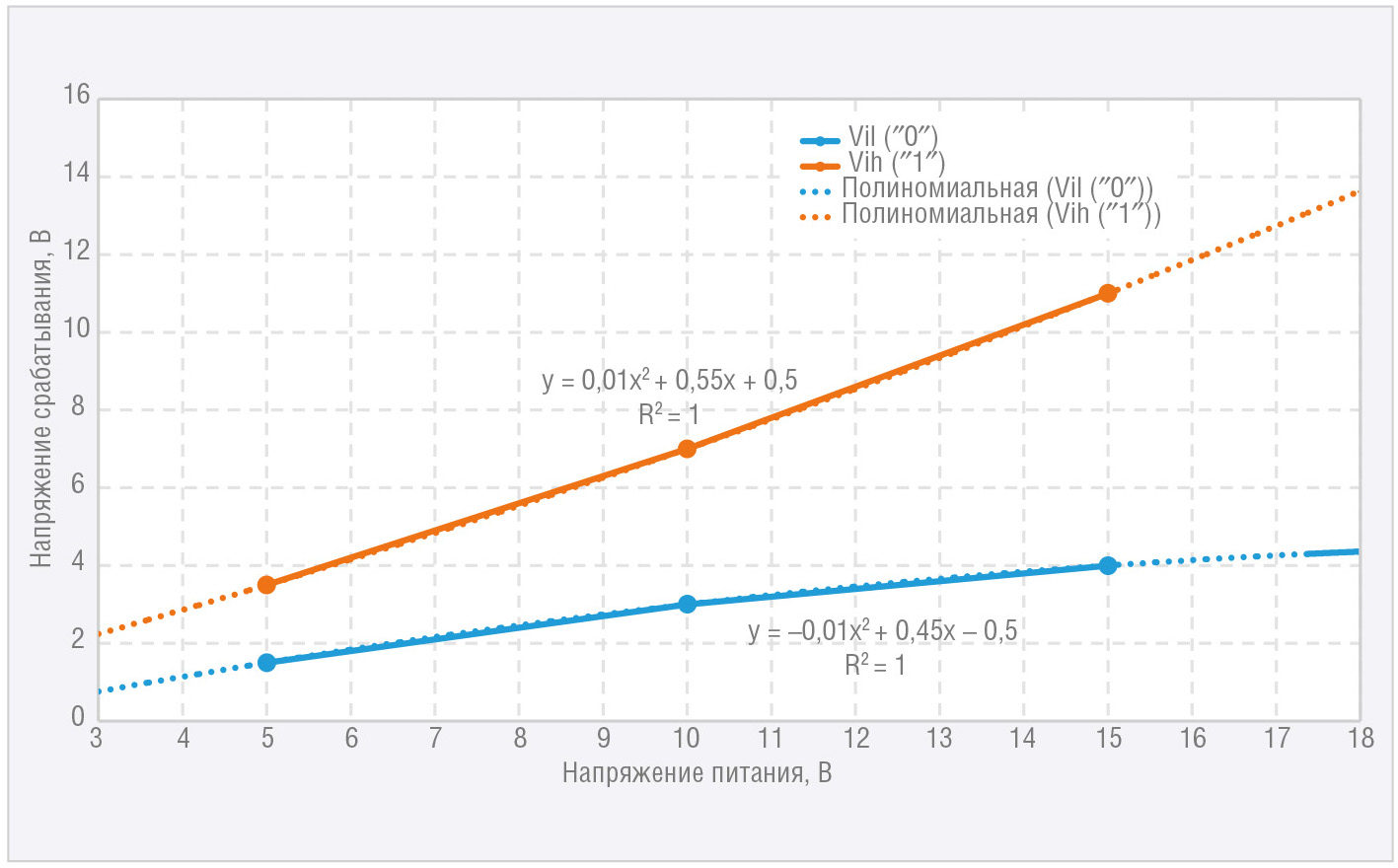

В спецификации указано, что микросхема изготавливается по КМОП-технологии с P- и N-канальными транзисторами. Все входы имеют диодную защиту. Допустимый диапазон напряжения питания от 3 до 18 В. В спецификации указано, что входное напряжение зависит от напряжения питания микросхемы (см. табл. 2).

Входы микросхемы имеют предельную ёмкость 7,5 пкФ. Предельный постоянный ток потребления для входов указан равным 0,1 мкА при напряжении питания 15 В.

Таким образом, для формирования структуры входа следует разработать схему замещения, которая должна быть чувствительна к напряжению питания, а также иметь диодную защиту. К сожалению, в спецификации отсутствует детальная информация о напряжении срабатывания входов от напряжения для типичной микросхемы, а приведены только предельные значения.

Если построить зависимость напряжения срабатывания входа от напряжения питания (см. рис. 2), то можно увидеть, что кривая зависимости меняет свой наклон примерно в области 10 В. Эти характеристики можно аппроксимировать при помощи полинома второй степени (см. линии тренда на рисунке 2). При этом для трёх точек коэффициент корреляции получается равным 1, и применение полинома более высокой степени не является целесообразным. Полиномиальные функции следует использовать в качестве порога для сравнения входного напряжения и формирования логического состояния в выходном каскаде схемы замещения входа микросхемы.

Для формирования порогового сигнала можно использовать упрощающие приёмы, например кусочно-линейную функцию, определяемую таблицей значений координат точек. Кусочно-линейная функция ограничивает значения функции координатами точек, заданными на концах. Поскольку данные о напряжении срабатывания входов известны только для напряжения питания от 5 до 15 В, а допустимое напряжение питания составляет от 3 до 18 В, то применение кусочно-линейной функции в данных условиях не позволит выполнить экстраполяцию при напряжении питания от 3 до 5 В и от 15 до 18 В. В сравнении с кусочно-линейной функцией использование полиномиальной функции позволяет выполнять расчёт порога срабатывания для какого угодно напряжения питания.

При разработке модели часто применяется приём нормирования сигналов таким образом, чтобы логическая структура модели не была чувствительна к напряжению питания микросхемы, а пороги срабатывания входов и выходов масштабировались в зависимости от него. Таким образом, целесообразно определить для напряжения срабатывания, соответствующего логическому «0», величину 0 В, а для соответствующего логической «1» – величину 1 В. Исходя из этого допущения, необходимо добавить в модель входа элемент сравнения, выходное значение которого будет нормировано на указанный диапазон и приведено к потенциалу базовой цепи 0, относительно которой работают базовые модели логических устройств.

Учитывая, что микросхема изготавливается по КМОП-технологии, можно утверждать, что собственное входное сопротивление внутренних цепей микросхемы чрезвычайно велико. Таким образом, ток потребления входов обеспечивается утечками в их элементах защиты. На это косвенно указывают сведения, приведённые в спецификации: допустимое входное напряжение составляет от VSS –0,5 В до VDD +0,5 В, ток потребления входов составляет ±0,1 мкА при напряжении питания 15 В. Указанные свойства характерны для маломощных импульсных диодов, которые действительно могли быть изготовлены на едином кристалле микросхемы вместе с логической частью. Исходя из этого предположения и для избегания чрезмерного усложнения модели микросхемы, при верификации достаточно выполнить только оценку тока потребления входов без необходимости точной имитации этого эффекта.

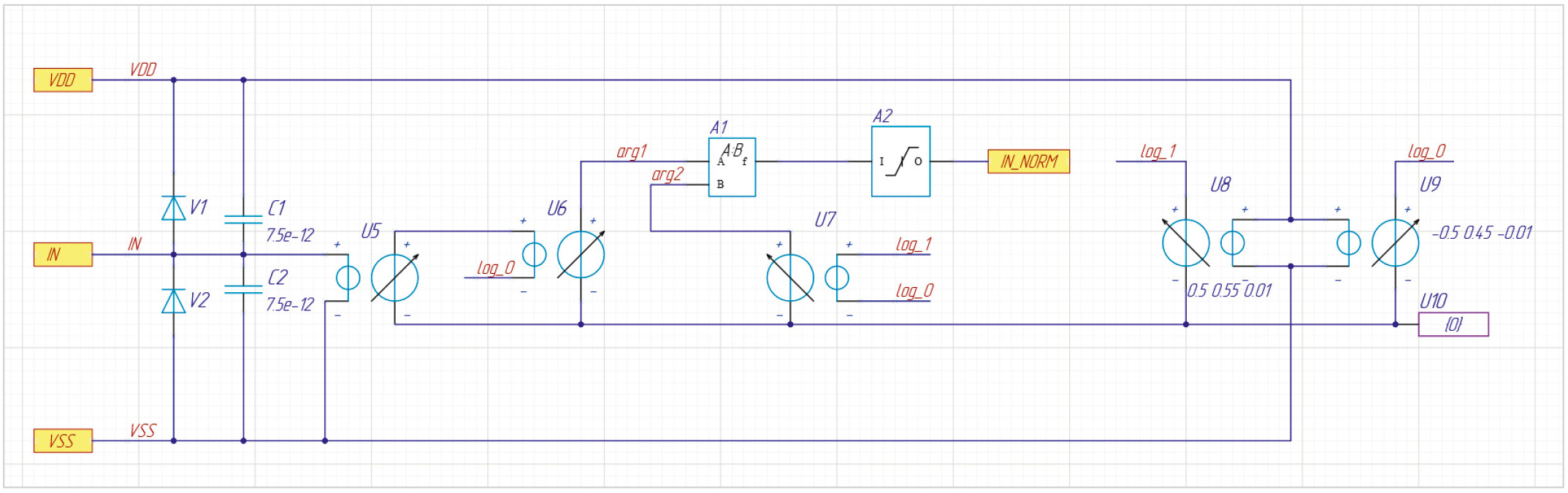

Таким образом, схема замещения входа микросхемы должна принять законченный вид (см. рис. 3). Элементы V1 и V2 реализуют диодную защиту. Элементы C1 и C2 реализуют входную ёмкость. Элементы U8 и U9 формируют пороговые напряжения логической «1» и логического «0» соответственно. Элемент U5 реализует перенос сигнала с потенциала узла VSS на потенциал базового узла 0. Элементы U6, U7, A1 (делитель) и A2 (ограничитель) выполняют нормализацию и приведение сигнала к диапазону от 0 до 1 В для последующей обработки логической структурой микросхемы. При этом уровню 0 В соответствует логический «0», а уровню 1 В – логическая «1».

Структура выходов

В спецификации указано, что все выходы имеют предельную нагрузочную способность до 10 мА постоянного тока.

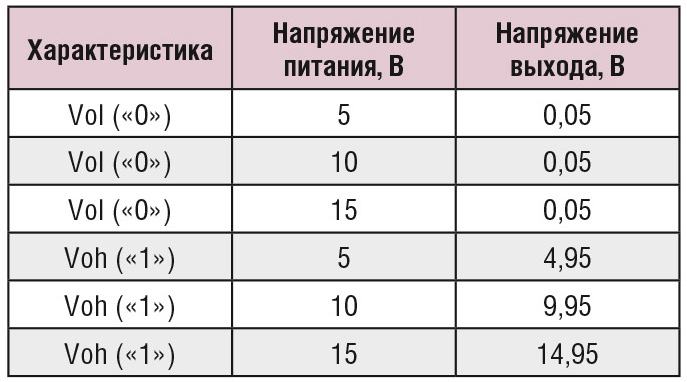

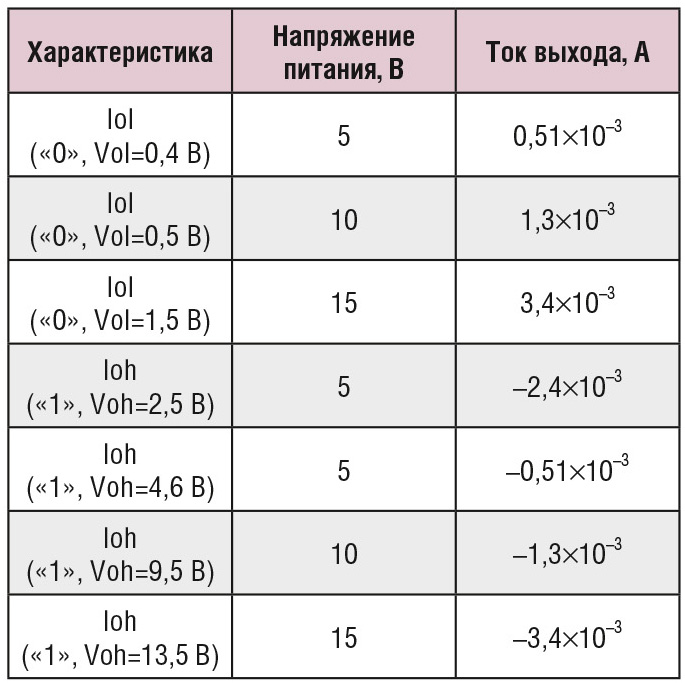

Выходное напряжение для выходов (см. табл. 3) имеет зависимость от напряжения питания. Нагрузочная способность по току для выходов (см. табл. 4) имеет зависимость от напряжения питания. Сведения из таблиц 3 и 4 предоставляют информацию о предельных вольт-амперных характеристиках (ВАХ) выходов микросхемы в зависимости от напряжения питания.

Для имитации указанных характеристик удобно применить источники тока, управляемые напряжением. Микросхема имеет выходы активного типа. Это значит, что схема замещения такого выхода должна иметь два «плеча»: верхнее плечо имитирует P-канальный транзистор, исток которого соединён с цепью питания положительной полярности; нижнее плечо имитирует N-канальный транзистор, исток которого соединён с цепью питания отрицательной полярности.

Обозначим нагрузочную характеристику выхода как Iвых и представим как линейную независимую суперпозицию функций, зависящих от напряжения на выходе, напряжения питания и требуемого логического состояния. Для верхнего плеча функция выходного тока принимает вид: Iвых_вп(Uвых, Uпит) = f(Uпит – Uвых) × g(Uпит) × Log1. Для нижнего плеча: Iвых_вп (Uвых, Uпит, Log0) = f(Uвых) × g(Uпит) × Log0. Функции f и g – некоторые произвольные линейно независимые функции, которые определяют зависимость от напряжения на выходе и напряжения питания. Функции Log0 и Log1 определяют требуемое логическое состояние выхода (Log0 = 1, если выход должен принять состояние логический «0», и Log0 = 0 – для логической «1»;

Log1=1, если выход должен принять состояние логическая «1», и Log1 = 0 для – логического «0»). Имея подобное представление, можно подобрать функции f и g такими, чтобы функция выходного тока соответствовала фактической выходной характеристике микросхемы наилучшим образом. Для точной идентификации функций f и g необходимо обладать массивом экспериментальных данных. Так как в текущем случае разработка модели ведётся только по сведениям из спецификации, представляющей предельные допустимые значения величин, и чрезвычайно высокая точность результата не требуется, достаточно попасть в порядок величины выходного тока, то функции f и g допустимо аппроксимировать полиномами первой или второй степени.

Из принятых определений для Iвых_вп и Iвых_нп видно, что функция g является общей для верхнего и нижнего плеч. При этом плечи по своим ВАХ должны быть симметричны. Таким образом, функцию g удобно реализовать в Altium Mixed Sim в форме зависимого источника напряжения, выраженного кусочно-линейной функцией. Значения функции g при этом будут описывать безразмерную величину – некоторый коэффициент, зависящий от напряжения питания. Для идентификации функции g удобно проводить измерение выходного тока при фиксированном напряжении выхода и изменяемом напряжении питания.

Идентификацию функций f и g будем выполнять следующим способом, при этом функцию f, имеющую размерность тока, будем для простоты изложений рассматривать для нижнего плеча (плечи имеют симметричные ВАХ):

- идентифицируем функцию f тока выхода для напряжения питания 5 В в диапазоне от 0 до 2,5 В напряжения выхода с помощью аппроксимации полиномом второй степени;

- вычислим на основе полученного полинома промежуточные значения для напряжений выхода 0,5 и 1,5 В, одинаковых для напряжений питания 10 и 15 В;

- перейдём для функции f от напряжений к проводимости, что упростит построение схемы замещения;

- выполним интерполяцию для известных разных напряжений питания и одинаковых напряжений выхода для того, чтобы экстраполировать проводимость для предельных значений напряжения питания 3 и 18 В;

- вычислим значения функции g как отношение проводимости для напряжений питания 3, 5, 10, 15 и 18 В к значению проводимости для 5 В, что допустимо сделать, так как проводимость имеет прямую пропорциональность с протекающим током.

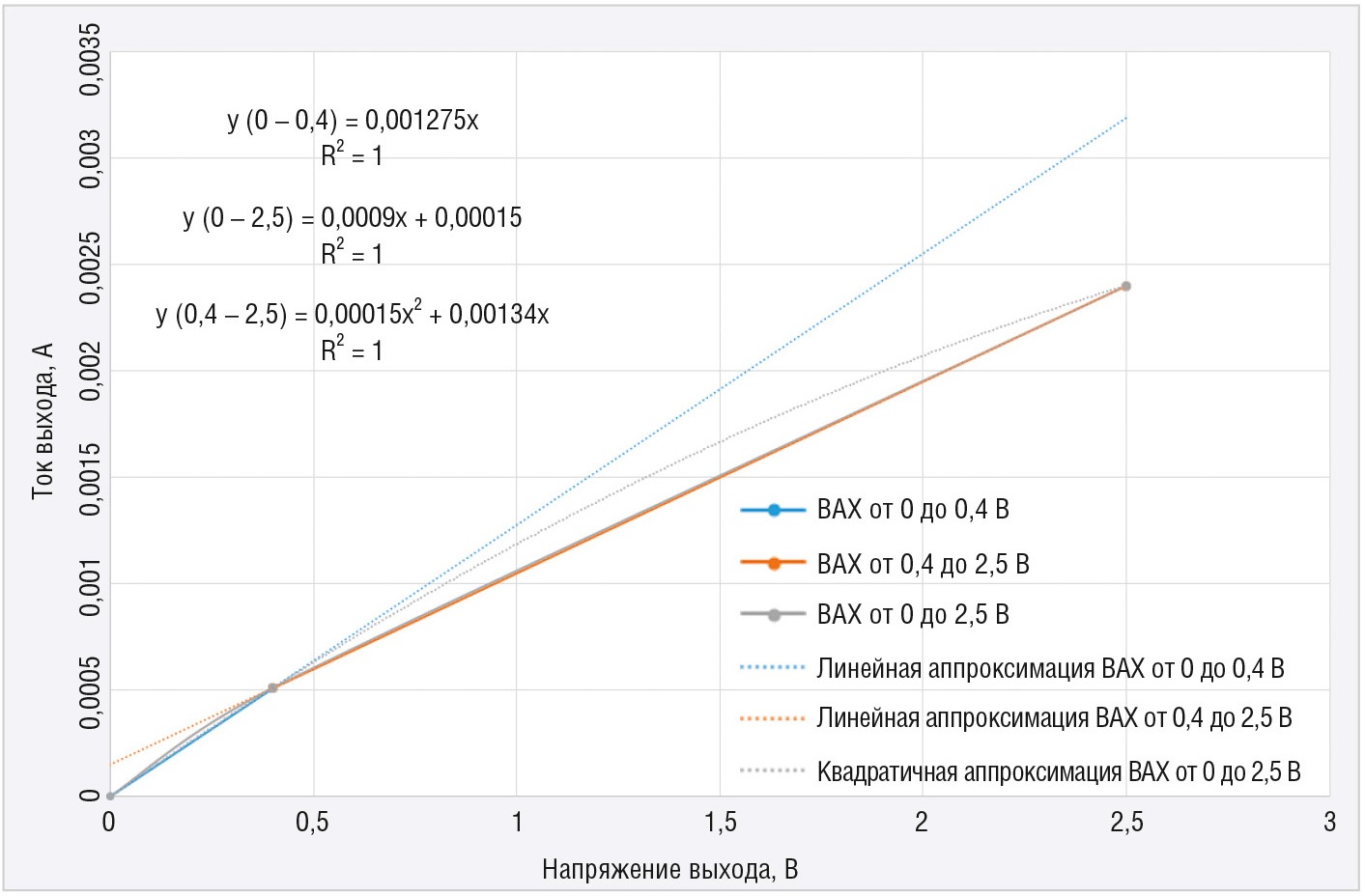

На основании предположения, что ток выхода для напряжения выхода 0 В должен иметь ток 0 А, для напряжения питания 5 В получаем три точки на вольт-амперной характеристике (0 В, 0 А), (0,4 В, 5,1×10–4 А) и (2,5 В, 2,4×10–3 А). На основании этих данных можно выполнить аппроксимацию ВАХ в области напряжения выхода от 0 до 2,5 В (см. рис. 4).

На рисунке 4 видно, что линейная аппроксимация отдельных участков между соседними парами точек ВАХ даёт при экстраполяции к другой граничной точке довольно большой промах, а метод аппроксимации полиномом второй степени позволяет достичь коэффициента корреляции R = 1 и расположить все точки исходных данных на линии тренда. Уравнение полинома второй степени имеет вид: y(x) = –1,5 × 10–4 × x2 + 1,34 × 10–3 × x.

На основании полученного полинома выполним интерполяцию тока выхода для напряжений выхода 0,5 и 1,5 В при напряжении питания 5 В. Для напряжения питания 10 В известен ток выхода при напряжении выхода 0,5 В. Воспользуемся полученным полиномом и рассчитаем значение тока для напряжения выхода 0,5 В при напряжении питания 5 В, получим значение Iвых(Uвых = 0,5 В, Uпит= 5 В) = 6,325 × 10–4 А. Для напряжения питания 15 В известен ток выхода при напряжении выхода 1,5 В, аналогично Iвых (Uвых = 1,5 В, Uпит = 5 В) = 1,673×10–3 А.

Для упрощения построения схемы замещения удобно использовать для формирования тока выхода источник тока, зависящий от собственного напряжения и управляемый некоторой профилирующей функцией, имеющей размерность проводимости Iвых(Uвых, Uпит)=G(Uвых, Uпит) × Uвых, G(Uвых, Uпит) = f(Uвых) × g(Uпит)/Uвых). Таким образом, определим отношение f(Uвых)/Uвых как функцию fпров(Uвых).

Эти сведения позволяют получить зависимость проводимости источника тока, формирующего ток плеча, используя данные одинаковых напряжений выхода и при различных напряжениях питания. Для получения значения проводимости следует разделить ток выхода на напряжение выхода (см. табл. 5).

Для построения функции fпров(Uвых) для напряжения питания 5 В разделим значения тока выхода на напряжение выхода (приведены в таблице 4). В результате получим набор координат точек для представления в кусочно-линейной форме: (0 В, 0 А), (0,4 В, 1,275×10–3 А), (2,5 В, 9,600 × 10–4 А).

Пары точек из таблицы 5 для одинакового напряжения выхода позволяют выполнить линейную аппроксимацию и достаточно точно экстраполировать ближайшие предельные значения проводимости для напряжений питания 3 и 18 В. Для экстраполяции значения проводимости для напряжения питания 3 В используем значения проводимости для напряжений питания 5 и 10 В при напряжении выхода 0,5 В. Значение проводимости для напряжения питания 3 В и напряжения выхода 0,5 В равно 7,31×10–4 См. Аналогично для экстраполяции значения проводимости для напряжения питания 18 В используем значения проводимости для напряжения питания 5 и 15 В при напряжении выхода 1,5 В. Значение проводимости для напряжения питания 18 В и напряжения выхода 1,5 В равно 2,6126×10–3 См.

Так как функция g определяет коэффициент пропорциональности для тока, а значит и проводимости, в зависимости от напряжения питания, то представим значения координат узловых точек как отношение проводимости для определённого напряжения к проводимости для напряжения 5 В. При этом воспользуемся значениями проводимости для соответствующих напряжений выхода 0,5 и 1,5 В при напряжении питания 5 В. В результате для определения функции g получим следующие точки: (3 В, 5,779×10–1), (5 В, 1), (10 В, 2,055), (15 В, 2,033), (18 В, 2,343).

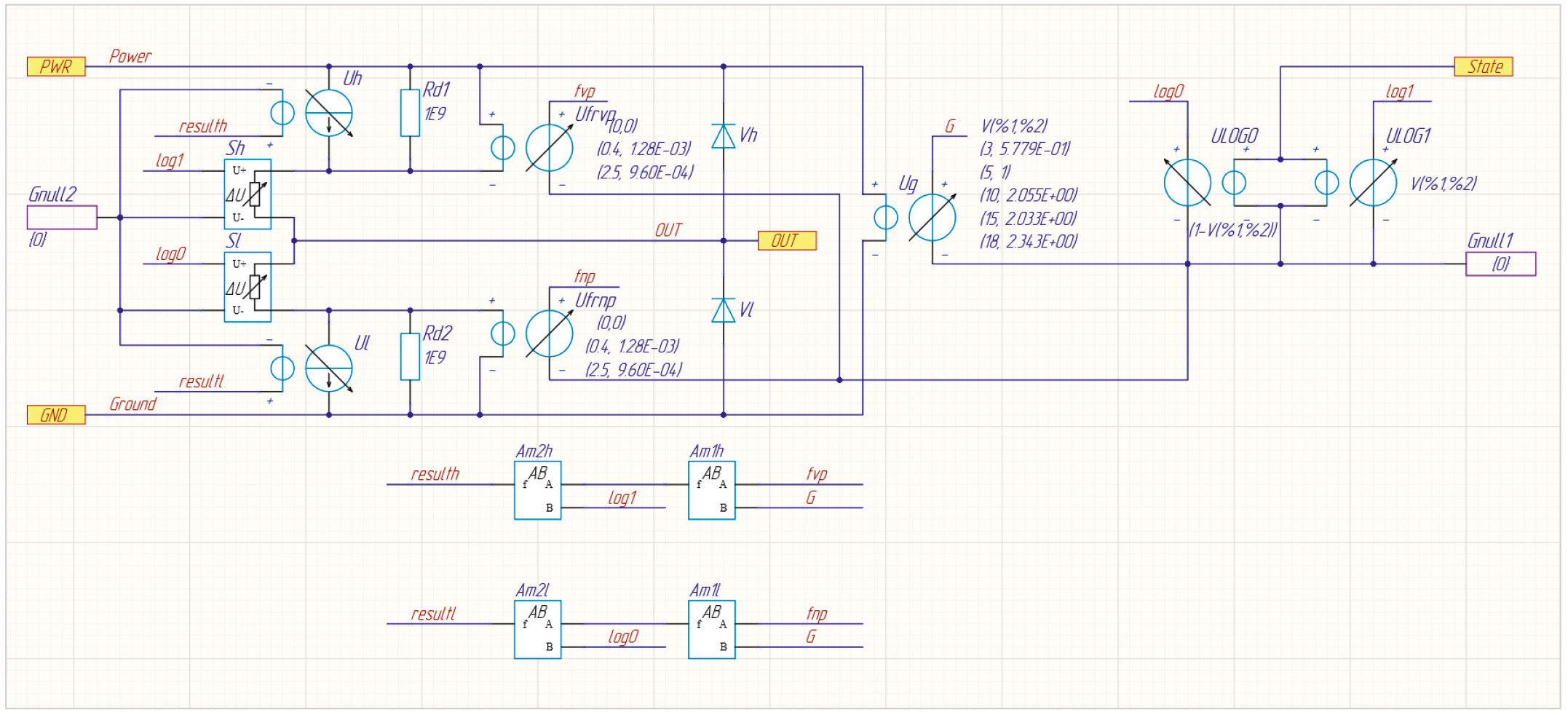

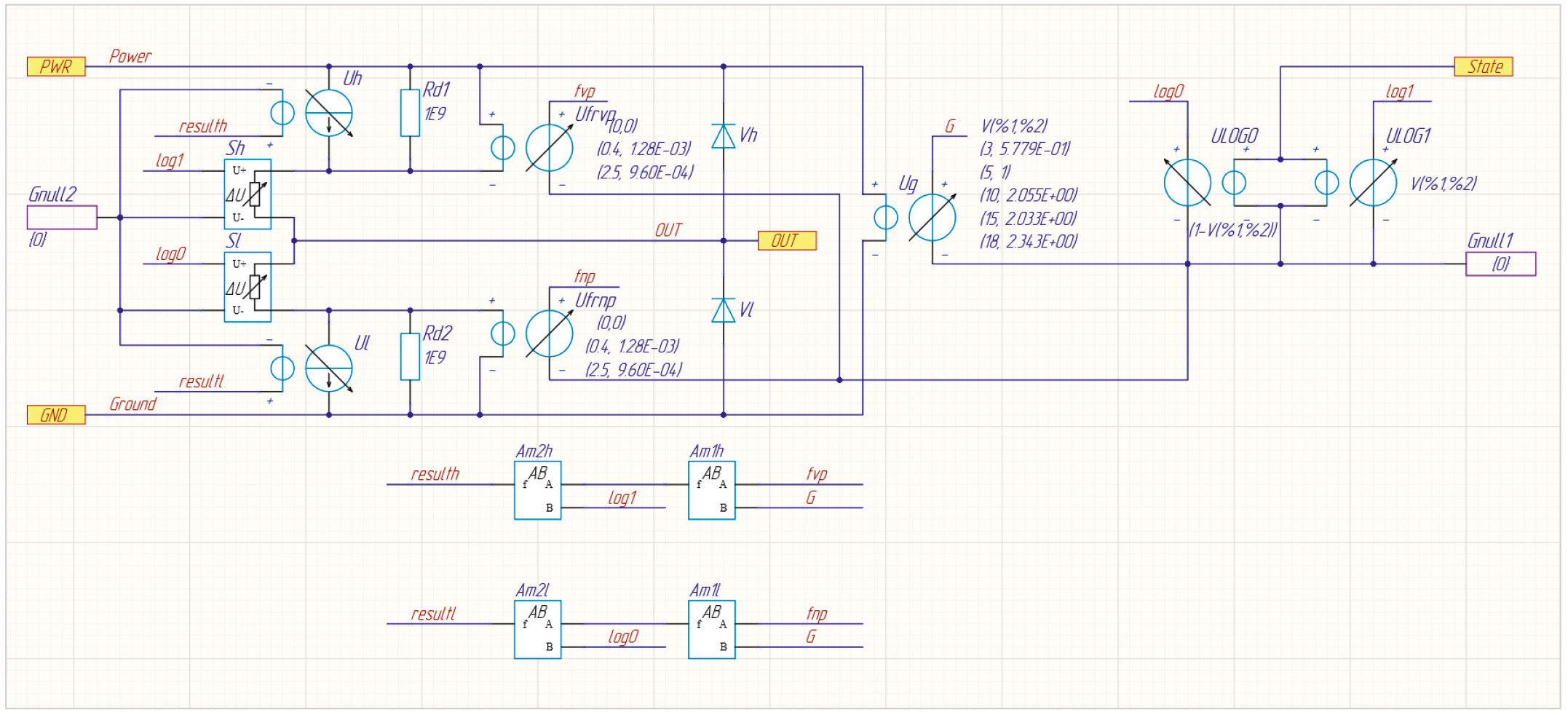

Выразить все изложенные выше построения можно в виде схемы замещения выхода (см. рис. 5).

Элементы Vh и Vl реализуют диодную защиту. Элементы Sh, Uh, Rd1 реализуют верхнее плечо выходного каскада. Элементы Sl, Ul, Rd2 реализуют нижнее плечо выходного каскада. Элементы Rd1 и Rd2 являются фиктивными для обеспечения сходимости расчёта. Причина их добавления в схему замещения заключается в том, что при запертых ключах Sh и Sl и при разомкнутой цепи вывода порта «OUT» формируется условие разрыва электрической цепи для источников тока Uh и Ul, которые могут иметь ненулевое значение. Это приводит к срыву расчёта по причине отсутствия сходимости: при бесконечно большом сопротивлении цепи ненулевой ток вызывает бесконечно большое значение напряжения. Чтобы обеспечить протекание тока, требуется добавить резисторы с заведомо большим, но конечным сопротивлением. Элементы ULOG1 и ULOG0 формируют пороговые напряжения логической «1» и логического «0» соответственно из сигнала состояния, приводимого на порт «State». Элементы Gnull1 и Gnull2 реализуют потенциал базового узла 0. Все математические операции отсчитываются от потенциала базового узла 0. Элементы Ufrvp, Ufrnp реализуют огибающую ВАХ вывода микросхемы для напряжения 5 В – функцию fпров – для верхнего и нижнего плеча соответственно. Элемент Ug реализует коэффициент умножения тока для напряжения питания – функцию g. Элементы Am1h, Am2h, Am1l, Am2l нужны для выполнения математических операций умножения при вычислении функции сопротивления для каждого плеча выхода (формула вычисления приведена выше). Значению порта «State», соответствующего 0 В, соответствует логический «0» на выходе, значению порта «State2», соответствующего 1 В, – логическая «1» на выходе.

Структура узла регулирования потребления тока питания

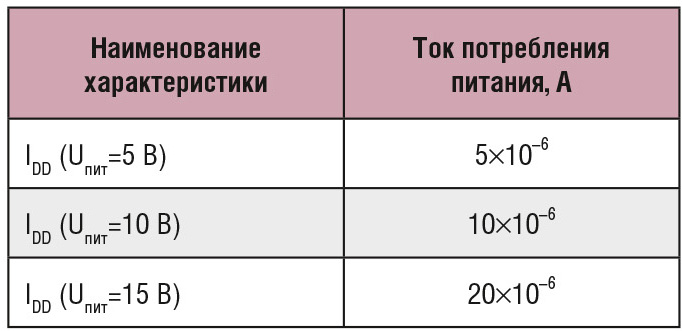

Потребление тока питания в спецификации указано зависящим от напряжения питания.

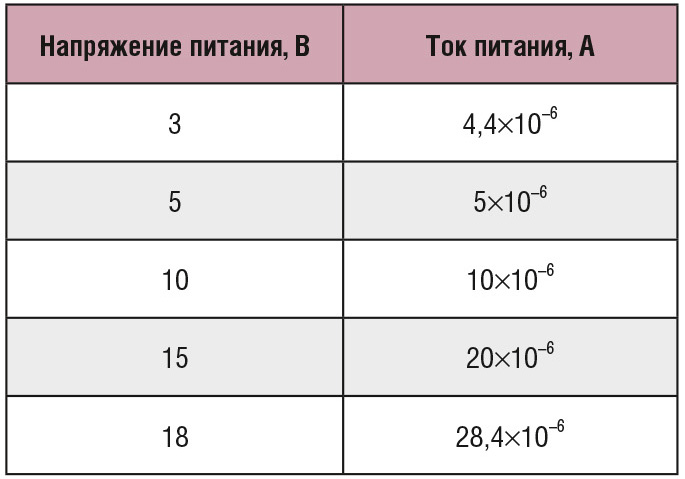

Поскольку в спецификации указано, что типичные значения должны быть использованы только для оценки производительности, то для построения схемы замещения узла потребления тока питания следует использовать предельные максимальные значения. В спецификации приведены сведения для напряжений питания 5, 10 и 15 В (см. табл. 6).

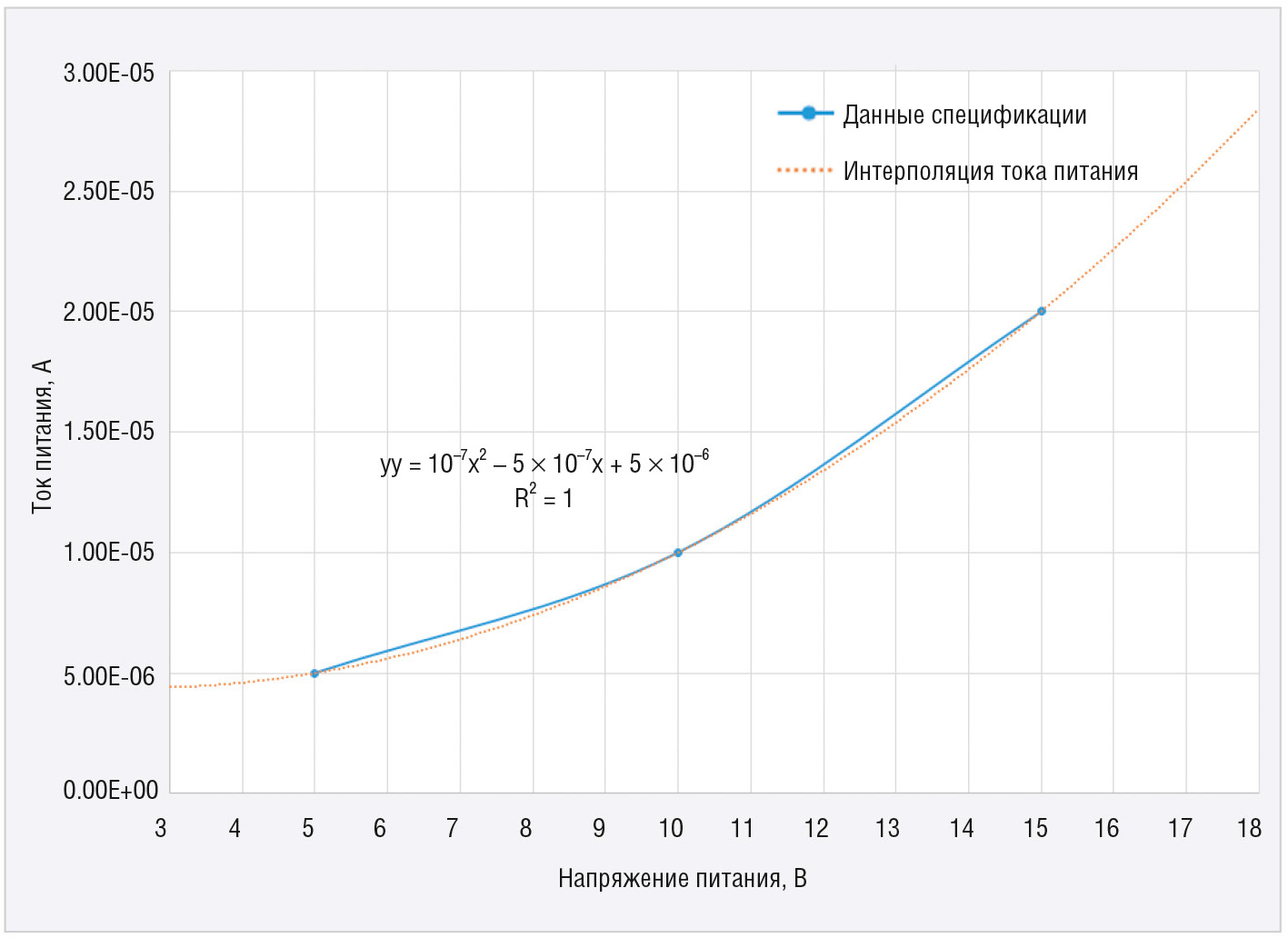

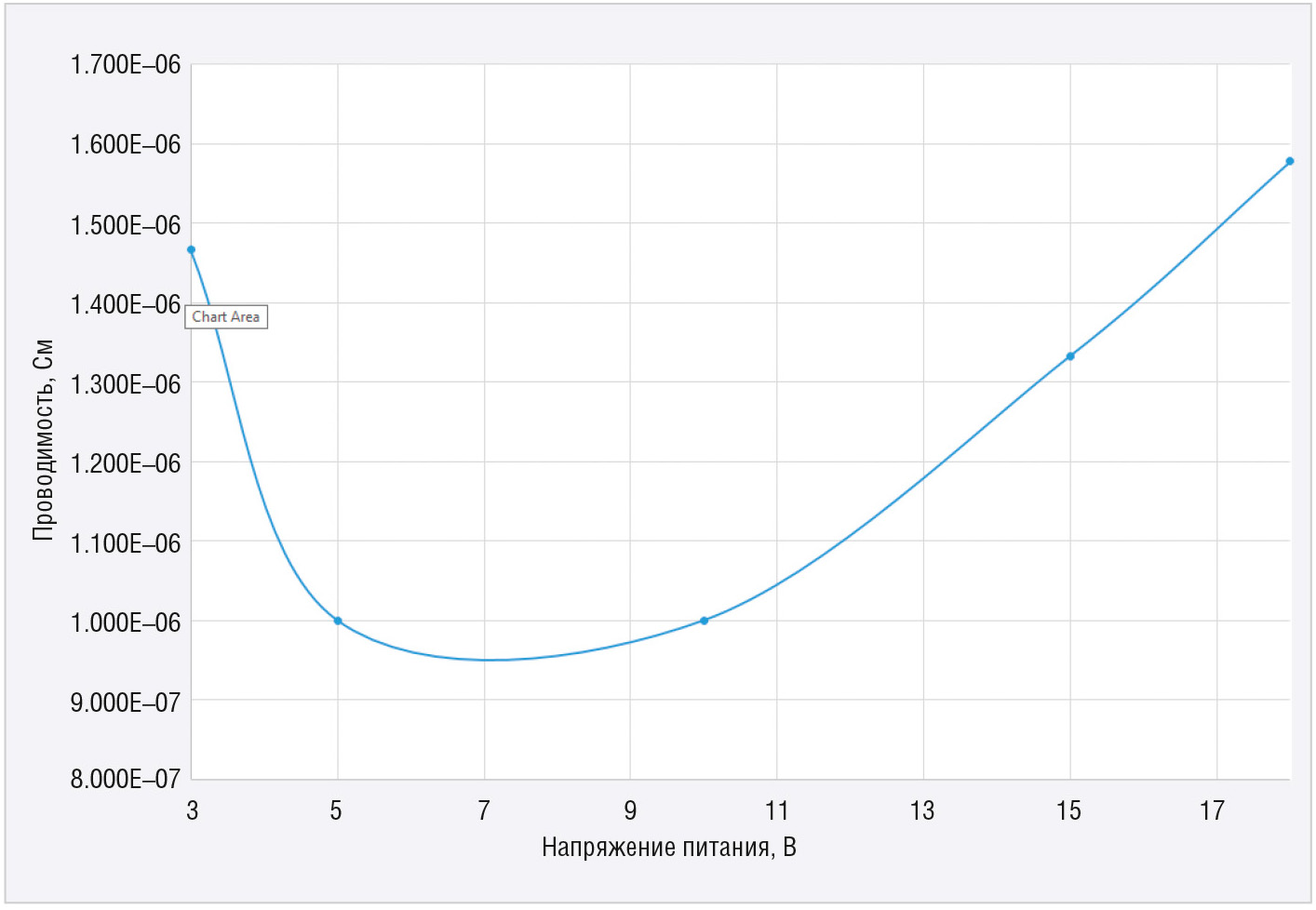

Однако диапазон допустимого напряжения питания составляет от 3 до 18 В. Следовательно, для получения сведений о токе питания для напряжения питания 3 и 18 В данные спецификации требуется экстраполировать. Данные спецификации по току потребления удобно аппроксимировать полиномом второй степени. В результате аппроксимации уравнение полинома имеет вид: Iпит(Uпит) = 10–7 × Uпит × Uпит– 5 × 10–7 × Uпит+5 × 10–6 А, достигнутый коэффициент корреляции R=1 (см. рис. 6).

Аппроксимация позволяет экстраполировать данные для напряжения питания Uпит=3 В и Uпит=18 В. Для Uпит=3 В экстраполированное значение максимального тока питания Iпит=4,4 мкА, для Uпит=18 В экстраполированное значение максимального тока питания Iпит=28,4 мкА. Совокупность данных по току потребления можно свести в таблицу (см. табл. 7).

Сведения из таблицы 7 можно использовать для представления потребления тока питания в табличной форме, поскольку такая форма является более удобной для последующей модификации модели. Построение узла регулирования тока питания удобно выполнить в форме источника тока, линейно зависящего от падения напряжения на своих выводах. При этом токи питания, приведённые в таблице 6, следует привести к напряжению питания, чтобы получить значение сопротивления узла питания для каждого напряжения питания (см. рис. 7).

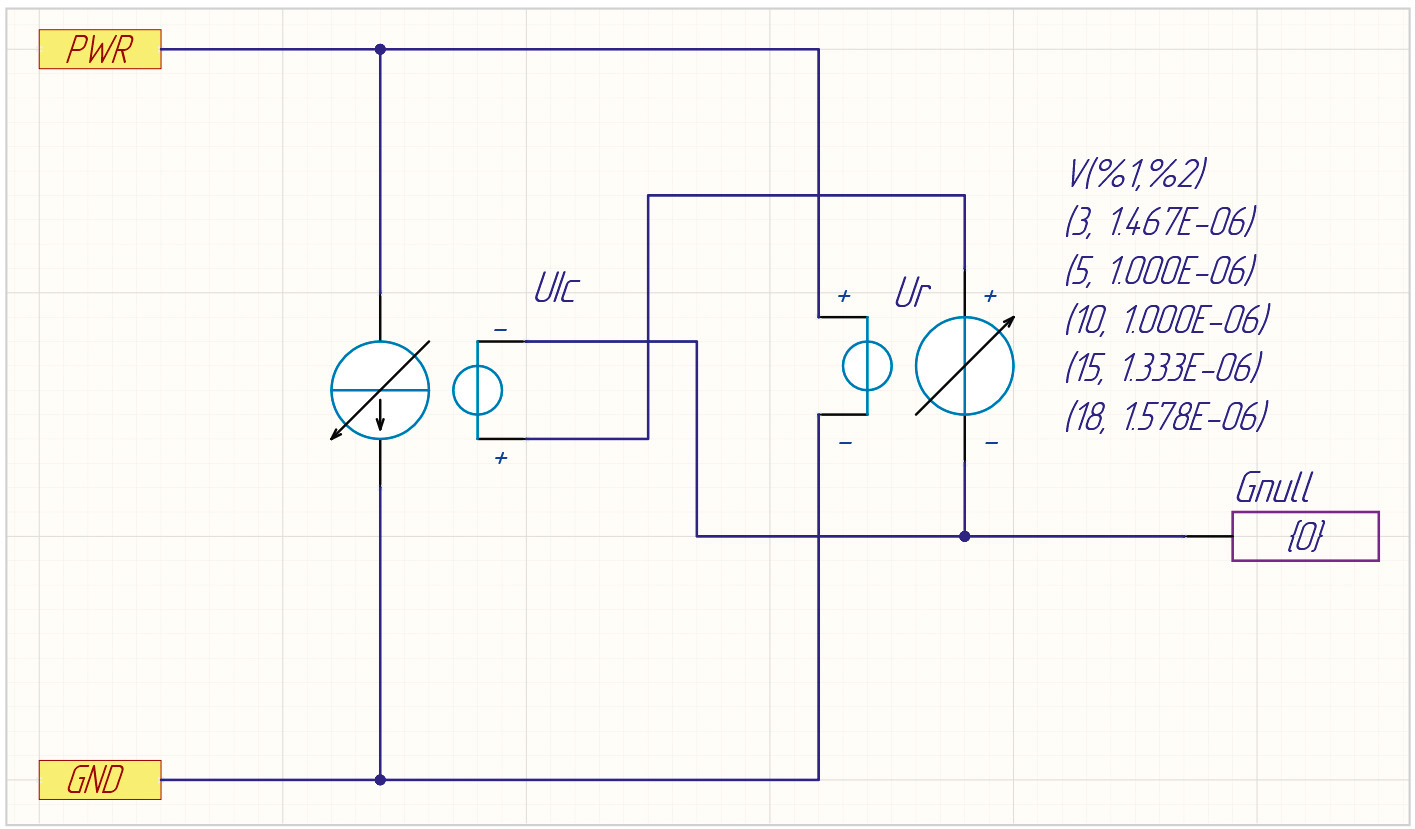

Результат можно представить в виде схемы замещения (см. рис. 8).

Элемент Ur реализует таблицу сопротивления узла питания в зависимости от напряжения питания. Элемент UIc реализует сопротивление микросхемы току питания, зависящее от напряжения питания.

В следующих частях статьи будут рассмотрены параметризация модели, вопросы идентификации и верификации. Отдельное внимание будет уделено разработке компонента интегрированной библиотеки.

Литература

- Расширение функциональных возможностей Altium Designer. URL: https://www.altium.com/ru/documentation/altium-designer/extending-altium-designer.

- Altium Mixed Sim. Руководство пользователя Altium Designer. URL: https://resources.altium.com/sites/default/files/2020-05/Altium Mixed Sim - Руководство пользователя Altium Designer.pdf.

- MC14518B, MC14520B. Dual up counter. Сайт компании On Semiconductor (лист спецификации в формате pdf). URL: https://www.onsemi.com/pub/Collateral/MC14518B-D.PDF.

- Библиотека базовых моделей Sim Lib GOST. URL: https://www.altium-ru.com/sites/default/files/attachments/Sim%20Lib%20GOST.zip.

Если вам понравился материал, кликните значок - вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал - не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!