Цикл проектирования программируемой интегральной схемы представляет собой итерационный процесс. За счёт ограничений, каждый этап проектирования предполагает возвращение на предыдущую стадию для доработки и получения нужных характеристик.

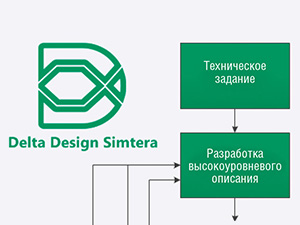

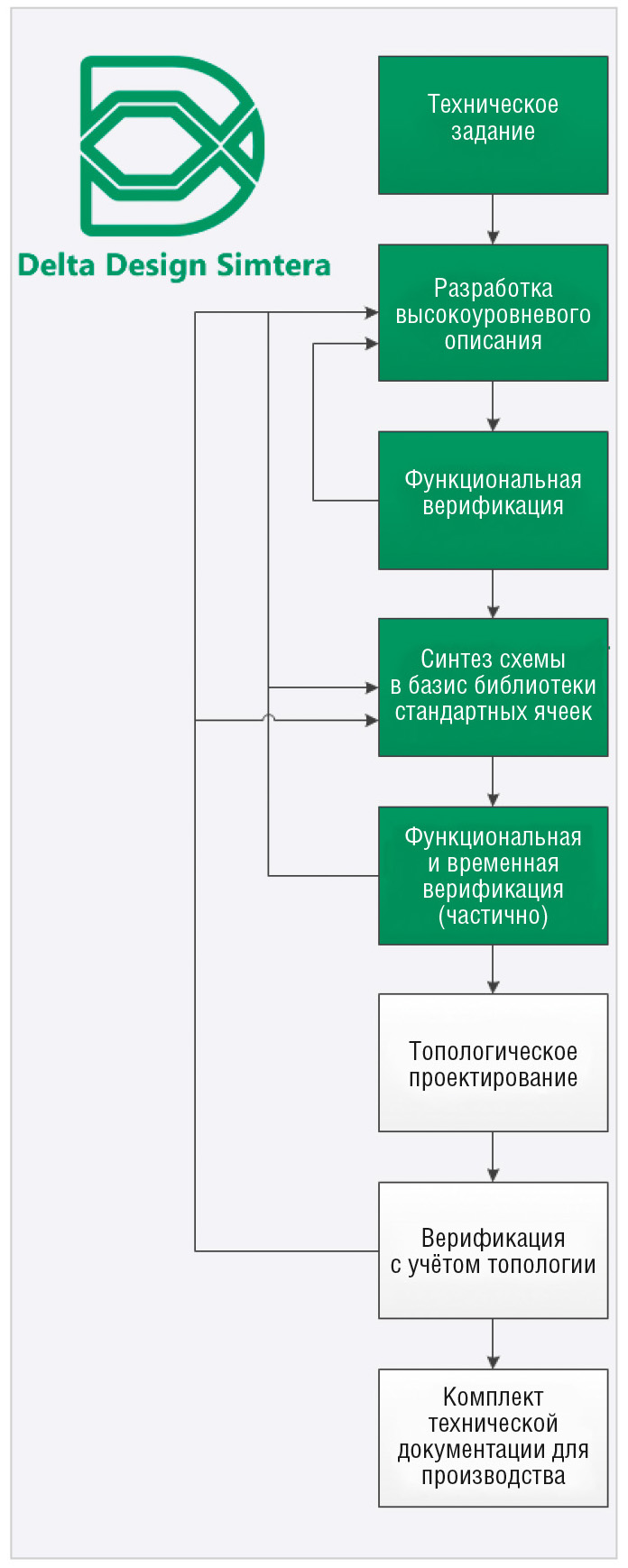

На рисунке 1 представлен маршрут разработки конфигурации ПЛИС с возможностями, реализованными в Delta Design Simtera. Зелёным цветом на рисунке выделены этапы, поддерживаемые Simtera: система обеспечивает разработку, верификацию, синтез и частично функциональную и временну¢ю верификацию проекта. Рассмотрим некоторые нововведения в готовящейся к официальному выпуску новой версии Delta Design Simtera.

Единый интерфейс

В новой версии Delta Design Simtera встроена в САПР проектирования электроники Delta Design и расширяет её функциональность. Теперь, в зависимости от требований разработчиков, Delta Design Simtera может быть предоставлена как в виде самостоятельного программного комплекса, так и в составе с другими программными решениями компании ЭРЕМЕКС. Единый пользовательский интерфейс унифицирует работу со всеми инструментами компании и снижает уровень входа как для новых, так и для опытных пользователей Delta Design.

Схемотехнический редактор и библиотека компонентов

В новой версии Delta Design Simtera предусмотрено ведение проектов в схемотехническом виде. Теперь по желанию разработчика ПЛИС можно выбрать вариант ведения RTL (Register Transfer Level – уровень регистровых передач) описания как в виде HDL-кода, так и в виде схемы. Можно также совмещать оба этих варианта. Вариант совместного ведения проекта типа «схема–код» доступен благодаря тому, что схеме сопоставляется соответствующее HDL-описание.

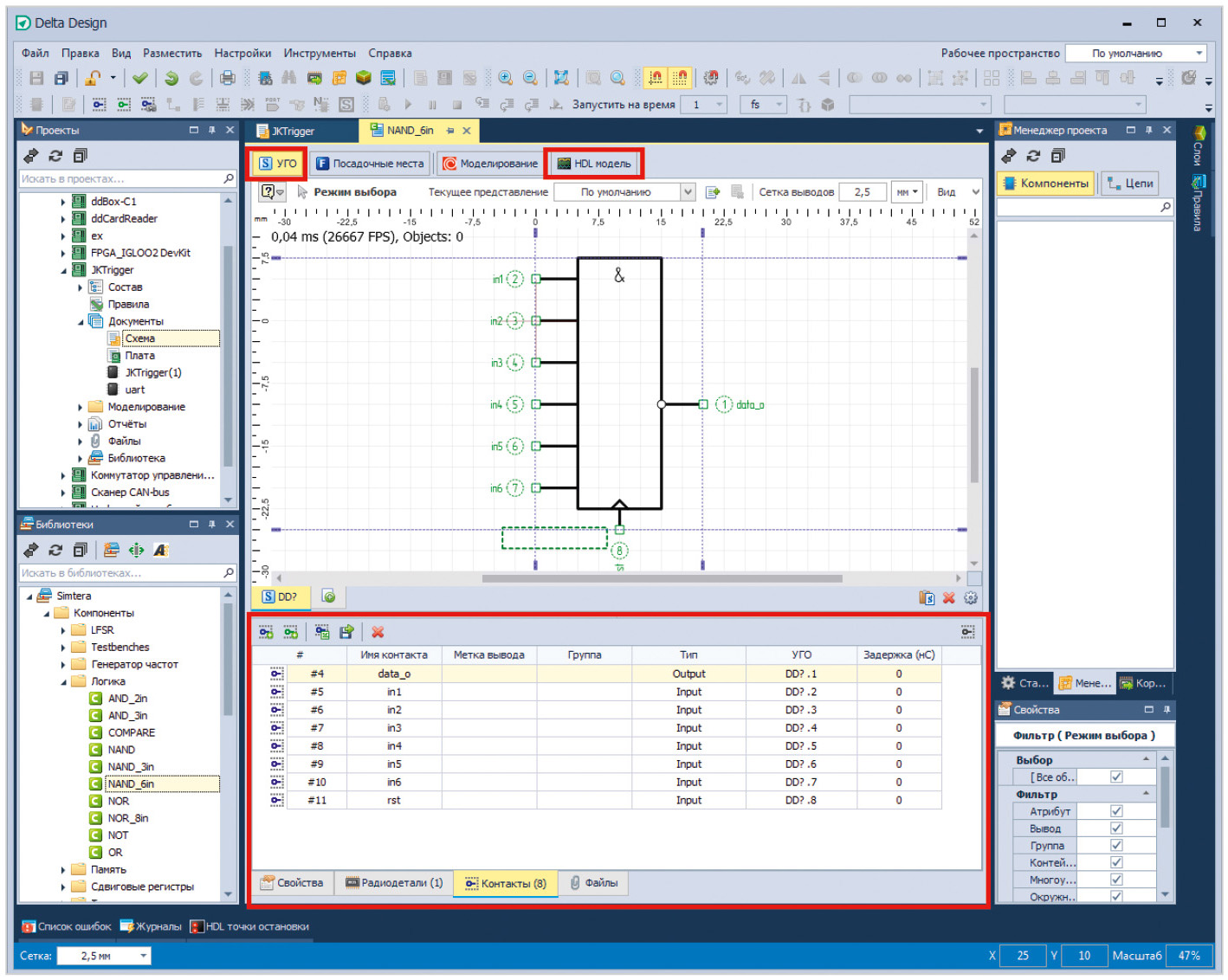

При ведении проекта в виде схемы появляется необходимость в использовании библиотеки. Библиотека позволяет вести единую централизованную базу компонентов. Компонент состоит из множества представлений – УГО (условно-графическое обозначение), посадочное место, SPICE-модель и прочее. В рамках данной статьи рассмотрим только УГО, список контактов и HDL-модель. Именно они задействованы при проектировании и верификации HDL-проектов в схемотехническом виде.

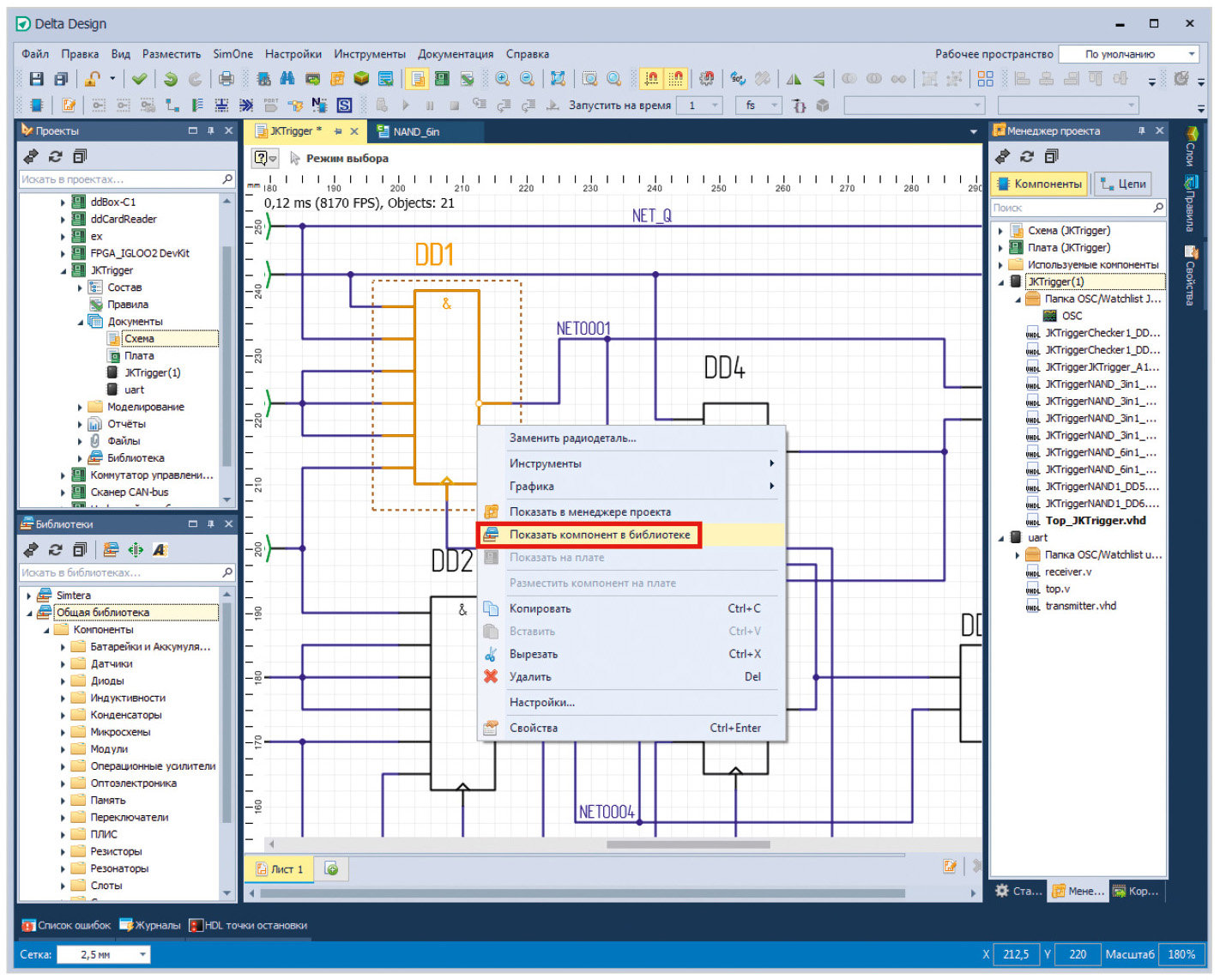

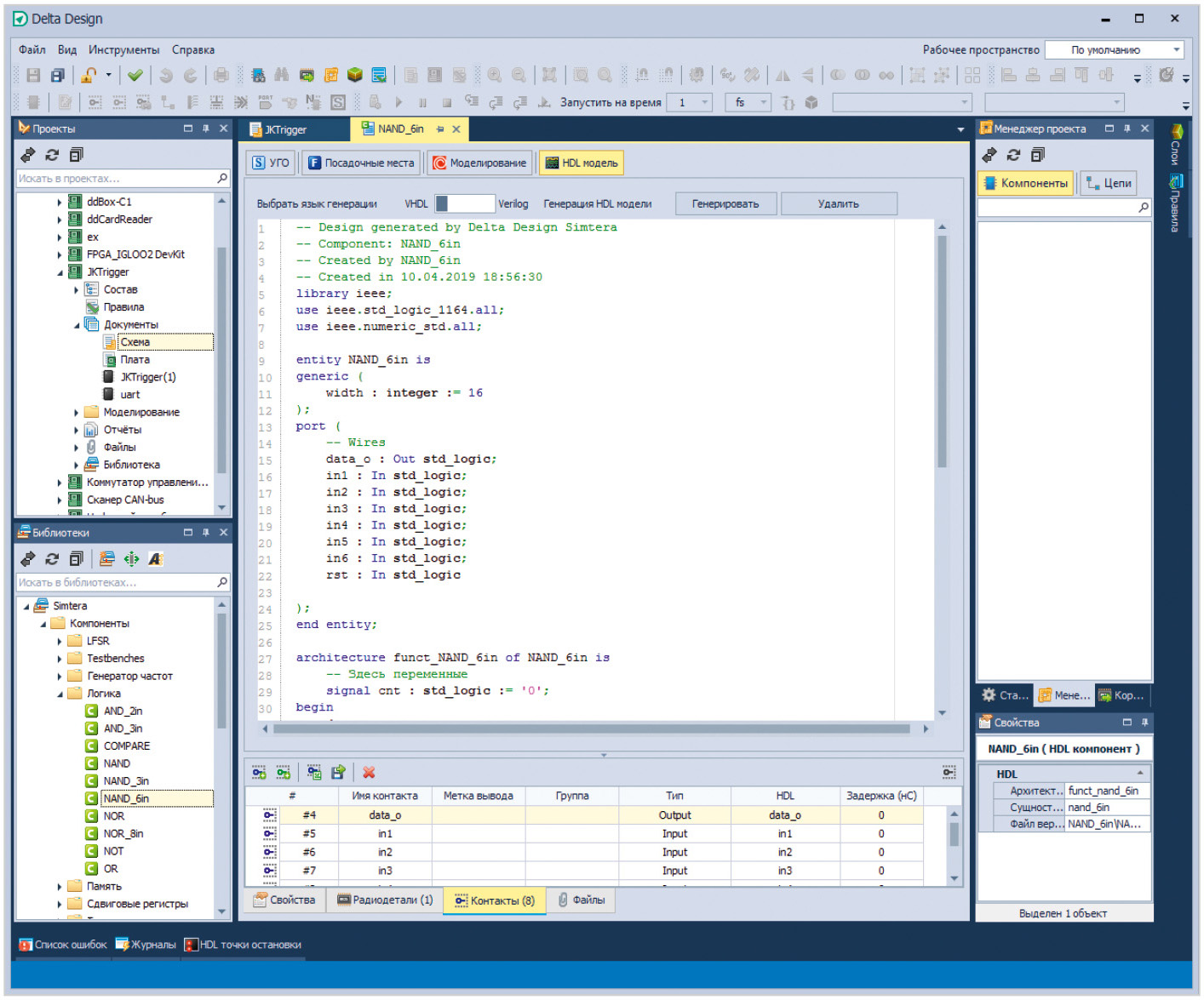

Для просмотра содержимого компонента необходимо обратиться к пункту «Показать компонент в библиотеке» из контекстного меню компонента при его выборе (см. рис. 2). При открытии выбранного элемента библиотеки становится доступно его редактирование. На рисунке 3 показан редактор компонентов.

Каждая вкладка редактора компонентов предполагает работу с определённой моделью компонента. На вкладке УГО соответственно открывается возможность редактирования графического отображения: доступна отрисовка графического представления, расстановка выводов и определение их типов с заданием имён. С помощью выводов осуществляется соединение компонентов в цепи, а графическое представление служит для визуальной идентификации элемента схемы. Также на основе выводов, использующихся в компоненте, возможна генерация шаблона HDL-кода. По выводам и их типам генерируется интерфейс с портами и переменными для HDL-модели компонента. При необходимости HDL-модель компонента может быть расширена разработчиком (см. рис. 4).

Работа с HDL-описанием компонента доступна во вкладке «HDL модель». Здесь так же, как и при работе во вкладке «УГО» доступна панель со списком выводов. Именно по этому списку при нажатии кнопки «Генерировать» (см. рис. 4) произойдёт создание VHDL- и Verilog-моделей. Эти модели содержат описание портов, а функциональность дописывается пользователем самостоятельно. При этом в базовой версии Delta Design Simtera подразумевается поставка библиотеки со стандартными логическими ячейками. Эту библиотеку можно использовать при разработке. Также она будет открыта для изменения и дополнения.

При ведении проекта в схемотехническом виде возможно использование всех средств разработки, заложенных в системе, – это соединение типа «Провод», «Шина», использование многолистовых проектов, повторяющихся блоков и других инструментов. Кроме этого в схемотехническом редакторе во вкладке «Свойства» может быть отображена информация об элементах схемы. Так, при выделении компонента схемы становятся доступными для отображения параметры HDL-модели компонента. Кроме того, параметры компонентов могут быть изменены. Например, в зависимости от использования HDL-языка для описания функциональности компонента, могут быть изменены параметры «generic» VHDL-модели или «parameter» Verilog-модели.

По результатам проектирования схемы можно выгрузить документацию со штампом, перечень используемых компонентов, а также получить статистику по проекту и многое другое.

Верификация и поведенческое моделирование

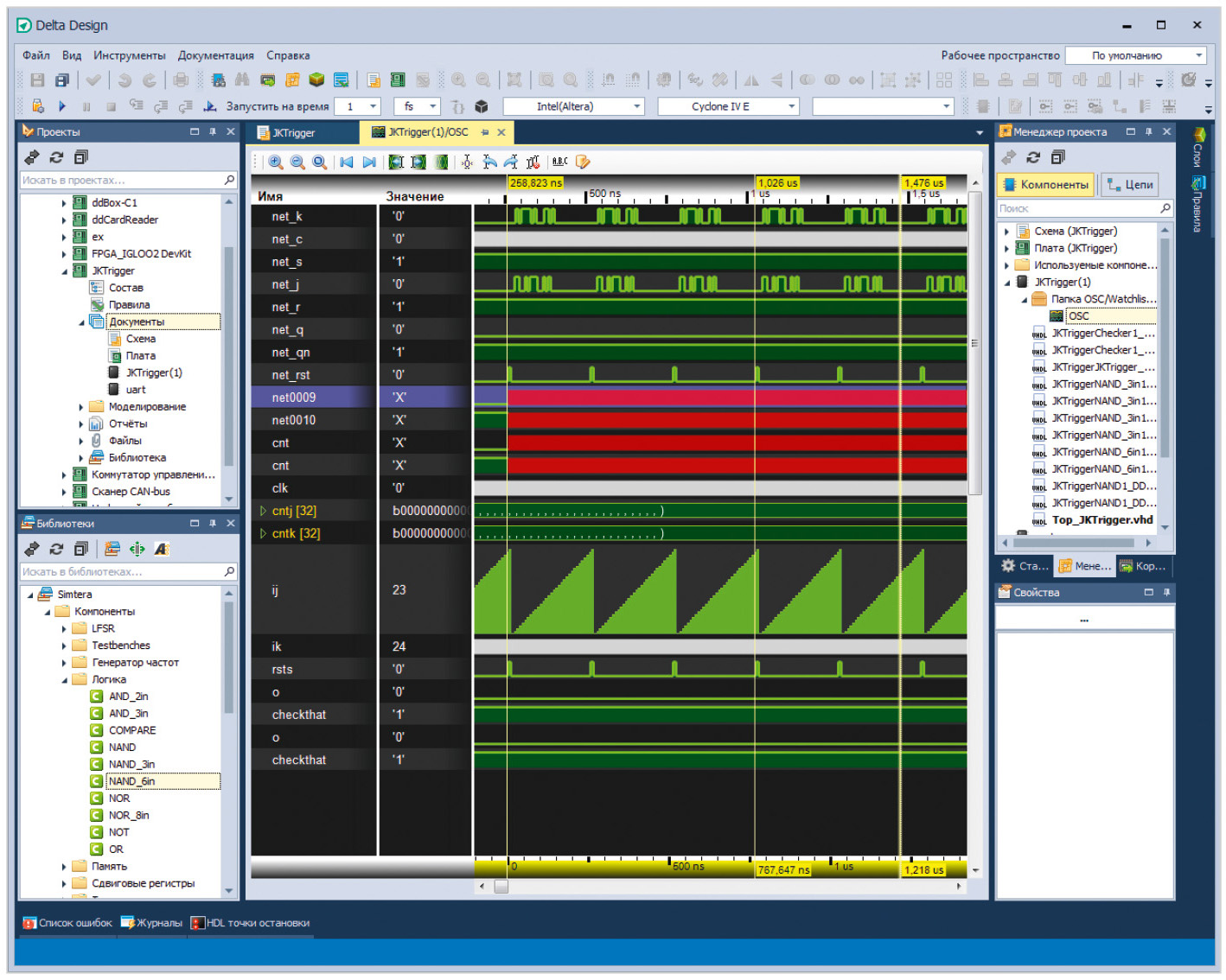

Основной функцией системы Delta Design Simtera является верификация HDL-проектов и их поведенческое моделирование. Кроме этого возможна отладка методом остановки по точкам прерывания в интересующих частях HDL-программы. На рисунке 5 представлена осциллограмма с результатами моделирования разрабатываемой схемы.

В системе, как и в предыдущих версиях, предусмотрены такие инструменты работы с осциллографом, как курсоры, отображение данных в цифровом и аналоговом видах, перемещение курсоров по оси времени и многое другое.

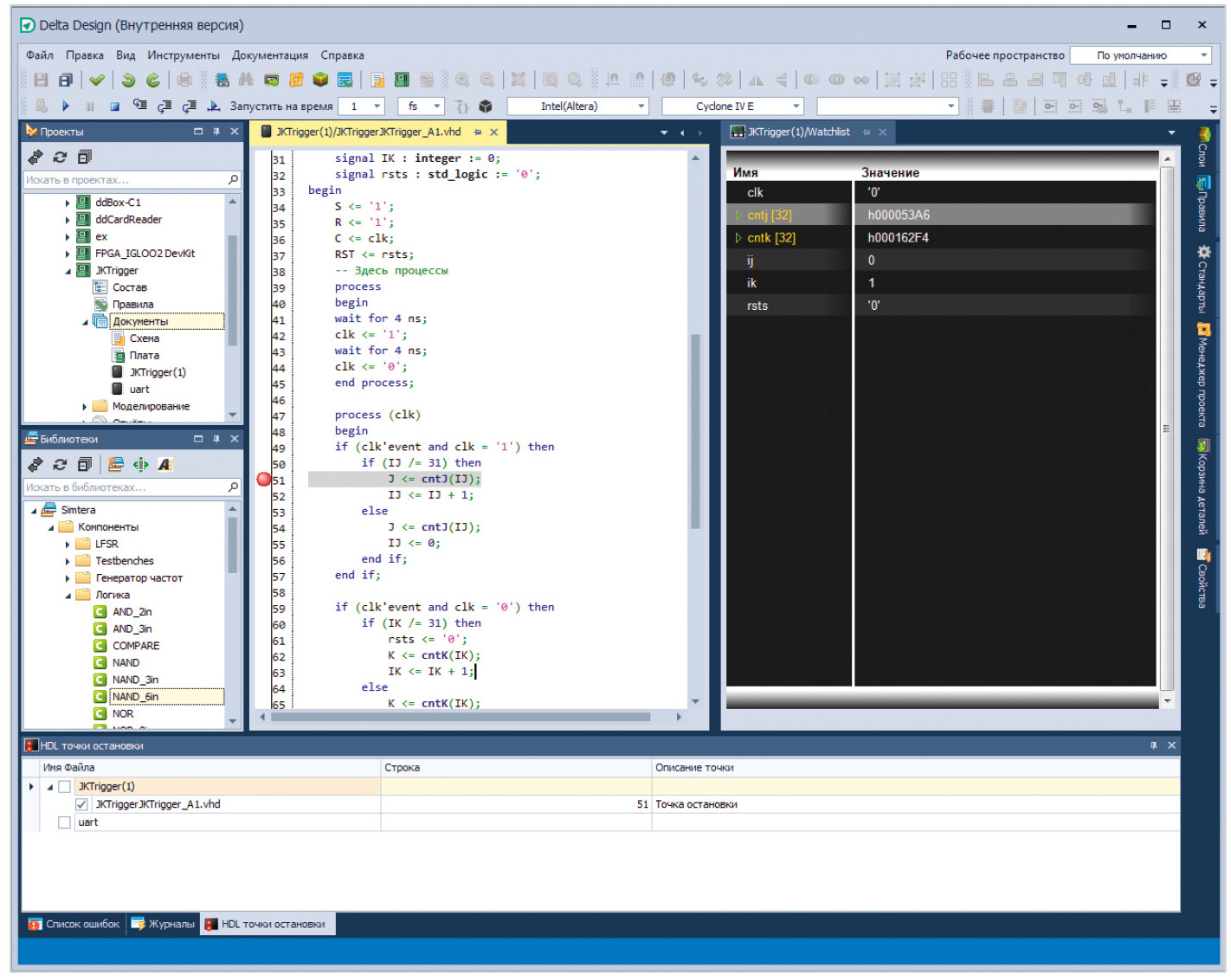

На рисунке 6 показан процесс отладки кода проекта с помощью точки останова (прерывания). При остановке выполнения программы на точке можно отследить состояние HDL-программы – значения переменных, логи, правильность выполнения. Вместе с точкой остановки можно использовать инструмент «Список наблюдения», который также представлен на рисунке 6, в правой части рабочего пространства, для отображения значений переменных при остановке программы.

В системе предусмотрено моделирование assert-ами (проверками утверждений). Для просмотра assert-ов точно так же, как и для просмотра логов, можно использовать панель «Журналы». Именно в неё выводятся сообщения о ходе компиляции, сообщения отладки и другая информация по программе.

Синтез

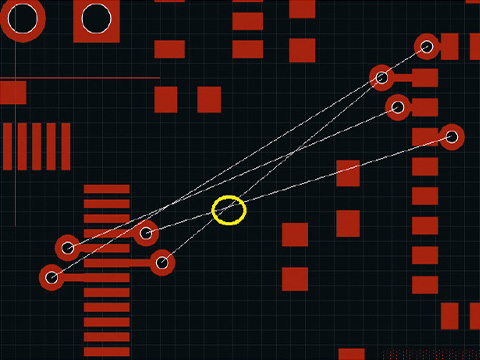

Заключительным этапом работы с системой может быть, как выгрузка файлов HDL-проекта, так и файлов синтеза из HDL в библиотечное представление выбранного устройства для последующего проектирования и получения файлов конфигурации ПЛИС.

В качестве устройств для синтеза можно выбрать Xilinx чипы 7-х серий, Intel – Cyclone IV, Cyclone IV E, Cyclone V, Cyclone 10, Arria 10 GX, MAX 10. Также ведётся работа по поддержке российских ПЛИС от компании МИЛАНДР.

Синтез реализован с помощью встроенного инструмента Yosys [2]. Такая интеграция позволяет отображать Verilog-проекты (на данный момент поддерживается только Verilog) в базис библиотечных ячеек ПЛИС и выгружать результаты синтеза в форматах BLIF, EDIF, VQM и упрощённый RTL Verilog для последующей работы в программных пакетах компаний-производителей (Xilinx, Intel, Lattice и др.).

Для упрощённой работы с Yosys в Delta Design Simtera можно создавать шаблоны, которые будут использоваться при проведении итераций синтеза.

Литература

- Малышев Н. Средства функциональной верификации компании Eremex. Современная электроника. 2018. №7. С. 36–37.

- Строгонов А., Городков П. Программные средства с открытым исходным кодом для проектирования цифровых устройств в базисах БИС и ПЛИС. Компоненты и технологии. 2017. №3. C. 105–114.

Если вам понравился материал, кликните значок — вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал —не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!