Бурное развитие микроэлектронных технологий привело к появлению систем-на-кристалле (SoC – System-on-a-Chip) с впечатляющими характеристиками. Так, графический чип Volta GV100 компании Nvidia содержит порядка 21,1 млрд транзисторов, более 5000 потоковых процессоров, 672 блока матричных вычислений, несколько уровней кэш-памяти, графическую память, более 100 контроллеров памяти и управления системным интерфейсом [1]. Volta GV100 производится по технологическим нормам 12 нм. Возможности современной фотолитографии давно перешагнули длину волны традиционного излучения (193 нм). За счёт специальных технологий (иммерсионная литография, FinFET-транзисторы, специальные методы повышения разрешающей способности и т.п.) удалось выйти на глубоко субмикронные нормы. Так, в компании TSMC сертифицирован технологический процесс с нормами 7 нм, ведутся работы над 5-нм процессом.

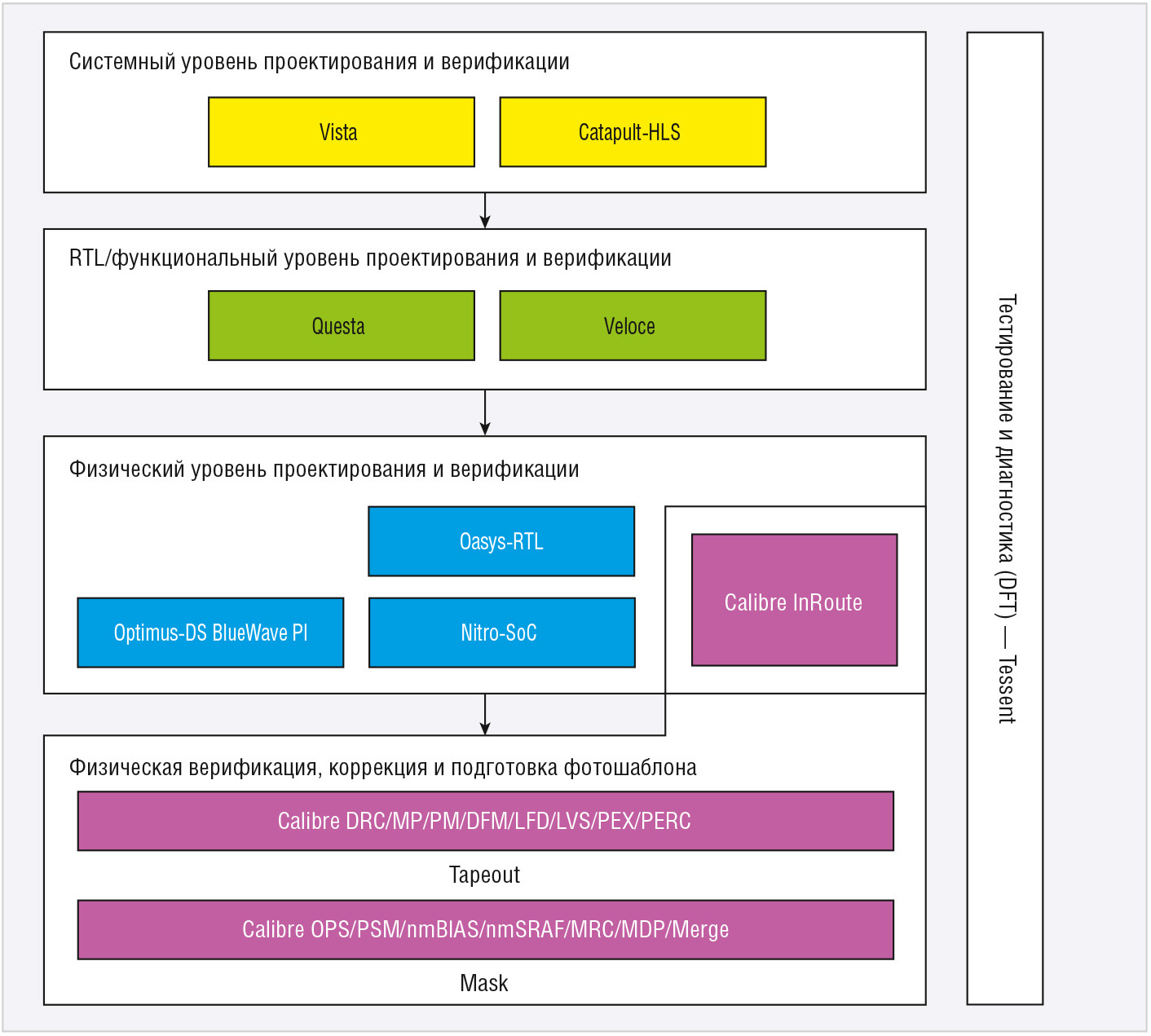

Совершенно очевидно, что такое развитие технологий предъявляет повышенные требования к средствам проектирования и верификации SoC. На сегодняшний день лишь несколько компаний предлагают исчерпывающий комплексный инструментарий для решения данной задачи. Одной из них является компания Mentor Graphics (сейчас входит в состав Siemens PLM Software), которая предлагает интегрированное решение по разработке SoC от системного уровня до верификации топологии кристалла, подготовки фотошаблона и постпроизводственного тестирования. Основные этапы маршрута проектирования Mentor Graphics представлены на рисунке 1.

Рассмотрим отдельные этапы маршрута проектирования более подробно.

Системный уровень проектирования и верификации

Одной из проблем, возникающих при проектировании и верификации сложных SoC, является необходимость так называемого «сдвига влево», присущего в последнее время практически всем маршрутам проектирования [2]. Это означает, что все основные архитектурные решения должны быть отработаны и верифицированы на как можно более раннем этапе проектирования. Даже если разрабатываемая SoC в основном состоит из уже готовых и верифицированных функциональных блоков, возникает проблема верификации шинных протоколов, согласования временны́х характеристик, разрешения конфликтов при обращении к памяти и т.п. Преимущества такого подхода очевидны. Во-первых, анализ и верификация принятых решений на системном уровне осуществляются гораздо быстрее, поскольку моделирование выполняется на языках высокого уровня, как правило SystemC и C++. Во-вторых, такой подход позволяет исключить дорогостоящие итерации проекта, когда ошибка или неоптимальный выбор алгоритма приводят к гораздо бóльшим затратам. Также стоит отметить, что оптимальный выбор решений на системном уровне позволяет получить гораздо более существенную экономию потребляемой мощности, чем если бы это было сделано на RTL или вентильном уровне.

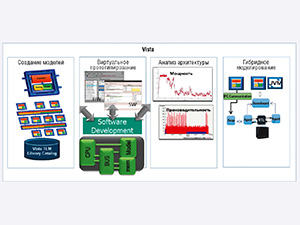

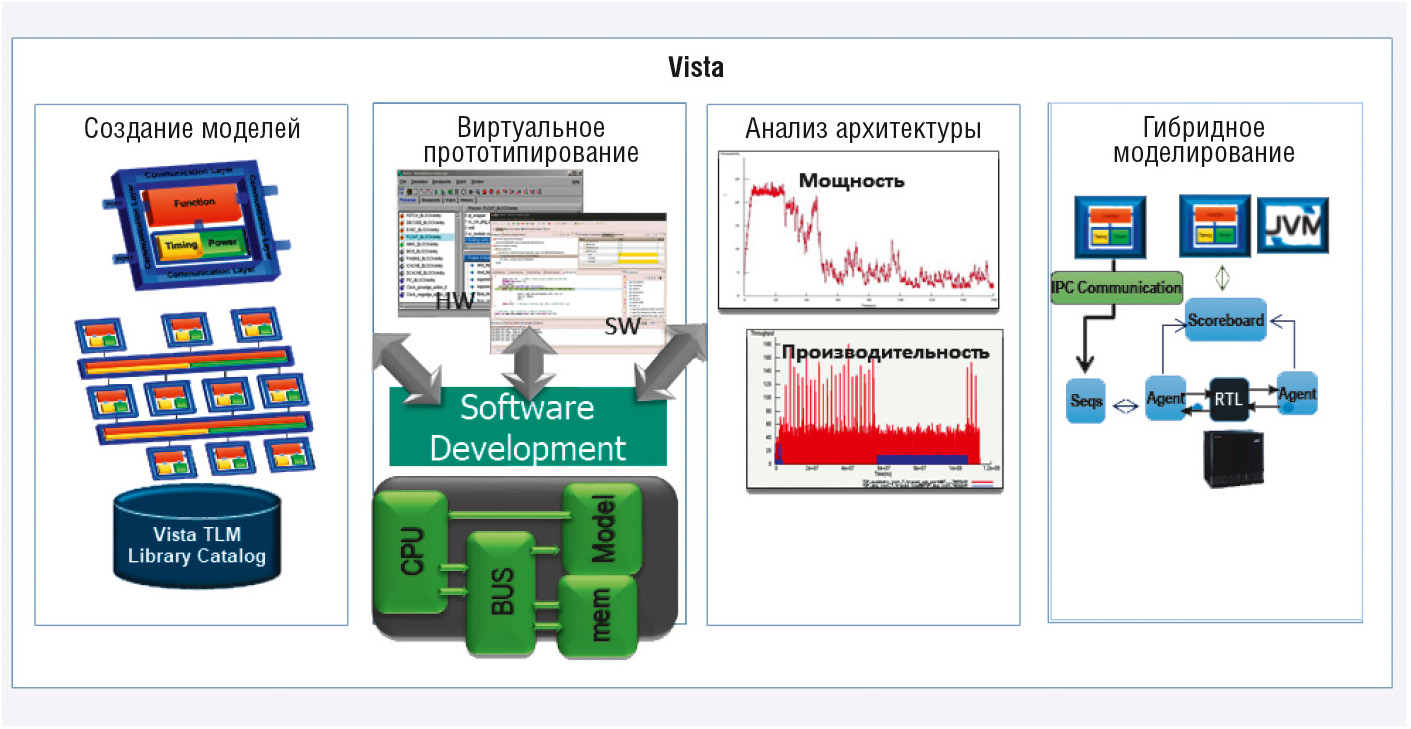

Ядром маршрута проектирования и верификации на системном уровне является платформа Vista. Как показано на рисунке 2, она включает следующие компоненты:

- библиотека моделей TLM (Transaction Level Models) [3] основных процессорных ядер и функциональных блоков – встроенный механизм генерации моделей позволяет дополнять библиотеку моделями пользователя;

- виртуальное прототипирование [4] – используя TLM-модели основных процессорных ядер и других функциональных блоков, разработчик получает возможность параллельной отладки оборудования (hardware) и программного кода, исполняемого на моделях процессоров; трассировка и отладка программного кода выполняются с помощью приложения Sourcery CodeBench;

- анализ архитектуры SoC на системном уровне – позволяет получить максимально возможную производительность системы при минимальных затратах мощности;

- гибридное моделирование – в данном случае обеспечивается возможность параллельного моделирования SoC на системном уровне и более точного моделирования одного или нескольких блоков на RTL-уровне; такой подход сочетает ускорение общего процесса моделирования с более точным RTL-моделированием выбранных блоков.

В целом Vista позволяет пользователю узнать:

- обеспечивает ли выбранная архитектура SoC эффективное выполнение всех функций, заложенных в спецификации заказчика;

- удовлетворяет ли SoC требованиям по быстродействию/производительности и потребляемой мощности;

- возможна ли успешная реализация SoC на выбранном технологическом базисе;

- обеспечивает ли система корректное и эффективное исполнение встроенного программного кода.

Однако отладка и оптимизация архитектуры SoC на системном уровне не решают задачу быстрого получения и верификации RTL-кода [5]. При решении этой задачи возникает множество проблем, например сложность вычислительных алгоритмов, особенно в таких областях, как компьютерное зрение, нейровычисления, широкополосная передача данных в мобильных системах, обработка и компрессия изображений, возрастает настолько, что ручное кодирование RTL приводит к недопустимому опозданию выхода изделия на рынок. Кроме того, как уже отмечалось ранее, исчерпывающая верификация на RTL-уровне по сравнению с системным уровнем требует исключительных затрат на оборудование (серверные кластеры), энергопотребление, лицензии ПО, а также трудозатрат инженеров по верификации. Кроме того, существует проблема переноса верифицированных функциональных RTL-блоков на новую технологию. Приложение Catapult HLS, поставляемое Mentor Graphics, позволяет если не полностью устранить указанные проблемы, то в максимально возможной степени облегчить их решение. Основной задачей Catapult HLS является синтез RTL-кода из исходного C++/SystemC-кода.

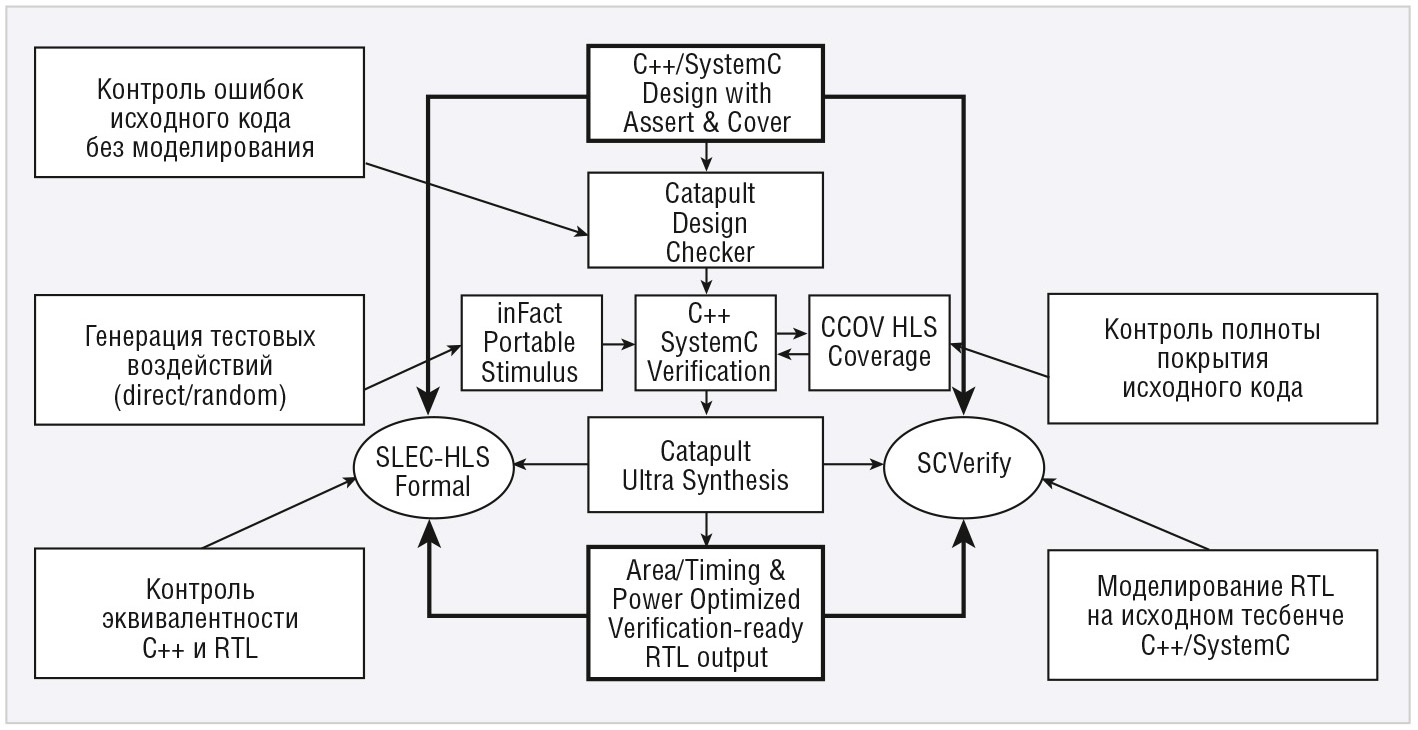

Принципы работы Catapult HLS представлены на рисунке 3.

Приложение решает следующие основные задачи:

- анализ исходного C++/SystemC-кода на предмет обнаружения ошибок и возможных неопределённостей и внесение рекомендаций по их устранению (например, некоторые конструкции кода C++ могут привести к неоднозначности или избыточности при синтезе RTL-кода);

- анализ полноты функционального покрытия при верификации исходного C++/SystemC-кода для обеспечения синтеза RTL-кода с исчерпывающим функциональным покрытием;

- синтез исходного C++/SystemC-кода в VHDL или Verilog-код, полностью подготовленный к дальнейшим операциям функциональной верификации логического синтеза; включение опции PowerPro обеспечивает оптимизацию потребляемой мощности непосредственно в процессе синтеза RTL-кода;

- контроль логической эквивалентности исходного C++/SystemC-кода и синтезируемого RTL-кода (приложение SLEC-HLS Formal);

- генерирование тестбенча для верификации синтезируемого RTL-кода (маршрут SCVerify) на основе исходного тестбенча для C++/SystemC-кода.

RTL/функциональный уровень проектирования и верификации

Несмотря на то что Vista и Catapult HLS обеспечивают на выходе в значительной степени верифицированный RTL-код, прежде чем приступить к физической реализации кристалла SoC, необходимо провести финальную верификацию на функциональном уровне его отдельных блоков, а иногда и всей системы в целом. Например, это происходит в результате «ассемблирования» блоков из собственной пользовательской библиотеки или приобретённых у третьих фирм. Функциональная верификация на RTL-уровне является наиболее затратной с точки зрения требуемых ресурсов оборудования, наличия лицензий и объёмов инженерного труда. Довольно долгое время под функциональной верификацией понимали простое моделирование объектов, описанных на VHDL или Verilog-коде, поэтому основной задачей было максимальное ускорение моделирования за счёт применения более усовершенствованных алгоритмов, более мощных процессорных ядер, распараллеливания моделирования на многоядерных и многопроцессорных системах. В последнее время появились так называемые усовершенствованные методы верификации [6], например формальная верификация на основе assertions, управление полнотой функционального покрытия, автоматическая генерация тестбенчей произвольных (random) тестов с ограничениями и многое другое. Именно такой подход реализован в платформе Questa компании Mentor Graphics, которая является ядром функциональной верификации SoC на RTL-уровне.

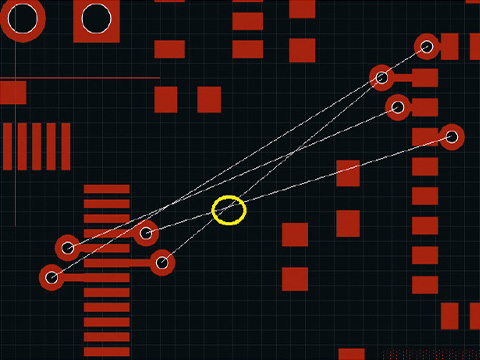

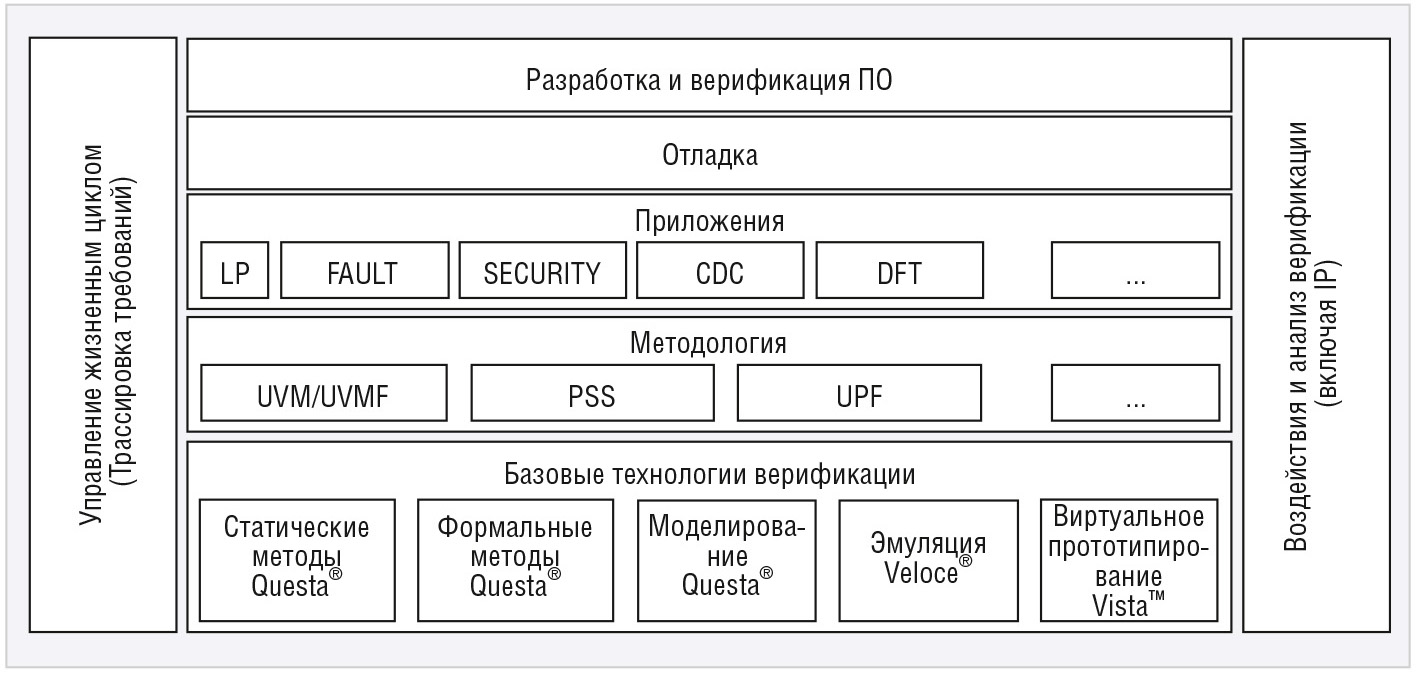

На рисунке 4 представлены основные задачи, которые решаются с помощью платформы функциональной верификации Mentor Graphics.

Ядром Questa является система программного моделирования цифровых проектов, которая поддерживает все основные языки (описание проекта и assertions) и методологии верификации: Verilog, SystemVerilog-2015, VHDL-2008, SystemC-2.3, UPF-3.0, C++, SV-TB, SVA, UVM, UCIS, PSS и другие. Симулятор обладает высокой производительностью и допустимой ёмкостью проектов. Опция Multi-Core позволяет повысить скорость моделирования за счёт распараллеливания задачи на многоядерных системах. Мощные встроенные отладочные возможности и функция просмотра трасс (опция Questa Visualizer) обеспечивают ускорение сходимости верификации, поскольку, как известно, отладка занимает львиную долю времени в этом процессе. Опция Questa InFact позволяет автоматически генерировать тестовые воздействия в соответствии с заданными алгоритмами, причём эти воздействия легко портируются на системный уровень верификации (Vista), в систему аппаратной эмуляции и в систему прототипирования на FPGA. Дополнительным фактором повышения эффективности и сходимости является встроенная библиотека IP-блоков для верификации (Questa Verification IP), которая даёт возможность пользователю сосредоточиться на блоках собственной разработки, заменяя стандартные протоколы и модули памяти встроенными моделями, отработанными на десятках проектов. Дополнительно при моделировании пользователь может учитывать и отрабатывать различные варианты распределения потребляемой мощности, выбирая в конечном счёте оптимальный вариант.

Помимо традиционного моделирования, Questa включает специальные приложения для статической и динамической формальной верификации (Questa Formal) и верификации систем с множественными доменами синхронизации (Questa CDC). Общее управление процессом верификации и сбором статистики по полноте функционального покрытия реализуется опцией Questa Verification Management.

В ряде случаев, например когда необходимо выполнить функциональную верификацию очень большой SoC при ограниченном времени, Mentor Graphics предлагает использовать систему аппаратной эмуляции Veloce [7]. В основании системы лежат специально разработанные «программируемые ASIC» (Crystal SoC). C помощью специального программного обеспечения, используя запатентованную технологию Virtual Wires, верифицируемый RTL-код «компилируется» непосредственно в схему эмулятора, что позволяет ускорить процесс верификации по сравнению с программным моделированием на несколько порядков. Последняя версия системы – Veloce StratoM – поддерживает проекты объёмом до 15 млрд вентилей. Средняя рабочая частота составляет до 2 МГц. Система обладает мощными отладочными средствами, например позволяет хранить все промежуточные состояния цикла эмуляции, останавливаться и стартовать с заранее заданных контрольных точек. Veloce StratoM поддерживает 4 основных режима работы: ускорение моделирования, внутрисхемную эмуляцию, валидацию встроенного программного обеспечения и «виртуальную лабораторию». Уникальными на рынке аппаратных эмуляторов являются такие характеристики, как поддержка многопользовательского режима (до 64 одновременно выполняющихся задач), очень малое время компиляции и загрузки проектов (2 млрд вентилей за 2 мин), малая занимаемая площадь и низкая потребляемая мощность.

Получив исчерпывающе верифицированный RTL-код, можно приступать к физической реализации проекта SoC.

Физический уровень проектирования SoC

Основные этапы физического уровня проектирования и верификации представлены на рисунке 5.

Этот уровень начинается с синтеза RTL-кода [2], который выполняется с помощью приложения OASYS-RTL. В качестве входных данных это приложение использует стандартные форматы:

- RTL-код (Verilog, VHDL, SystemVerilog);

- библиотека стандартных ячеек под конкретный технологический процесс (LIB);

- физическая библиотека (LEF);

- временны́е и топологические ограничения систем синхронизации (SDC);

- ограничения по потребляемой мощности (CPF/UPF);

- входная DFT-информация (CTL);

- ограничения по размещению и планировке кристалла (DEF).

На выходе OASYS-RTL формируются следующие данные:

- вентильный Verilog-нетлист;

- предварительная информация о размещении (DEF);

- данные о цепях сканирования для DFT (Scandef).

Одно из главных отличий OASYS-RTL от традиционных систем синтеза состоит в том, что он уже на начальном этапе использует разбивку RTL-кода на некоторые области с их предварительным «виртуальным» размещением и оценкой получающихся параметров по временны́м соотношениям, потребляемой мощности, размещению, занимаемой площади и возможным конфликтам при трассировке. Это позволяет оптимизировать синтезируемый проект ещё на этапе RTL-кода, в отличие от традиционных систем, которые выполняют основную оптимизацию уже на уровне вентилей. Одновременно оцениваются и параметры всего проекта в целом и, в случае необходимости, выполняется переразмещение с повторным синтезом отдельных блоков. Это позволяет получить более высокое качество результатов уже после первого прохода. Для оптимизации мощности используются такие технологии, как библиотеки компонентов с несколькими порогами срабатывания, стробирование синхросигналов, системы с несколькими переключаемыми шинами питания и др.

Другими уникальными возможностями OASYS-RTL являются анализ и валидация готовых RTL-функциональных блоков в процессе синтеза. Анализируется корректность временны́х параметров и возможных конфликтов при размещении и трассировке.

OASYS-RTL имеет единый пользовательский интерфейс, обеспечивающий одновременный просмотр логического и физического представлений проекта с возможностью кросс-ссылок между ними и локализацией потенциальных нарушений временны́х параметров и конфликтов при трассировке.

Приложение поддерживает синтез проектов ёмкостью более 100 млн вентилей и обеспечивает скорость синтеза, на порядок превышающую возможности традиционных синтезаторов.

За счёт использования стандартного представления входных и выходных данных OASYS-RTL может применяться как в маршруте проектирования Mentor Graphics, так и в маршрутах других поставщиков средств проектирования.

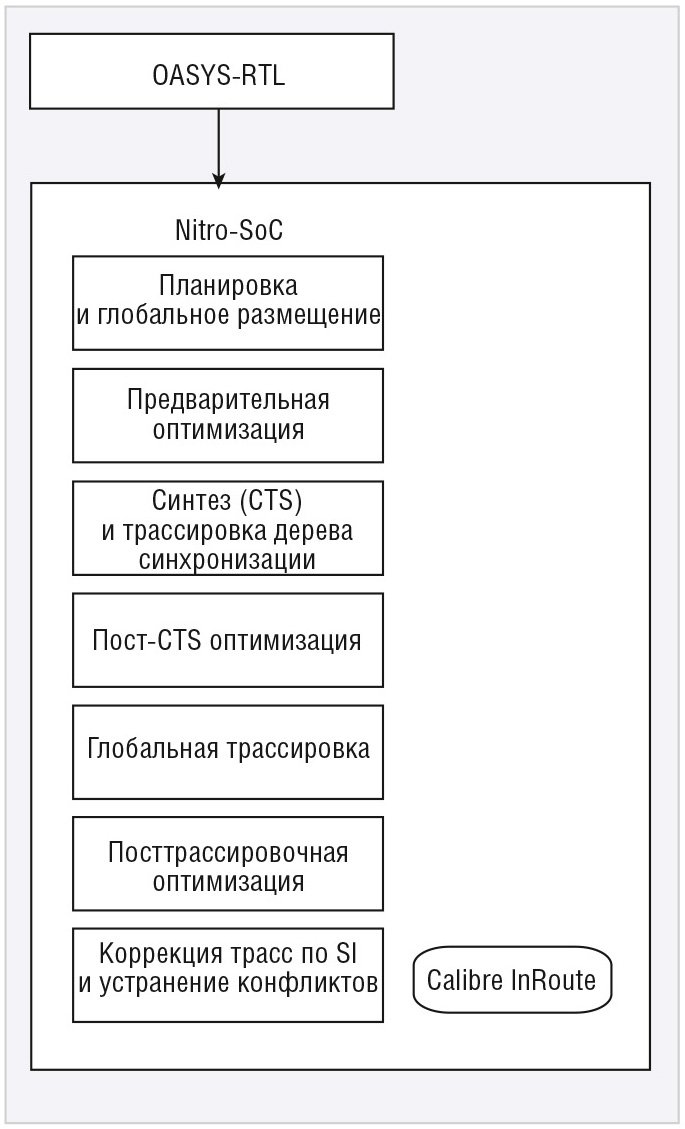

Получив оптимизированный нетлист на выходе OASYS-RTL, можно приступать к размещению и трассировке всего кристалла [2]. Эта задача решается с помощью приложения Nitro-SoC. Формат MXDB (Mentor eXchange Data Base) обеспечивает оптимальную передачу данных с этапа синтеза на этап размещения и трассировки. Основные этапы физического проектирования, выполняемые в приложении Nitro-SoC:

- планировка кристалла и глобальное размещение;

- предварительная оптимизация;

- синтез (CTS) и трассировка дерева синхронизации;

- пост-CTS оптимизация;

- трассировка кристалла;

- посттрассировочная оптимизация;

- коррекция трасс по результатам анализа целостности сигналов и устранения конфликтов трассируемости;

- удвоение межслойных переходов (Calibre InRoute);

- генерация полигонов для технологии двойного фотошаблона (DP – Double Patterning) (Calibre InRoute);

- оптимизация по результатам анализа DFM-правил (Calibre InRoute).

На этапе планировки и размещения возможны различные алгоритмы работы, включая «плоский», иерархический и «псевдоплоский». Поддерживается размещение как для канальной, так и для бесканальной трассировки. На этапе распределения пинов учитываются выполнение временны́х ограничений и возможные конфликты при трассировке. С помощью специальной технологии размещения макросов (AMP – Automatic Macro Placement) достигается очень высокое качество результатов размещения.

В процессе синтеза и трассировки дерева синхросигнала применяется специальный алгоритм MCMM (Multi-Corner Multi-Mode), который позволяет не только устранить перекосы в распространении синхросигнала, вызванные технологическими вариациями, например вариациями резистивности трасс, но и оптимизировать проект с точки зрения экономии дополнительных буферов в цепях синхронизации, оптимизации площади кристалла и потребляемой мощности.

Nitro-SoC имеет встроенный механизм оптимизации потребляемой мощности, который используется на всех этапах физического проектирования. Это позволяет сократить потребление мощности, в том числе дополнительно до 10% на финальном этапе оптимизации, что достигается за счёт применения специальных алгоритмов оптимизации мощности в процессе трассировки, которые обеспечивают баланс между динамически потребляемой мощностью, мощностью утечки, быстродействием и площадью кристалла.

Nitro-SoC поддерживает самые современные технологии мультишаблона и FinFET [8] и сертифицирован для технологических норм 7 нм в компании TSMC. Ультракомпактная база данных приложения обеспечивает работу с проектами ёмкостью более 100 млн вентилей при минимальных затратах оперативной памяти рабочей станции. За счёт встроенных механизмов параллелизма в каждом исполнительном блоке достигается очень высокая скорость получения финального варианта топологии: до 1,5 млн вентилей за 24 часа. Приложение поддерживает распараллеливание на многоядерных и многопроцессорных системах с использованием алгоритмов multi-threading и fine-grained multiprocessing.

В традиционных маршрутах проектирования после получения топологии кристалла в формате GDSII или OASIS следуют этап верификации топологии с точки зрения выполнения DRC- и DFM-правил, при необходимости – экстракция паразитных параметров для более точного моделирования отдельных блоков на уровне Spice или FastSpice, дополнительные процедуры по коррекции топологии (OPC, PSM, sRAF и др.) для технологических норм 65 нм и ниже. Последний этап, как правило, выполняется изготовителем кристалла.

Компания Mentor Graphics предложила уникальную технологию DRC/DFM-верификации топологии непосредственно в процессе трассировки в Nitro-SoC с помощью приложения Calibre InRoute. Для этого была разработана архитектура OpenRouter, которая запускает все DRC- и DFM-процедуры Calibre непосредственно изнутри цикла трассировки. Любое нарушение правил, обнаруженное Calibre InRoute, автоматически исправляется программой трассировки Nitro-SoC в инкрементном режиме. Такой подход позволяет существенно сократить количество итераций физической верификации, по существу получив финальный верифицированный вариант топологии (sign-off tapeout) на первом проходе. Другим преимуществом является отсутствие передачи больших массивов данных, т.к. ядра программы трассировки и программы верификации работают на одном хосте. Как уже было сказано, Calibre InRoute, помимо классического контроля DRC, включает все процедуры DFM (Calibre LFD, Calibre CMP Analyzer, Calibre YieldAnalyzer, Calibre YieldEnhacer), а также такие технологии повышения качества DFM, как заполнение металлом (metal fill), технологии двойного и мультишаблона (double-pattern, multi-pattern) и метод сравнения с библиотекой шаблонов (pattern matching). Все файлы правил (rule decks) DRC и DFM, которые использует Calibre InRoute, сертифицированы ведущими фабриками для технологических узлов вплоть до 7 нм. Приложение, функционально аналогичное Calibre InRoute, которое предлагается для использования в сторонних маршрутах проектирования, получило название Calibre RealTime.

На завершающем этапе физического проектирования часто возникает необходимость выполнения ещё двух важных операций – статического временнóго анализа и анализа целостности по цепям питания. Для решения первой задачи предназначено приложение Optimus DS. Оно позволяет работать как с плоскими, так и с иерархическими проектами, поддерживает алгоритм MCMM (Multi-Corner Multi-Mode), включает анализ целостности сигналов, учитывает вариативность параметров ячеек, а также за счёт распараллеливания на многоядерных системах поддерживает проекты до 100 млн вентилей в иерархическом режиме. Скорость обработки на плоских проектах, включая анализ целостности сигналов, составляет около 30 млн вентилей за 6 ч.

Для решения задачи анализа целостности питания предназначено приложение BlueWave PI. Оно анализирует искажения по цепям питания в переходных режимах и при одновременном переключении сигналов в соседних цепях, обнаруживает недопустимые падения напряжения (электромиграция) в цепях питания в статическом и динамическом режимах, анализирует наведённые шумы и многое другое. BlueWave PI поддерживает распределённые вычисления, что позволяет анализировать проекты большого объёма за короткое время. Как Optimus DS, так и BlueWave PI полностью интегрированы с приложением физического проектирования Nitro-SoC.

Физическая верификация, коррекция и подготовка фотошаблона

Если по каким-либо причинам физическая верификация не может быть проведена на этапе трассировки, например если Calibre используется в стороннем маршруте проектирования и пользователь не имеет лицензии Calibre RealTime или если всё-таки требуется финальная, более исчерпывающая верификация перед этапом tape- out, можно использовать платформу Calibre в режиме stand-alone.

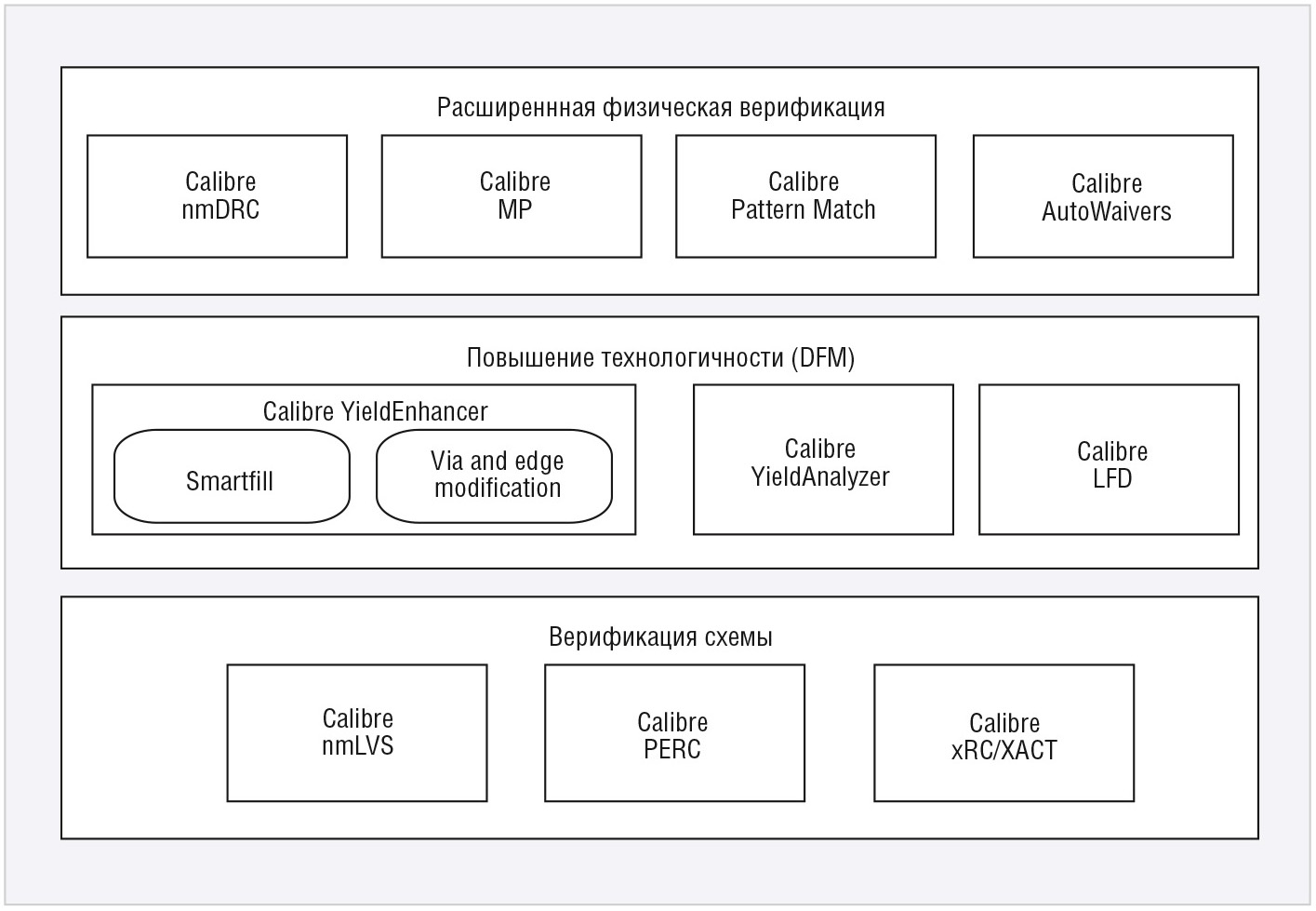

Общая структура приложений Calibre, которые используются до этапа sign-off tapeout, приведена на рисунке 6.

На этом этапе можно выделить 3 функциональные группы приложений:

- Группа физической верификации.

- Группа DFM (Design for Manufacturing).

- Группа верификации схемы.

Как правило, верификация начинается с прогона Calibre nmDRC и проверки выполнения правил из rule deck для технологии, по которой будет изготовлен кристалл. На сегодняшний день Calibre nmDRC является де-факто стандартом в области физической верификации. Файлы правил Calibre nmDRC появляются и отрабатываются на фабриках задолго до того, как та или иная технология запускается в серийное производство. Таким образом, пользователи всегда имеют надёжные и проверенные данные, которые позволяют со 100%-й точностью верифицировать проекты. Программа отличается исключительно высокой скоростью обработки и экономным использованием ресурсов памяти. Распараллеливание обработки в режиме hyperscaling на многоядерных или многопроцессорных системах обеспечивает существенное повышение производительности.

Для технологических норм 20 нм и ниже оказывается недостаточно контроля геометрических правил проектирования. В последнее время появились технологии двойного фотошаблона и мультифотошаблона, которые позволяют повысить разрешающую способность рисунка топологии за счёт применения нескольких фотошаблонов. Эта задача решается с помощью опции Calibre Multi-Patterning, которая обеспечивает автоматическое или полуавтоматическое разбиение рисунка слоя на две или несколько частей для получения нескольких фотошаблонов.

Другая технология, широко применяемая для продвинутых технологических норм, получила название Pattern Matching. В состав платформы Calibre входит опция с соответствующим названием Calibre Pattern Matching. Суть технологии сводится к тому, что вместо обработки геометрических правил, описанных на языке SVRF, опция использует заранее сохранённую библиотеку верифицированных шаблонов рисунков топологии для сравнения с топологией текущего проекта и установки маркера «Верифицирован» в случае совпадения. Это позволяет существенно ускорить и повысить точность процесса верификации.

Последняя опция из данной группы – Calibre AutoWaiver – обеспечивает «маскировку» и исключение из процесса верификации областей топологии, которые по какой-либо причине не нуждаются в данной процедуре. Например, это могут быть заранее верифицированные для данной технологии физические IP-блоки или области, хотя и генерирующие формальные ошибки верификации, но не влияющие на процесс изготовления и выхода годных.

К группе DFM относятся опции Calibre YieldEnhancer, Calibre YieldAnalyzer и Calibre LFD.

Первая из них реализует ряд операций, которые направлены на повышение «технологичности», а следовательно, повышения выхода годных. К таким операциям относятся заполнение металлом разреженных областей топологии (smart fill), удвоение межслойных переходов (double via) и другие. Опция Calibre YieldAnalyzer обеспечивает обратную связь от этапа анализа выхода годных после изготовления кристалла к процессу физической верификации. Она анализирует критические области отказов и формирует дополнительные правила (на языках SVRF и TVF), которые затем включаются в библиотеки DRC/DFM-правил с целью повышения выхода годных в последующих выпусках данного кристалла или других проектах, выполняющихся по той же технологии. Опция Calibre LFD моделирует влияние вариаций параметров процесса фотолитографии на возникновение дефектов в топологии кристалла и формирует корректирующие правила, сводящие данное влияние к минимуму.

Последняя группа относится к верификации параметров схемы. Модуль Calibre nmLVS решает классическую задачу извлечения параметров полупроводниковых приборов и их связности из топологического представления проекта и сравнения их с исходным нетлистом схемы проекта. Вторая важная задача – передача паразитных параметров, полученных с помощью приложения экстракции Calibre xRC/XACT, в исходный нетлист для последующего более точного Spice-моделирования в приложениях Eldo или AFS. Как и все остальные приложения платформы Calibre, Calibre nmLVS поддерживает как плоские, так и иерархические проекты и распараллеливание на много-

ядерных системах. Оно интегрировано с приложением Calibre PERC, что позволяет учитывать при моделировании не только геометрические, но и электрические параметры.

Одной из важнейших задач, которая стоит перед разработчиками SoC, является экстракция паразитных параметров непосредственно из топологии кристалла. Как уже было сказано, это позволяет проводить более точное моделирование формы и задержек сигнала с учётом реального размещения и топологии ячеек. Эта задача решается с помощью приложения Calibre xRC. Экстракция выполняется на основе заранее верифицированных фабриками правил, описанных на языке SVRF. Такие файлы правил имеются практически для всех существующих фабрик и технологических процессов. Как и все приложения платформы Calibre, Calibre xRC поддерживает работу с иерархическими проектами и распределённую обработку на многоядерных системах, а также практически все модели экстракции (R, C, RCC, RCLM и др.). Выходные форматы (Hspice, Eldo, Spectre, Calibreview, DSPF, SPEF и др.) позволяют создавать нетлист, используя все известные системы моделирования. Эти же данные могут быть применены для статического временнóго анализа, анализа целостности сигналов, анализа цепей питания на предмет недопустимых падений напряжения.

Для технологий с нормами менее 20 нм, включая FinFET, компания Mentor Graphics разработала новое приложение Calibre xACT [9]. Оно включает новое счётное 3D-ядро, которое позволяет учитывать все эффекты продвинутых технологий, например эффект уменьшения размеров «плавника» и стока, которые приводят к увеличению сопротивления между истоком и стоком и снижению быстродействия транзистора.

Последнее приложение из группы верификации схем относится к новому поколению инструментов для повышения надёжности работы SoC. Приложение Calibre PERC является мощным средством анализа различных электрических эффектов, которые могут привести к деградации работы и полному отказу схемы. К ним относятся эффект электрического «перенапряжения» в цепях питания, эффект электростатического разряда, пересечение сигнальными проводниками областей с различными номиналами питания и многое другое. Calibre PERC поддерживает как стандартные файлы правил на языке SVRF, так и «кастомизированные» пользователем правила на Tcl-TVF. Приложение полностью интегрировано с другими решениями платформы Calibre.

Последняя группа приложений Calibre относится к этапу post-tapeout и предназначена для выполнения ряда процедур, ориентированных на повышение разрешающей способности в процессе фотолитографии, а также на подготовку данных для изготовления фотошаблона. Поскольку эти процедуры обычно выполняются специалистами фабрики, мы не будем подробно на них останавливаться в данной статье. Ограничимся кратким перечислением основных технологий повышения разрешающей способности:

- оптическая коррекция – OPC (Optical Proximity Correction);

- фазовый сдвиг за счёт изменения толщины фотошаблона – PSM (Phase-Shift Mask);

- добавление рассеивающих линий – OPCsbar (OPC Scattering Bars);

- добавление специальных структур для повышения разрешения – SRAF (Sub-Resolution Assist Feature).

Заключение

В данной статье был рассмотрен маршрут проектирования SoC от компании Mentor Graphics. Основное внимание было уделено цифровым системам. Следует отметить, что все приложения, рассмотренные в статье, могут с одинаковым успехом работать как в интегрированном маршруте Mentor Graphics, так и в качестве точечных решений в маршрутах других компаний.

Отдельные статьи мы планируем посвятить маршруту проектирования аналоговых и смешанных SoC, а также средствам тестирования и диагностики SoC (DFT).

Литература

- NVIDIA Launches Revolutionary Volta GPU Platform, Fueling Next Era of AI and High Performance Computing. NVIDIA Press Release, May 10, 2017.

- Немудров В., Мартин Г. Системы-на-криcталле. Проектирование и развитие. – М.: Техносфера, 2004.

- Weller Y., Rachamim R. Realizing ESL with Scalable Transaction Level Models. White Paper. Mentor Graphics, 2010.

- Matalon S. Vista Virtual Prototyping. White Paper. Mentor Graphics, 2015.

- Селиванов И. Маршруты высокоуровневого синтеза. Современная электроника. 2007. № 6.

- Аряшев С.И., Рогаткин Б.Ю., Барских М.Е. Современные методы функциональной верификации RTL-моделей блоков СБИС микропроцессора. МЭС-2014. Россия, Москва, октябрь 2014.

- Salvidge C., Chobisa V. The Veloce Strato Platform: Unique Core Components Create High Value Advantages. White Paper. Mentor Graphics, 2017.

- Narayanan A., Winefeld B. FinFET and Multi-Patterning Aware Place and Route Implementation. White Paper. Mentor Graphics, 2016.

- Chow K., Relayea C., Clee C., Abouzeid K. The Calibre XACT Platform: Next-Generation Parasitic Extraction for 16 nm and Beyond. White Paper. Mentor Graphics, 2015.

Если вам понравился материал, кликните значок — вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал —не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!