Введение

Сегодня, как показывают исследования и практика, важнейшее значение при разработке функциональности программируемой логической интегральной схемы (ПЛИС) приобретает верификация проекта [1], причём сложность этого процесса растёт из года в год. Согласно исследованиям, проведённым компанией Mentor Graphics, в среднем верификация занимает 48% от всего времени, потраченного на создание проекта.

Если говорить о растущей сложности верификации, то стоит учесть, что в среднем 59% проектов на ПЛИС содержат встраиваемый процессор, а 32% проектов задействуют 2 и более процессоров [2] – это также усложняет разработку и отладку. В итоге более половины разработок, а именно 65%, сдаются позже намеченных сроков. Причиной этого является наличие в них «непростых» ошибок.

Инструменты Delta Design Simtera

Учитывая то, что инженерный состав, занимающийся функциональной верификацией, тратит 21 и 43% времени на создание тестбенчей и отладку соответственно [3], в Delta Design Simtera основное внимание уделено таким областям деятельности разработчика ПЛИС, как ведение кода, нахождение и устранение ошибок и моделирование.

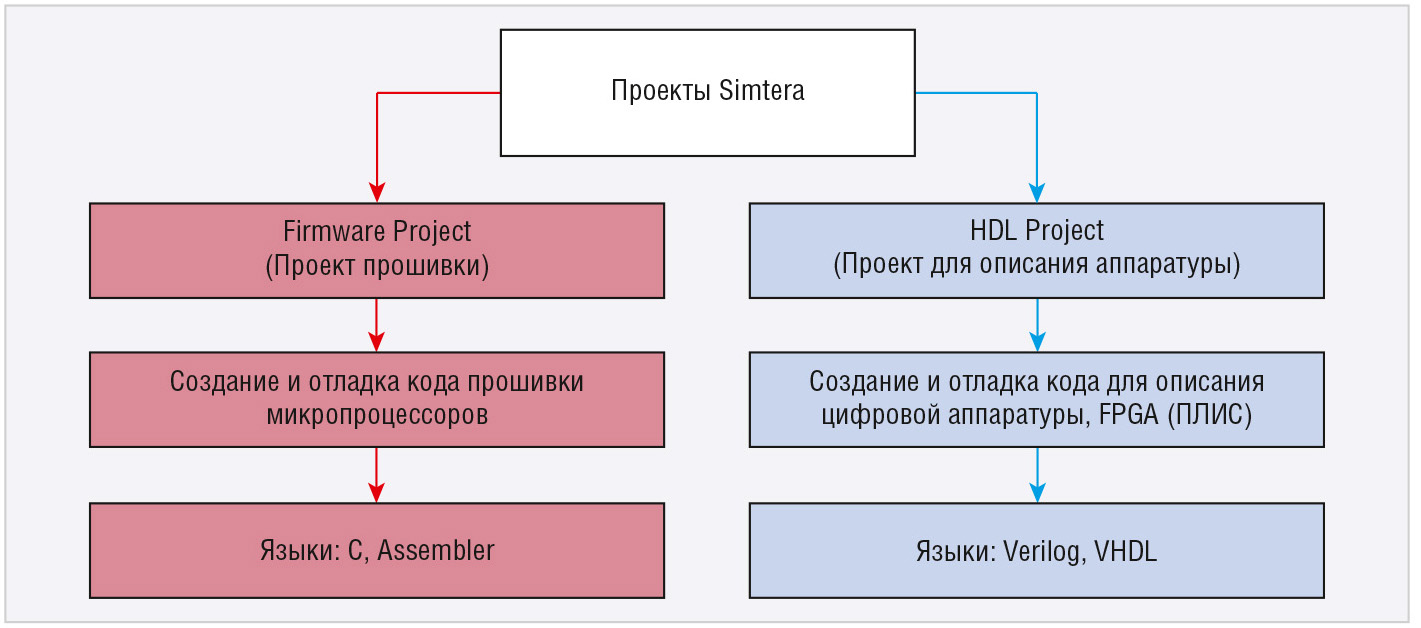

В системе реализован низкий уровень входа, что поможет как опытному, так и начинающему HDL-программисту начать разработку под программируемую логику. Simtera поддерживает спецификации популярных HDL-языков (VHDL 2008 и Verilog 2001), позволяет работать над «смешанными» проектами и пользоваться преимуществами обоих языков в составе одного проекта. Инструменты подсветки синтаксиса и поиска по коду делают разработку ещё более удобной без необходимости использования сторонних текстовых редакторов.

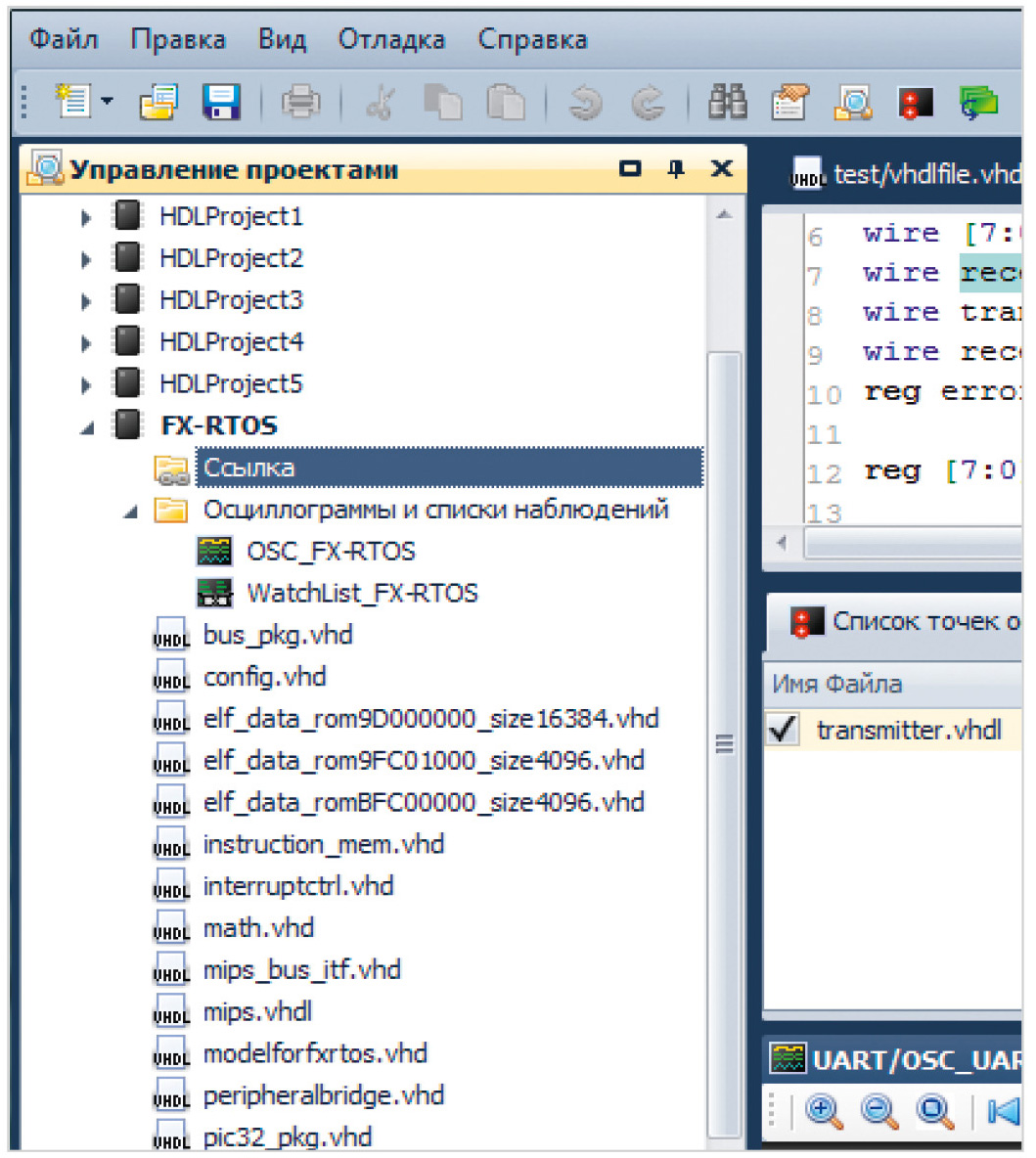

Низкий уровень входа достигается также за счёт интуитивно понятного интерфейса пользователя. Чёткая структура проектов облегчает процесс разработки и навигации. Возможность использования ссылки на проект позволяет не дублировать большое количество одинакового кода, а ссылаться на однажды написанный код из других проектов (см. рис. 1).

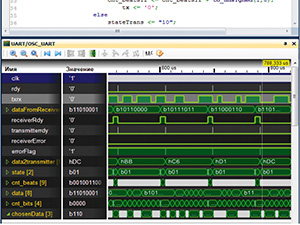

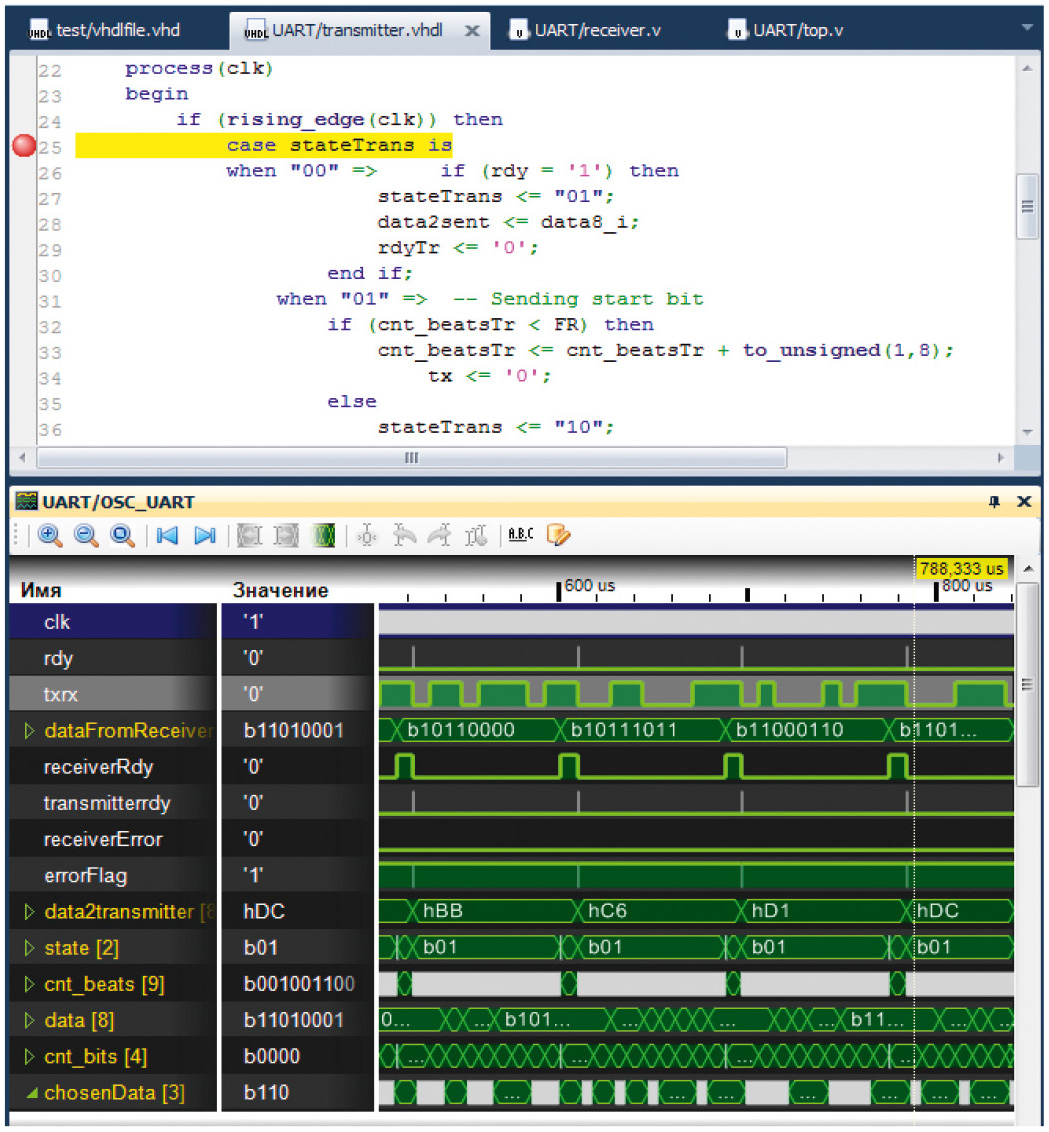

Для отладки в Simtera предусмотрен пошаговый механизм с просмотром значений переменных на интересующем разработчика шаге. Пошаговую отладку можно использовать совместно с осциллографом (см. рис. 2).

Среда моделирования позволяет увидеть содержимое регистров, памяти и проанализировать временны¢е диаграммы. Также для отладки кода в системе предусмотрена верификация с помощью ассертов. Встроенная система просмотра ассертов позволяет быстро локализовать и устранить истинную причину ошибки, в несколько раз сокращая время верификации объекта по сравнению с традиционным моделированием.

Таким образом, Simtera представляет собой единую систему разработки и отладки HDL-кода в едином пользовательском интерфейсе с интегрированной средой отладки.

Режим работы с осциллографом значительно снижает визуальную нагрузку: отсутствует эффект «мерцания» при перемотке данных, при большом масштабе данные сворачиваются, обеспечена плавность отрисовки данных.

Переход со сторонних систем верификации проектов ПЛИС в Simtera

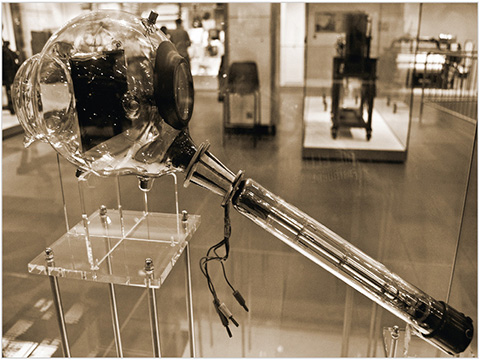

Ориентированность программного пакета Simtera на общепринятые стандарты языков описания аппаратуры позволяет разработчикам перенести наработанные функциональные блоки и тестбенчи. Для этого в системе предусмотрен импорт проектов. Интегрированная среда разработки для ПЛИС и микропроцессоров может стать ещё одной из причин миграции в Simtera (см. рис. 3).

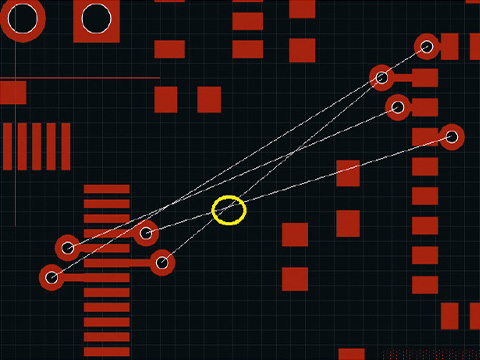

В скором времени предполагается реализовать интеграцию с системой сквозного проектирования печатных плат, что позволит разработчикам HDL и печатных плат обмениваться констрейнами для более эффективного совместного проектирования ПЛИС и плат с их использованием.

Заключение

Основной набор инструментов в системе проектирования и верификации Simtera предназначен для выявления и оперативного устранения ошибок, что положительно сказывается на стоимости и сроках процесса разработки. Мощная система по работе с проектами и HDL-кодом, реализованная в Simtera, делает разработку ПЛИС-проектов более удобной и эффективной.

Литература

- The 2016 Wilson Research Group Functional Verification Study. Part 2. FPGA Verification Effort Trends

- The 2016 Wilson Research Group Functional Verification Study. Part 1. FPGA Design Trends

- The 2016 Wilson Research Group Functional Verification Study. Part 3. FPGA Effort Verification Trends (Continued)

Если вам понравился материал, кликните значок — вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал —не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!