Учебная система моделирования DEEDS (Digital Electronics Education and Design Suite) разработана в Генуэзском университете [1–3] коллективом под руководством Джулиано Донзеллини (Giuliano Donzellini) и состоит из трёх взаимосвязанных компонентов:

- DEEDS-DcS – Digital Circuit Simulator – подсистема моделирования логических схем;

- DEEDS-FsM – Finite State Machine Simulator – подсистема моделирования конечных автоматов;

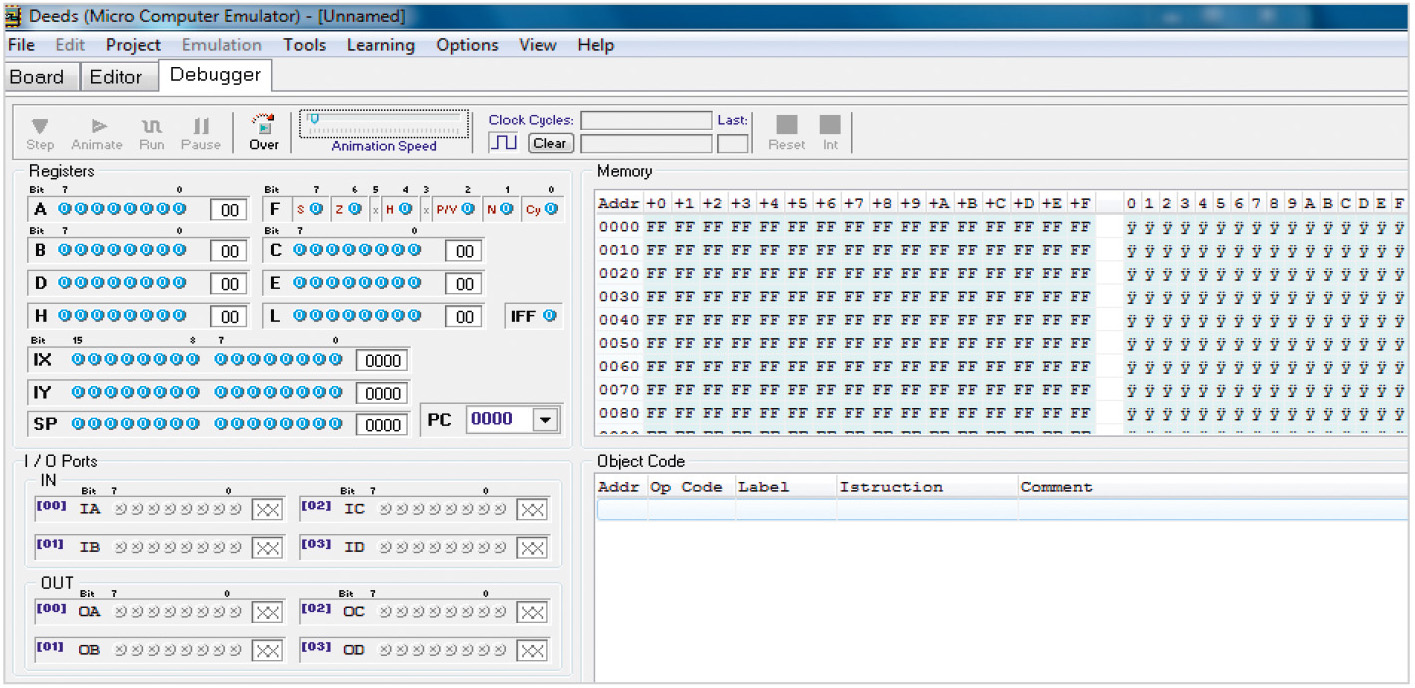

- DEEDS-McE – Micro Computer Emulator – подсистема моделирования микро-ЭВМ.

Термин «взаимосвязанные компоненты» предполагает, в частности, возможность построения модели устройства, в котором часть аппаратуры представлена на уровне вентилей, часть – как конечный автомат и часть – как микро-ЭВМ.

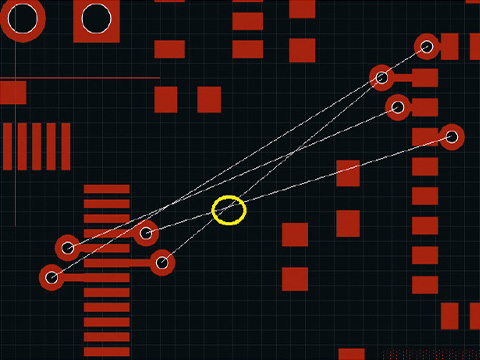

Прилагаемые к DEEDS демонстрационные и учебные материалы покрывают разделы булевой алгебры, проектирования логических схем на уровне вентилей, изучения комбинационных и последовательностных функциональных узлов цифровой аппаратуры, проектирования конечных автоматов и программирования микро-ЭВМ на языке Ассемблер, а также отладки проектов на ПЛИС, используемых в отладочных платах фирмы Altera (сейчас входит в состав Intel). Описания проектов, выполняемых в любой из трёх подсистем, можно конвертировать в код на языке описания аппаратуры VHDL [4] и использовать этот код в промышленных системах автоматизации проектирования (САПР) и учебных курсах, связанных с языками описания аппаратуры.

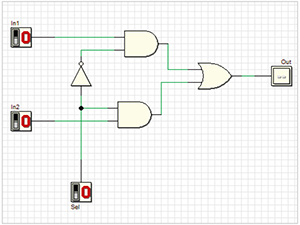

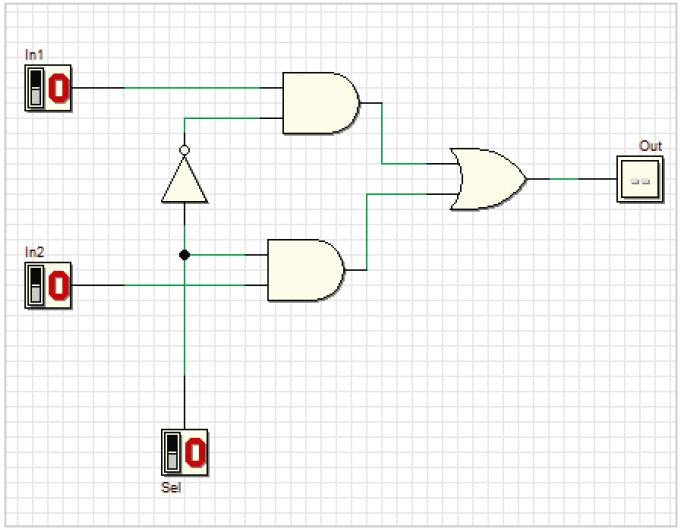

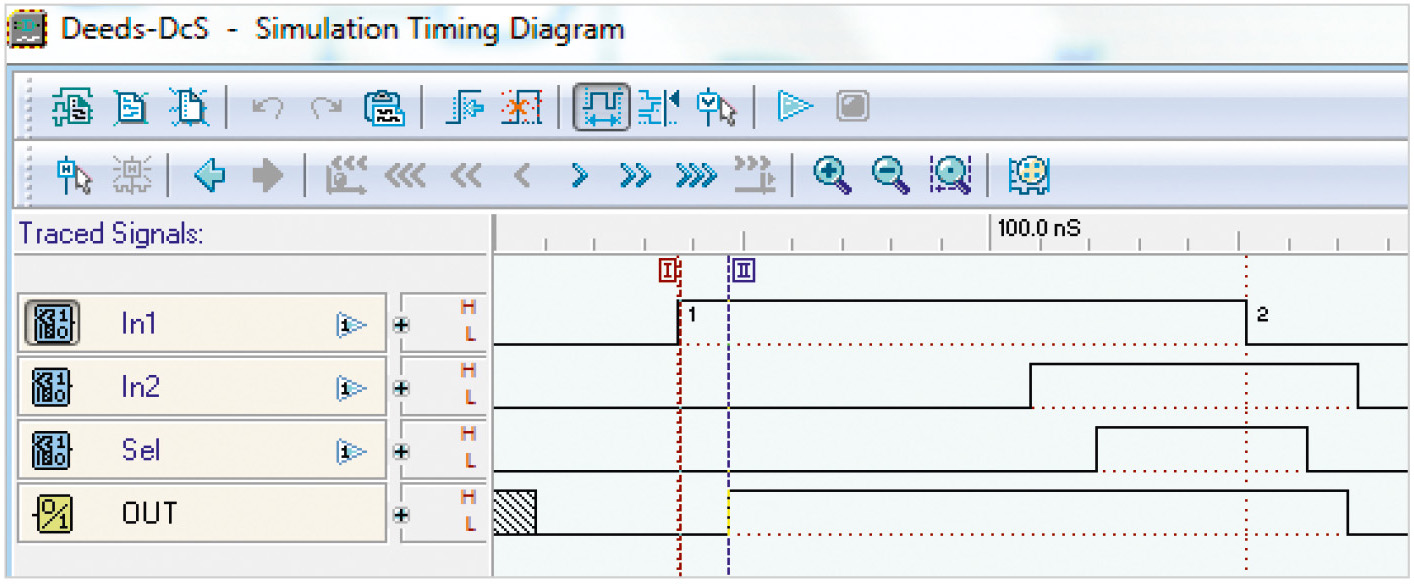

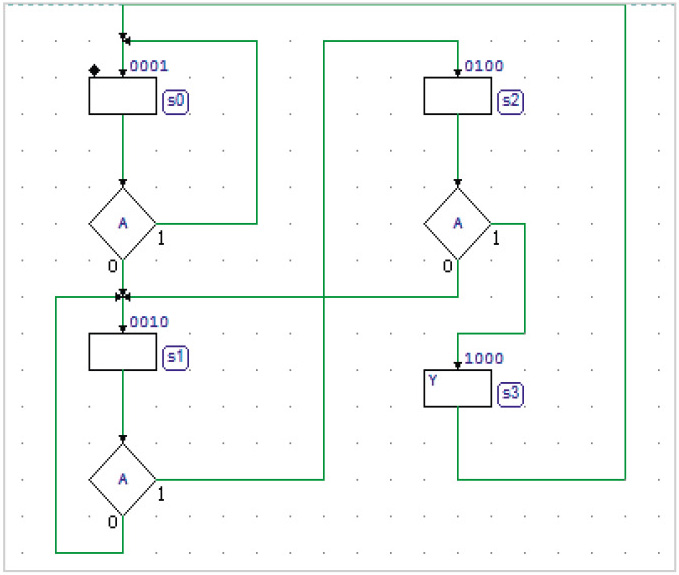

На рисунках 1–6 представлен ряд экранов системы DEEDS, отображающих отдельные фазы решения различных задач пользователей.

На рисунках 1 и 2 показана часть последовательности этапов работы пользователя с подсистемой цифрового моделирования схем d-DcS: схема, которую построил пользователь (см. рис. 1), далее – временнáя диаграмма её моделирования (см. рис. 2).

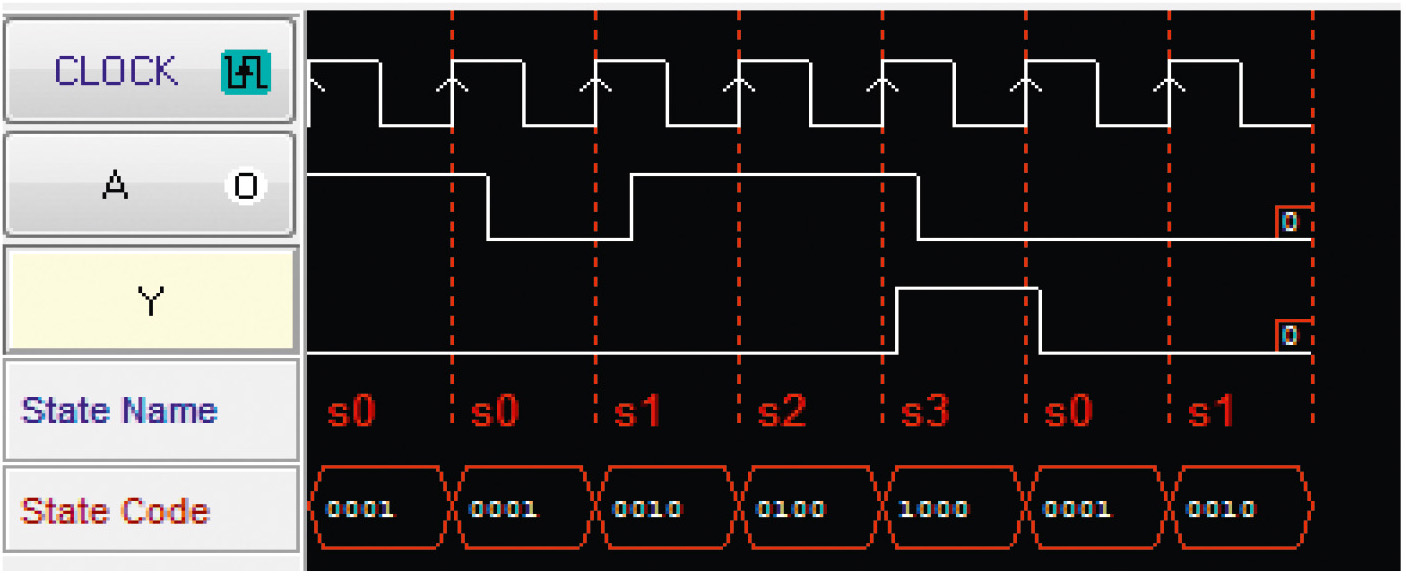

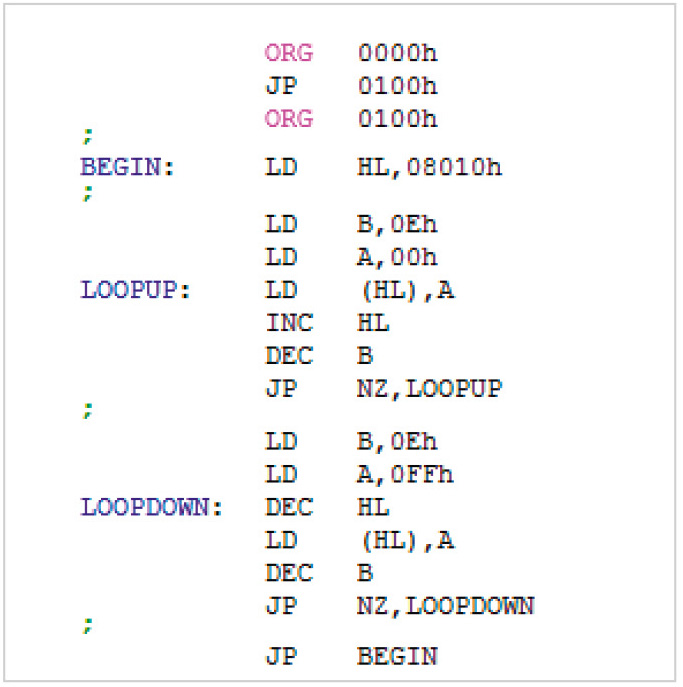

На рисунках 3–6 показаны фрагменты работы пользователя с подсистемами моделирования конечных автоматов DEEDS-FsM (блок-схема автомата и временнáя диаграмма его модели) и DEEDS-McE (программа на языке Ассемблер микро-ЭВМ и процесс её отладки).

Бесплатность, простота установки и освоения системы, нетребовательность к ресурсам инструментальной ЭВМ – всё это можно отнести к преимуществам системы DEEDS. Например, объём скачиваемого установочного файла DEEDS, равный примерно 30 Мбайт, не сравнить с объёмом в 2 Гбайт установочного файла бесплатной студенческой версии систем Active-HDL фирмы Aldec или файла в 6 Гбайт пакета Vivado WebPACK фирмы Xilinx. Хотя возможности указанных фирменных систем намного выше, но и освоение этих возможностей требует гораздо больших усилий – примером может служить объём пособия [5] по САПР ISE фирмы Xilinx.

Тяжеловесность промышленных САПР, предъявляющих повышенные требования к ресурсам инструментальных ЭВМ и квалификации пользователей, становится преградой для их использования в обучении на младших курсах небогатых вузов и колледжей. Системы типа DEEDS могут выступать в такой ситуации как альтернативные.

В настоящее время DEEDS используется в шести европейских технических университетах среднего уровня, её учебные материалы, помимо английского и итальянского языков, переведены на турецкий и испанский. Исходный код реализованных в системе программ содержит более 200 000 строк. Очередные релизы системы выходят примерно раз в год.

Последняя версия системы дополнена средствами, позволяющими пользователю создавать собственные блоки – макросы – из стандартных блоков (вентилей, мультиплексоров, дешифраторов, триггеров и регистров, счётчиков и блоков памяти и т.п.) и использовать их в более сложных проектах. Однако вложенность макросов не допускается.

Особенностью организации учебных материалов DEEDS является их установка на сервер системы. Клиент-серверное взаимодействие с пользователем осуществляется следующим образом. Кликнув на название лабораторной работы, пользователь скачивает её описание. При нажатии на рисунок изучаемой схемы он получает с сервера заготовку – рисунок схемы модельного эксперимента с установленными источниками входных и приёмниками выходных сигналов (саму схему устройства он должен «собрать»), а также заготовку для задания временно́й диаграммы входных сигналов.

Подсистема DEEDS-DcS может использоваться в курсе типа «Цифровая схемотехника» и позволяет выполнять моделирование логических схем в двух режимах.

В режиме анимации пользователь просматривает мигание индикаторов, отображающих значения входных, выходных сигналов и сигналов в контрольных точках схемы на каждом такте.

В режиме временно́го моделирования пользователь получает временны́е диаграммы работы схемы с учётом задержек, фиксированных для определённых групп элементов, – например, все вентили имеют задержку, равную 4 нс.

Подсистема DEEDS-FsM может использоваться в курсе типа «Теория автоматов» и позволяет вводить в ЭВМ граф-схемы переходов автоматов в форме блок-диаграмм и при моделировании получать временны́е диаграммы их работы. Однако, поскольку в DEEDS нет функции синтеза, логическую схему автомата пользователям приходится делать вручную.

Подсистема DEEDS-McE может использоваться в курсе типа «Микропроцессоры и микро-ЭВМ» и позволяет отлаживать программы на языке Ассемблер, являющемся подмножеством Ассемблера популярного восьмиразрядного микропроцессора Z80, моделировать взаимодействие периферийных устройств и подготавливать проекты для имплементации на отладочных платах с ПЛИС типа FPGA фирмы Altera. Разделу, связанному с выполнением отладки проектов на ПЛИС, авторы DEEDS в последнее время уделяют особое внимание [2, 3].

На кафедре ВМСС Московского энергетического института (МЭИ) выполнена работа по русификации учебных материалов подсистем DEEDS-DcS и DEEDS-FsM. Переведены и дополнены вариантами заданий описания лабораторных работ по изучению основ цифровой схемотехники, подготовлены методические указания для пользователей. Имеется также версия традиционных описаний лабораторных работ, которые не рассчитаны на использование сети Интернет во время выполнения занятий. Эти материалы используются как альтернативные в системе дистанционного обучения (ИДДО) МЭИ в курсе «Схемотехника ЭВМ» и в системе очного обучения при верификации курсовых проектов по теме «Проектирование запоминающих устройств»

(6-й семестр).

Литература

- www.digitalelectronicsdeeds.com

- G. Donzellini, D. Ponta «Digital Design Laboratory – A Musical Box on FPGA designed with DEEDS», Proceedings of the «15th Biennal Baltic Electronics Conference (BEC) – BEC 2016», Tallinn, Estonia (EU), 3–5 October 2016, pp.67–70, IEEE Catalog Number: CFP16BEC-USB.

- G. Donzellini, D. Ponta «Introducing Field Programmable Gate Arrays with DEEDS Projects», Proceedings of the «Fourth Interdisciplinary Engineering Design Education Conference – I-EDEC 2014», Santa Clara, California (USA), 3 March 2014, pp.58–65, IEEE Catalog Number: CFP1428S-CDR.

- Поляков А.К. Языки VHDL и VERILOG в проектировании цифровых систем на ПЛИС. – М.: Изд. дом МЭИ, 2012.

- Зотов В.Ю. Проектирование цифровых устройств на основе ПЛИС фирмы XILINX в САПР ISE. – М.: Горячая линия – Телеком, 2003.

Если вам понравился материал, кликните значок — вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал —не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!