Многие современные цифровые микросхемы (ИС) большой степени интеграции, такие как МК и некоторые виды ПЛИС имеют оперативную память данных, которой зачастую не хватает для записи больших объёмов информации. В современном мире микро-электроники широкое распространение получили динамические и статические оперативные запоминающие устройства (ОЗУ).

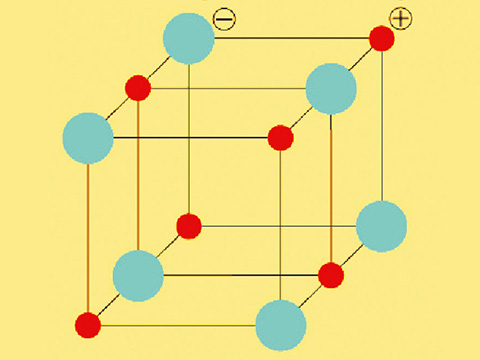

В динамических ОЗУ система хранения данных организована через заряды ёмкостей МОП-структур, которые необходимо с определённой периодичностью подзаряжать (регенерировать) для исключения саморазряда, ведущего к потере записанной информации.

Архитектура построения статических ОЗУ основана на триггерах, которые сохраняют своё состояние при поданном на ИС питании. Современные наработки в технологии производства микросхем ОЗУ позволяют повышать степень интеграции, но и приводят к появлению большего количества дефектов. Поэтому на сегодняшний день остаётся актуальной задача тестирования ИС ОЗУ как на этапе входного контроля на предприятиях, производящих устройства микроэлектроники, так и в компаниях, занимающихся поставками комплектующих.

Любая ИС ОЗУ содержит шину управления, шину адреса и шину данных. Очевидно, что для функционального тестирования необходимо задавать воздействия на ИС с учётом требования выявления дефектов.

Самым очевидным способом проверки работоспособности ОЗУ является проверка режимов управления, записи и чтения данных. Т.е. функцио-нальный контроль сводится к записи данных в память и чтение данных из памяти с последующим сравнением считанной и записанной информации. Очень важной особенностью данной операции является выбор – какой код записывать и считывать для выявления неисправностей.

Как показывает практика, скрытые дефекты ИС ОЗУ чаще всего бывают двух типов – сбой в ячейке по определённому адресу или адресам (в ячейке памяти хранится ошибочное значение, отличающееся от записываемого) и, так называемое, «залипание» бита памяти (когда значение определённого бита по данному адресу невозможно изменить).

Одним из вариантов для проверки является комбинированный подход по тестированию, заключающийся в применении комплекса записываемых кодов, которые включают в себя «шахматные» и «переменные» коды.

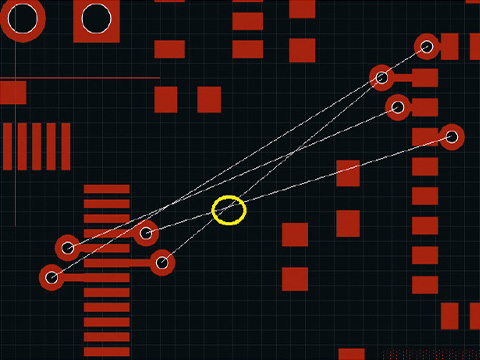

Для задания внешних воздействий на ИС памяти используется внешний МК или ПЛИС, порты ввода/вывода которых генерируют сигналы шины управления, шины адреса и шины данных необходимой размерности.

На первоначальном этапе в ИС памяти последовательно записывается «шахматный» код 5516, далее производится считывание данных из ОЗУ с последующим сравнением с записанными значениями. Если сравнение проходит успешно (все считанные значения соответствуют записанным), то в ИС записывается инверсный «шахматный» код АА16 и считывание с последующим сравнением. Данный комплекс операций проводится несколько раз с инвертированием кода после каждого «прохода».

Далее тестирование проводится «переменным» кодом. В идеальном варианте в ячейки с соседними адресами записываются прямо противоположные псевдослучайные данные, однако это значительно увеличивает время тестирования, т.к. для получения наиболее полного тестирования необходимо достаточно большое число циклов с изменением данных после каждого цикла.

Но если применять «переменные» коды в сочетании с «шахматными» кодами, то вполне достаточно ограничиться записью по каждому адресу значения, отличающегося от значения предыдущего адреса и последующего.

В самом простом случае в ячейку памяти записывается её адрес, что позволяет при наличии дефекта легко определить, на каком адресе произошёл сбой. После заполнения всех ячеек памяти следуют операции чтения и сравнения с записанными данными. В случае успешного завершения операции сравнения, можно произвести цикл ещё раз с записью в ячейку инверсного значения адреса с последующим чтением и проверкой.

Вышеописанный комплекс функционального тестирования позволяет выявить дефекты ИС памяти с большой достоверностью. Перечисленные алгоритмы «шахматных» и «переменных» кодов позволяют не только выявить наличие дефектных ячеек или отдельных битов, но и определить их адреса. Однако следует учитывать: когда задающим (управляющим ИС памяти) устройством является МК, есть ограничение по быстродействию тестирования. В случае высокоскоростных ОЗУ следует применять ПЛИС для достижения большей скорости обмена данными и тестирования ИС на максимально возможных частотах.

ЛИТЕРАТУРА

Если вам понравился материал, кликните значок — вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал —не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!