Введение

Современная цифровая электронная аппаратура характеризуется постоянным увеличением быстродействия интегральных устройств, что усложняет обеспечение целостности и латентности сигнала при проектировании топологии печатных плат [1, 2]. Целостностью сигналов можно управлять посредством контроля импеданса печатных проводников, который достигается с помощью порядка конструкции слоёв печатной платы и шириной дорожек, которые будут использоваться на каждом слое. Основной способ решения проблем латентности сигнала (проблема синхронизации сигналов со стороны приёмника, задержка распространения сигналов, расфазировка сигналов) – это выравнивания длин проложенных дорожек, по которым проходит сигнал [3]. Рассмотрим инструменты решения задачи синхронизации сигналов в САПР Altium Designer 16.0.

Проблема и решение

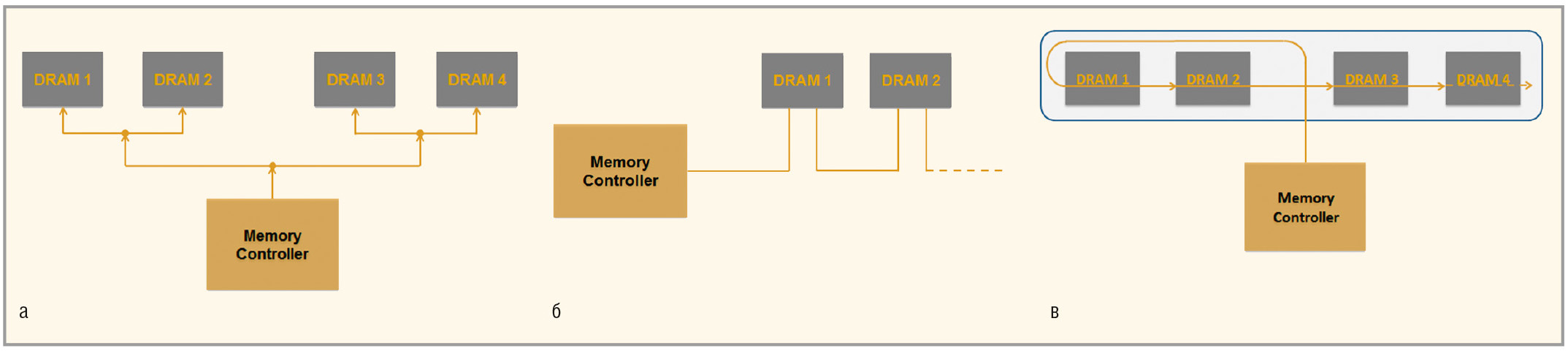

Для группы сигнальных печатных проводников, состоящих из двух контактов, соединяющих выходной контакт источника сигнала и единственный входной контакт приёмника сигнала, вычисление и сравнение длин является стандартным процессом. Дело обстоит иначе, когда есть серия элементов на пути прохождения сигнала или есть более двух контактов в сигнале, который может быть разведён с использованием различных методов трассировки: древовидная / Т-образная топология (см. рис. 1а), шлейф / «гирляндная» топология (см. рис. 1б), сеть / Fly-By-топология (см. рис. 1в).

T-образный подход к трассировке подразумевает прохождение сигнала от единственного контакта выходного устройства и разделение его на два ответвления одинаковой длины к принимающим устройствам, что приводит к появлению отражений и переменной сумме дополнительных искажений сигнала на другом ответвлении в каждой точки ветвления.

Fly-By-трассировка – это, по существу, разновидность «гирляндной» топологии. Она представляет собой последовательное прохождение сигнала от источника до приёмника, далее – до следующего приёмника и останавливается на последнем устройстве. Эта топология устраняет отражения, но недостаток её состоит в том, что задержка сигнала увеличивается для каждого последующего устройства в цепочке. Такая топология применяется, когда выходное устройство может компенсировать смещение сигнала для каждого приёмного устройства, используя метод выравнивания сигнала.

Решением обозначенной задачи является перенос конструктивных требований, позволяющих обеспечить синхронизацию сигналов (например, максимальная длина трассировки), в ряд правил проектирования, таких, как правило «длины», чтобы гарантировать синхронизацию и правило «соответствия длины», чтобы выявить потенциальные несоответствия синхронизации.

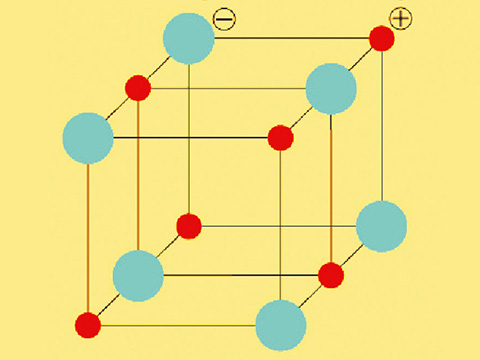

Теперь конструктор рассматривает сигналы с точки зрения их функции (см. рис. 2).

В данном случае (см. рис. 2) имеется адресный сигнал, который должен быть разведён от источника сигнала к каждому устройству памяти. Чтобы добиться этого, применяется Fly-By-топология с нагрузочным резистором в конце линии. Также можно задать терминирующие резисторы у источника сигнала. Даже если адрес A0 проходит через терминирующий резистор, то для конструктора с другой стороны этого резистора сигнал всё ещё имеет адрес A0.

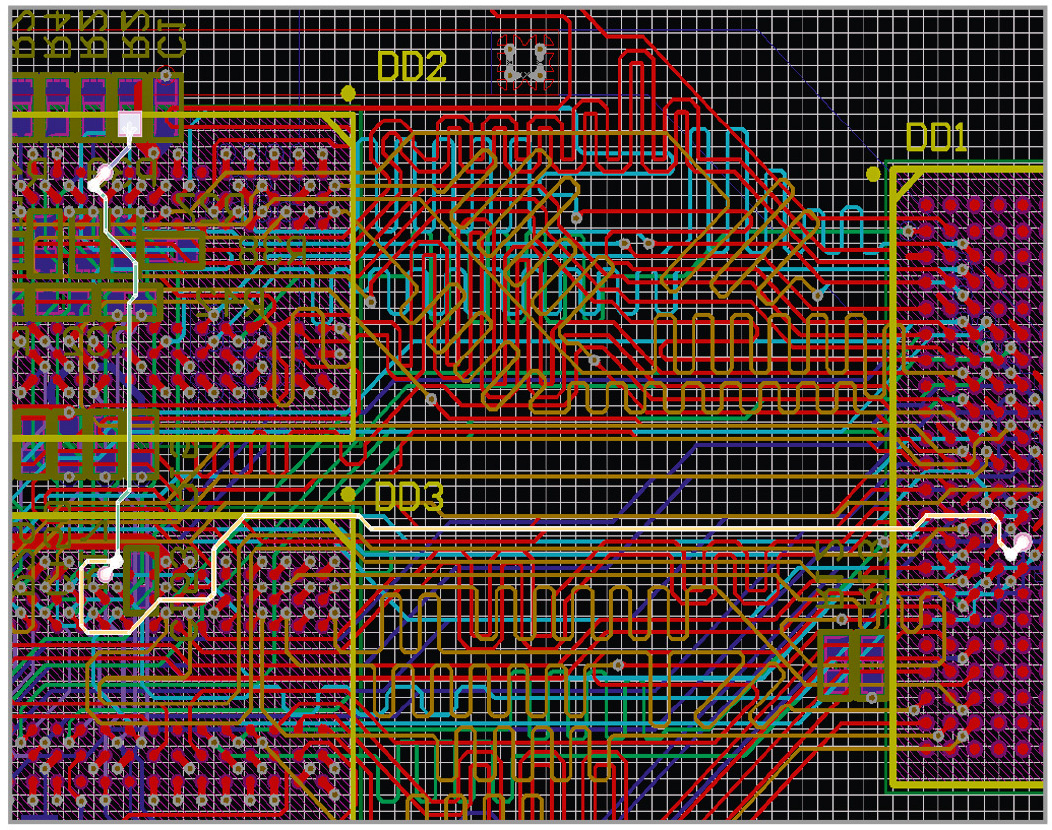

Топологический редактор САПР рассматривает каждый сигнал просто как ряд связанных контактов (обычно называемый цепью). Цепь A0 идёт от входного контакта к одному контакту компонента памяти, затем к контакту другого компонента памяти и т.д. Как только в цепь последовательно включается терминирующий резистор, адресная цепь становится двумя дискретными цепями. Это мешает конструктору контролировать выполнение ключевых конструктивных требований, таких как «длина» и «соответствие длины». Начиная с версии Altium Designer 15.0, для разрешения этой проблемы введена новая функция, названная xSignals. Эта функция обеспечивает корректную обработку пути прохождения высокоскоростного сигнала.

xSignals – это определяемый конструктором маршрут прохождения сигнала между двумя узлами. Это могут быть два узла в одной цепи или два узла в связанных цепях, разделённых компонентом. Функция xSignals необходима для определения правил проектирования, таких как Length (Длина сигнала) и Matched Length (Соответствие длины), которые используются во время проектных задач, например, для интерактивной настройки длины путём формирования зигзагообразной дорожки.

Создание объектов xSignals

Формирование объектов xSignals производится только в топологическом редакторе. В отличие от обычных цепей, которые создаются на этапе проектирования электрической схемы, формирование xSignals производится следующими методами:

- Create xSignals – создать xSignals;

- Create xSignals from Selected Pins – cоздать xSignals по выбранным контактам;

- Create xSignals Between Components – создать xSignals между компонентами;

- Create xSignals from Connected Nets – создать xSignals из связанных цепей.

Рассмотрим различные варианты создания одиночных xSignals:

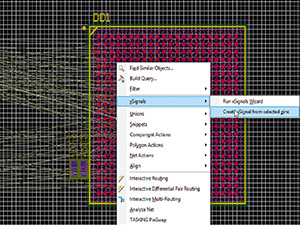

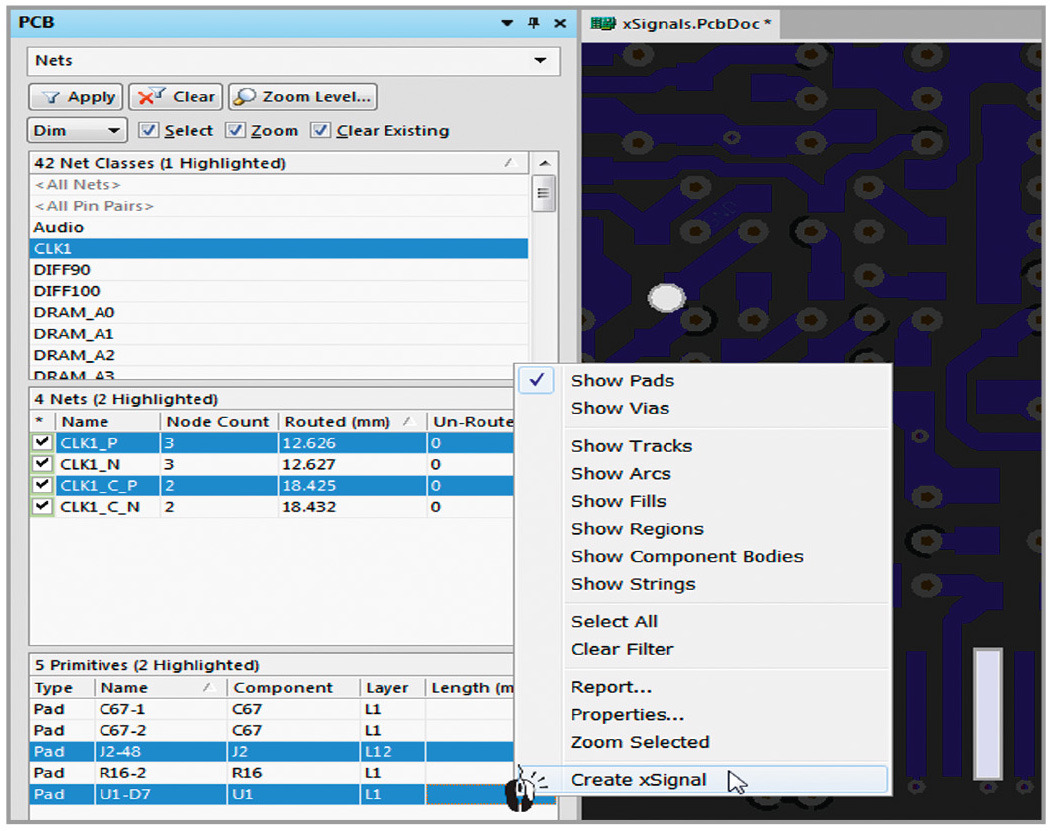

- Установите PCB Panel (Панель печатной платы) в режим Nets (Цепи), выберите требуемые цепи, определите и выберите требуемые контактные площадки в нужных цепях в разделе Primitives (Примитивы), затем щёлкните правой кнопкой по одной из выбранных контактных площадок и выберите команду Create xSignals (Создать xSignals) из контекстного меню (см. рис. 3).

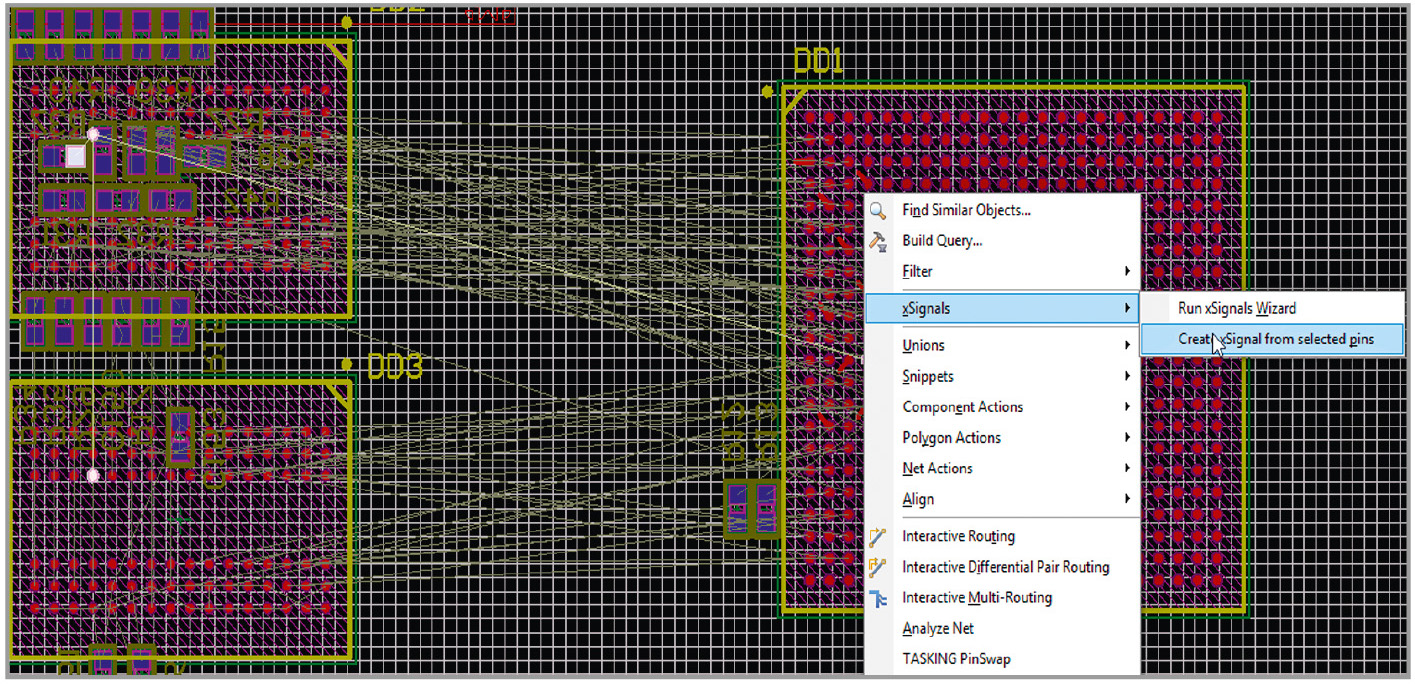

- Выберите два контакта (контакта компонента) в рабочей области редактора печатной платы, затем щёлкните правой кнопкой по нужному контакту и выберите xSignals > Create xSignals from Selected Pins (xSignals > Создать xSignals из выбранных контактов) из контекстного меню (см. рис. 4).

В случаях, когда требуется сформировать группу xSignals, применяются команды Create xSignals Between Components и Create xSignals from Connected Nets [4], которые доступны в подменю Design > xSignals.

Работа с объектами xSignals

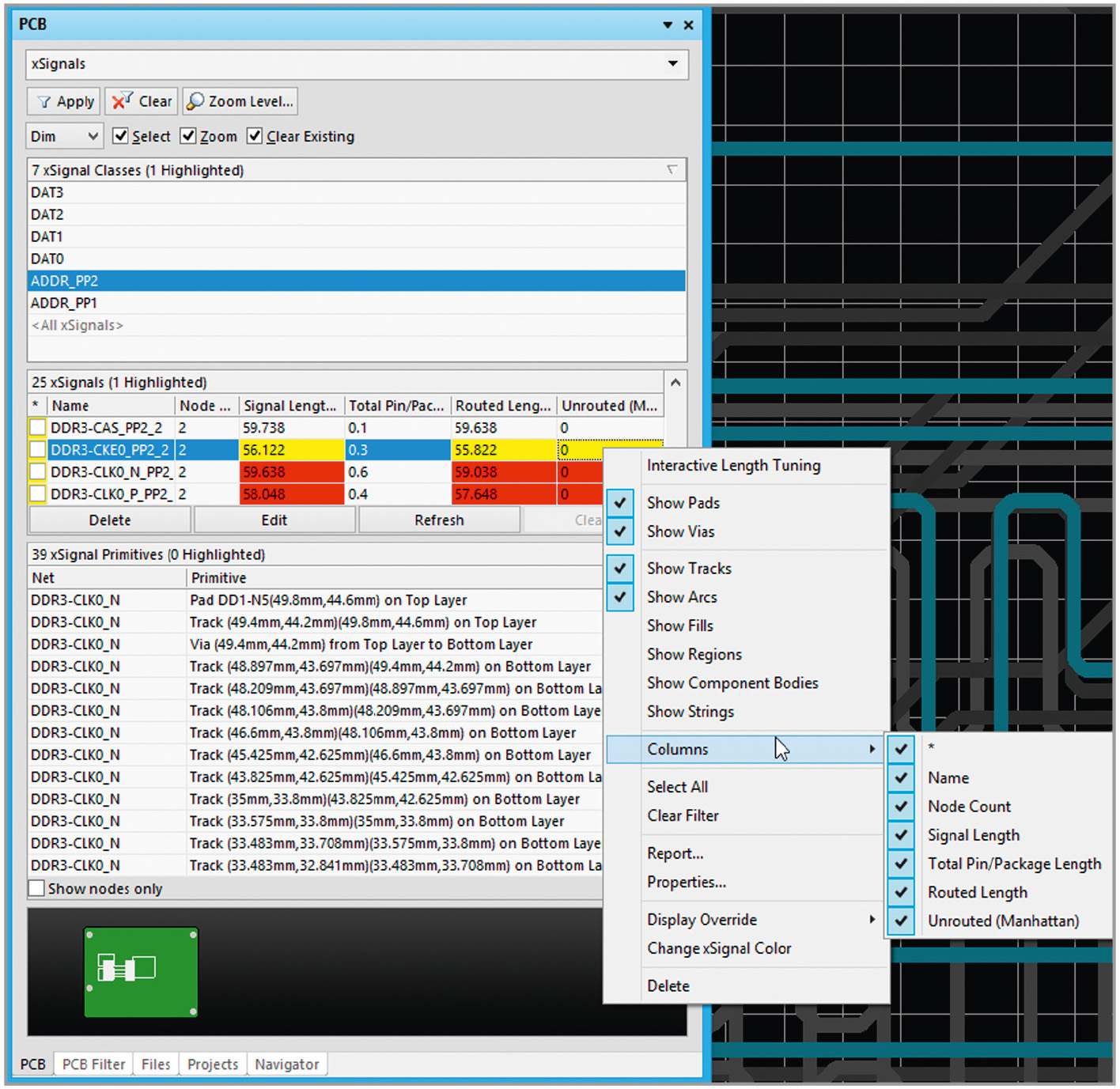

Для работы со списком классов xSignals, отдельными маршрутами xSignals и их примитивами предназначен подрежим xSignals рабочей панели PCB, включаемый выбором из выпадающего списка вверху панели (см. рис. 5).

При выборе требуемого объекта xSignals Classes или xSignals в соответствующем разделе панели в контекстном меню доступны следующие команды:

- для элементов в xSignals Classes: Add (Добавить), Delete (Удалить) или Edit (Редактировать); формирование классов xSignals важно для корректного создания правил проекта;

- команда Change xSignals Color (Выбор цвета всех соединительных цепей xSignals) доступна отдельно как для xSignals Classes, так и для одиночного xSignals; использование цвета помогает идентифицировать связанные цепи во время трассировки.

Формирование правил проектирования

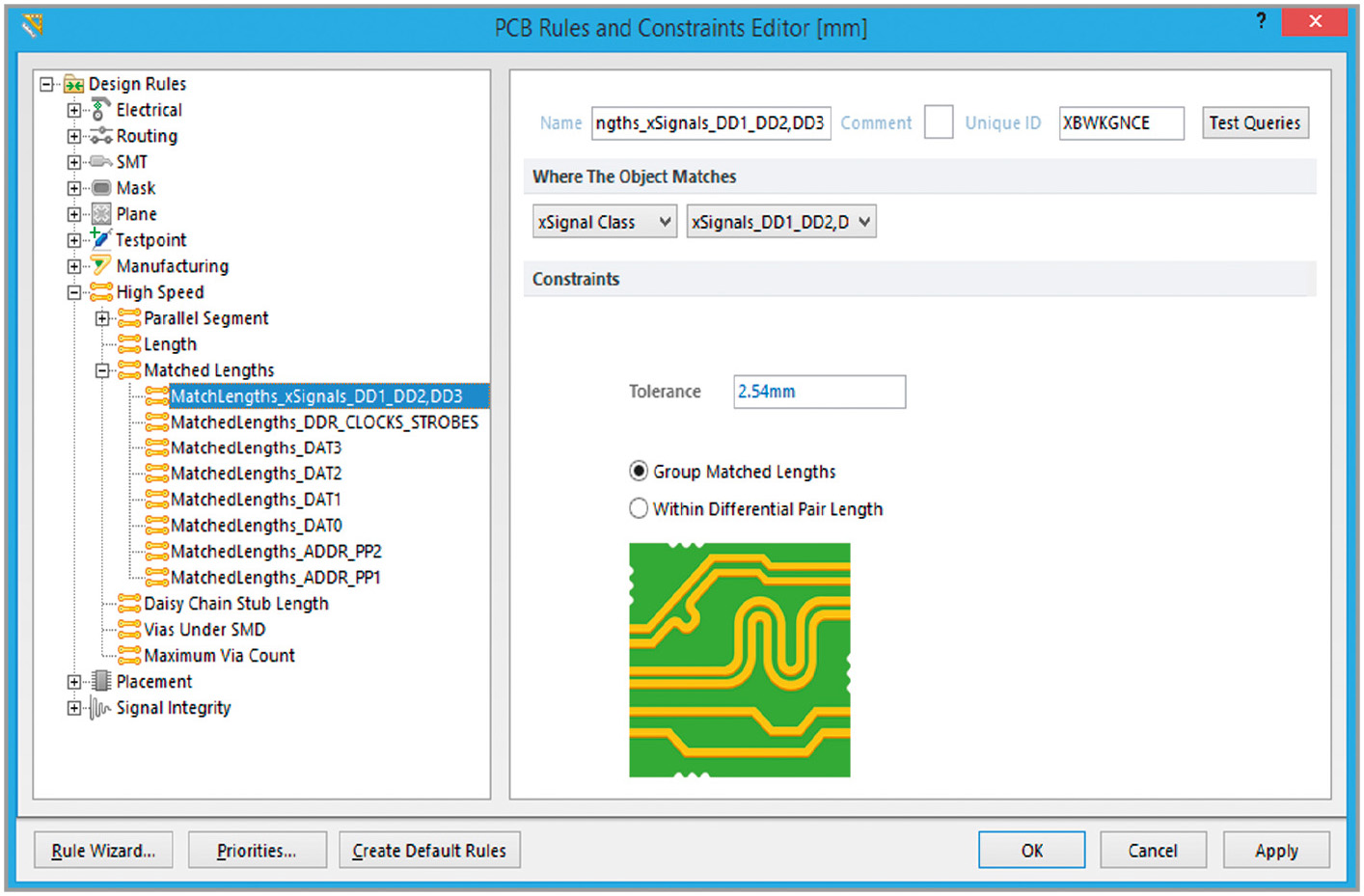

После определения объектов xSignals, для них формируются соответствующие конструкторские требования в редакторе правил, раздел High Speed в Design > Rules (см. рис. 6), где определяются правила Length (Длина сигнала) и Matched Length (Соответствие длины).

Правило Length устанавливает максимально разрешённую длину прохождения сигнала.

Правило Matched Length устанавливает соответствие длины сигнала относительно выбранного объекта. Возможны два варианта исполнения правила:

- Group Matched Lengths – выравнивание длин в заданной группе;

- Within Differential Pairs – выравнивание длин внутри дифференциальной пары.

Для определения области действия правила используются следующие выражения для запроса фильтрации:

- InxSignal – объект в выбранном маршруте xSignals, например, InxSignals(‘DRAM_A0_PP1’);

- InxSignalClass – объект в выбранном классе xSignals, например, InxSignalClass(‘PCIE’);

- IsxSignal – объект xSignals с указанным именем, например, IsxSignals(‘DRAM_A0_PP1’);

- ключевые слова атрибутов;

- InAnyxSignal – объект в любом маршруте xSignal, например, InAnyxSignal.

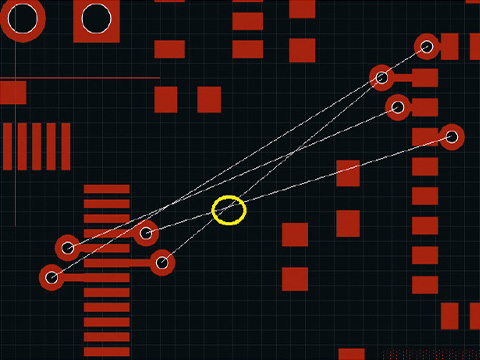

Выполнение правил проверяется во время размещения объектов (так называемый Online DRC) или после проектирования (так называемый Batch DRC (Пакетная проверка)). Контроль правила Matched Length производится в рабочей панели PCB в режиме xSignals (см. рис. 5), результат отображается в строке состояния (количество узлов, длина маршрута, неразведённая длина, длина трассировки, суммарная длина выводов микросхем) трассируемой цепи в виде цветовой индикации:

- белый цвет – в пределах заданного значения;

- жёлтый цвет – если длина дорожки меньше длины, заданной правилом;

- красный цвет – если длина дорожки превышает максимум заданного значения.

Заключение

Во второй части статьи будет описан xSignal-мастер, используемый для формирования групп xSignals. Также будет рассказано о расчёте Signal Length (Длина маршрута сигнала) и расчёте суммарной длины трассы маршрута сигнала в САПР Altium Designer 16.0.

Литература

- Кечиев Л.Н. Проектирование печатных плат для цифровой быстродействующей аппаратуры. М. ООО «Группа ИТД». 2007.

- Джонсон Г. Грэхем М. Высокоскоростная передача цифровых данных: высший курс чёрной магии. М. ИД Вильямс. 2005.

- Попов С., Попов Ю. Выравнивание задержек сигнала. Проблемы и решения. Печатный монтаж. 2013. №5.

- Altium. High Speed Design with xSignals. www.techdocs.altium.com/display/ADOH/High+Speed+Design+with+xSignals.

Если вам понравился материал, кликните значок — вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал —не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!