Необходимость тестирования микросхем появилась, собственно, в момент их изобретения, ведь производителям необходимо всегда быть уверенными в характеристиках своей продукции. Типичная архитектура таких тестовых систем состоит из нескольких источников/измерителей (по одной паре на каждый вывод), оснащённых большим объёмом быстрой памяти. Каждый такой канал может быть сконфигурирован в качестве выходного для воздействия на вход микросхемы, или входного – для регистрации отклика с её выхода. В память заносятся пакеты данных, называемые тестовыми векторами, которые выдаются источником в качестве воздействия на испытуемую микросхему. Компаратор сравнивает состояния выходов микросхемы с ожидаемыми значениями, также хранимыми в ячейке памяти канала.

С течением времени в этой технологии появилось множество улучшений: увеличилась тактовая частота, появилась возможность установки уровня напряжения источника и скорости его нарастания, а также значения пороговых уровней по входу. Тем не менее, базисная архитектура работы каналов не изменилась и по сей день. Это и приводит к возникновению упомянутых вопросов от заказчиков, что естественно при рассмотрении типовой спецификации тестера микросхем на архитектуре быстрой памяти. Это оборудование подходит для тестирования отдельных микросхем, но при этом также обладает многими недостатками, в частности при выполнении задачи поиска неисправностей на печатных платах. Перечислим их:

- Цена. Использование высокоскоростной памяти и сопутствующей управляющей логики приводит к тому, что получаемая система является весьма дорогой. Цена некоторых решений может достигать более полумиллиона фунтов стерлингов.

- Сложность и габариты. Сложность многоканальных тестеров, построенных на этой архитектуре, приводит к тому, что они обычно представлены в стационарном исполнении

- и их транспортировка затруднительна. Стоимость обслуживания при этом также высока.

- Конечный набор тестовых программ. Простая микросхема, такая как 74F74, может быть установлена на печатную плату множеством способов. Тестер на архитектуре быстрой памяти потребует использовать отдельную тестовую программу для каждой схемы внешних соединений. Таким образом, для выполнения этой программы необходимо предварительно описать схему. Иными словами, нельзя просто «подключить и протестировать» микросхему без предварительного написания программы.

- Время программирования. Как было отмечено, тестовые программы необходимо корректировать всякий раз, когда конфигурация проверяемой платы изменяется. Это потребует дополнительных временны¢х затрат и отрицательно скажется на стоимости владения.

- Фиксированная схема коммутации с микросхемой. На платах с плотным размещением компонентов доступ к микросхеме затруднён, следовательно, как возможность присоединения к ней зажима пробника различными способами, так и допустимость контакта этого зажима с частью другого компонента на плате в процессе тестирования, может быть неоценима. Но поскольку тестовые векторы в архитектуре быстрой памяти жёстко заданы для каждого канала, то для таких систем эти особенности недоступны.

Поскольку указанные недостатки систем на архитектуре быстрой памяти видятся значительными, особенно при решении задач поиска неисправностей на плате, тестеры компании построены по другому принципу работы.

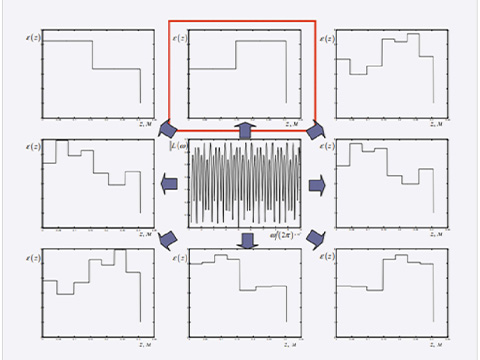

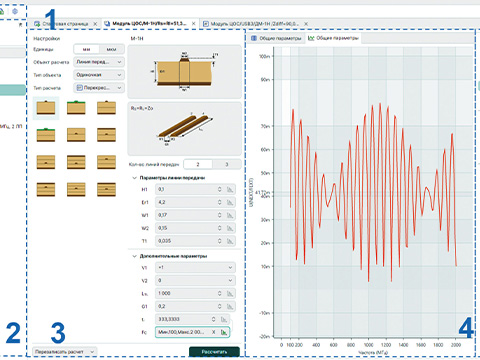

Источники сигналов в архитектуре любого оборудования ABI управляются посредством программного обеспечения. Шаблоны воздействий на тестируемую микросхему и ожидаемых откликов от неё содержатся в тестовой программе высокого уровня, что отличает её от классической последовательности тестовых векторов. В процессе работы программы выходы микропроцессора обеспечивают заданное воздействие на тестируемую микросхему. Запись данных в выходные порты осуществляется посредством специализированной микросхемы. Следовательно, тестовые векторы генерируются «на лету» в ходе тестирования, а не загружаются в память до его проведения. Этот принцип даёт несколько важных преимуществ:

- Низкая цена. Архитектура на специализированной микросхеме, управляемой микропроцессором, позволяет получить многоканальный (до 2048 выводов) тестер по относительно низкой цене. Это достигается благодаря устранению дорогих микросхем памяти и связанной с ними управляющей логики.

- Размер. 64-канальный тестер микросхем на архитектуре быстрой памяти невозможно разместить в форм-факторе привода CD-ROM. Исполь-

- зование специализированной микросхемы позволило создать компактную, а, следовательно, портативную систему поиска неисправностей, что справедливо даже для системы с 2048 каналами.

- Автоматический учёт схемы соединений. Для примера: если в течение тестирования обнаружится, что вывод подключён к шине земли, тестовая программа изменит свою структуру. Иными словами, тестовая программа автоматически подстраивается под схему соединений микросхемы. Эта функция неоценима при поиске неисправностей на плате, так при её отсутствии почти невозможно получить надёжные результаты. Некоторые системы других производителей используют архитектуру быстрой памяти и, таким образом, ограничены в своих возможностях при поиске неисправностей. Другие – вообще неспособны подстроиться под схему соединений и, проще говоря, являются фактически бесполезными при задаче поиска неисправностей, так как не могут протестировать микросхему функционально.

- Автоматическое позиционирование зажима. Тестовая программа также может изменять программные номера своих выводов для того, чтобы обеспечить выбор способа подключения тестового зажима. Он может быть подключён любым способом, даже частично контактируя с другими компонентами, при этом без какого-либо влияния на результаты тестирования.

Пришло время сформулировать ответы на озвученные ранее вопросы заказчиков.

«Какова скорость тестирования?» Спецификация микросхемы учитывает допуски и отклонения при их изготовлении. Многие из указанных в ней параметров, естественно, могут выйти за пределы указанных ограничений. Таким образом, микросхемы должны быть протестированы, используя высокоскоростное оборудование (по цене более полумиллиона фунтов стерлингов) для отсева образцов, параметры которых не соответствуют спецификации. Оставшиеся микросхемы идут на продажу и затем входят в состав устройств. На момент отгрузки с завода они все исправны и соответствуют своим спецификациям. Однако в дальнейшем микросхемы могут быть повреждены в процессе использования из-за скачков напряжения, перегрева, перегрузки по току или статики. Все эти факторы вызывают внезапные отказы. Менее 2% всех отказов микросхем на плате приходятся на проблемы, связанные со скоростью её работы. Таким образом, дополнительная цена оборудования, уплаченная за возможность тестирования микросхемы на полной скорости её работы, не выглядит обоснованной. Приведём пример. Некоторое оборудование для поиска неисправностей может работать на скорости до 10 МГц. Если микросхема 74F74 протестирована на частоте 10 МГц, то её работоспособность в реальной схеме при тактовой частоте в 120 МГц не гарантируется. Таким образом, повышение стоимости оборудования за счёт обеспечения скорости тестирования в 10 МГц необоснованно. Скорость тестирования продукции компании ABI значительно ниже, но не может быть точно специфицирована, так как тестовая программа модифицируется в процессе тестирования и скорость меняется от микросхемы к микросхеме. Она не зависит от скорости ПК или тактовой частоты тестера. В результате ответ на вопрос может быть сформулирован следующим образом: «Скорость тестирования при поиске неисправностей не имеет существенного значения, поскольку 98% отказов микросхем от неё не зависит».

«Каков объём памяти на вывод?» Архитектура продуктов компании ABI имеет практически неограниченный объём эквивалентной памяти, так как тестовые векторы генерируются «на лету» по ходу работы. Рассмотрим в качестве примера задачу тестирования памяти RAM. При использовании тестера на архитектуре быстрой памяти проведение одиночного цикла запись/чтение/сравнение может обеспечиваться 25 тестовыми векторами. Если объём памяти составляет 128K × 8, то весь процесс потребует уже более 13 миллионов тестовых векторов. Эта цифра вытекает из рассмотренного принципа работы систем на архитектуре быстрой памяти. В рассматриваемой архитектуре ABI написание тестовой программы для решения данной задачи может занимать около 30 минут. Поэтому итоговый ответ на заданный вопрос звучит так: «Эффективная память фактически бесконечна, так как тестовые векторы продолжают генерироваться по ходу тестирования».

В заключение приведём несколько фактов:

- тестеры компании ABI используют приведённую архитектуру уже более 30 лет;

- функции автоматической компенсации схемы соединений и автоматического позиционирования зажимов были разработаны компанией ABI в 1984 г.;

- более 98% отказов микросхем возникают внезапно, а более 75% отказов на плате происходят вследствие обрывов или замыканий, но ни те, ни другие факторы не зависят от скорости работы;

- заявленная архитектура позволяет строить гибкие тестовые системы, объединяющие широкий набор инструментов для поиска неисправностей в одном корпусе.

Если вам понравился материал, кликните значок - вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал - не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!