Продолжая рассказ о ПЛИС Achronix, невозможно обойти вниманием аппаратное ядро контроллера динамической памяти. В ПЛИС Speedster22i HD 1000 имеется шесть таких ядер, что позволяет адресовать суммарно более 412 Гбайт данных. В данной статье рассматриваются устройство аппаратного ядра и принципы работы с ним.

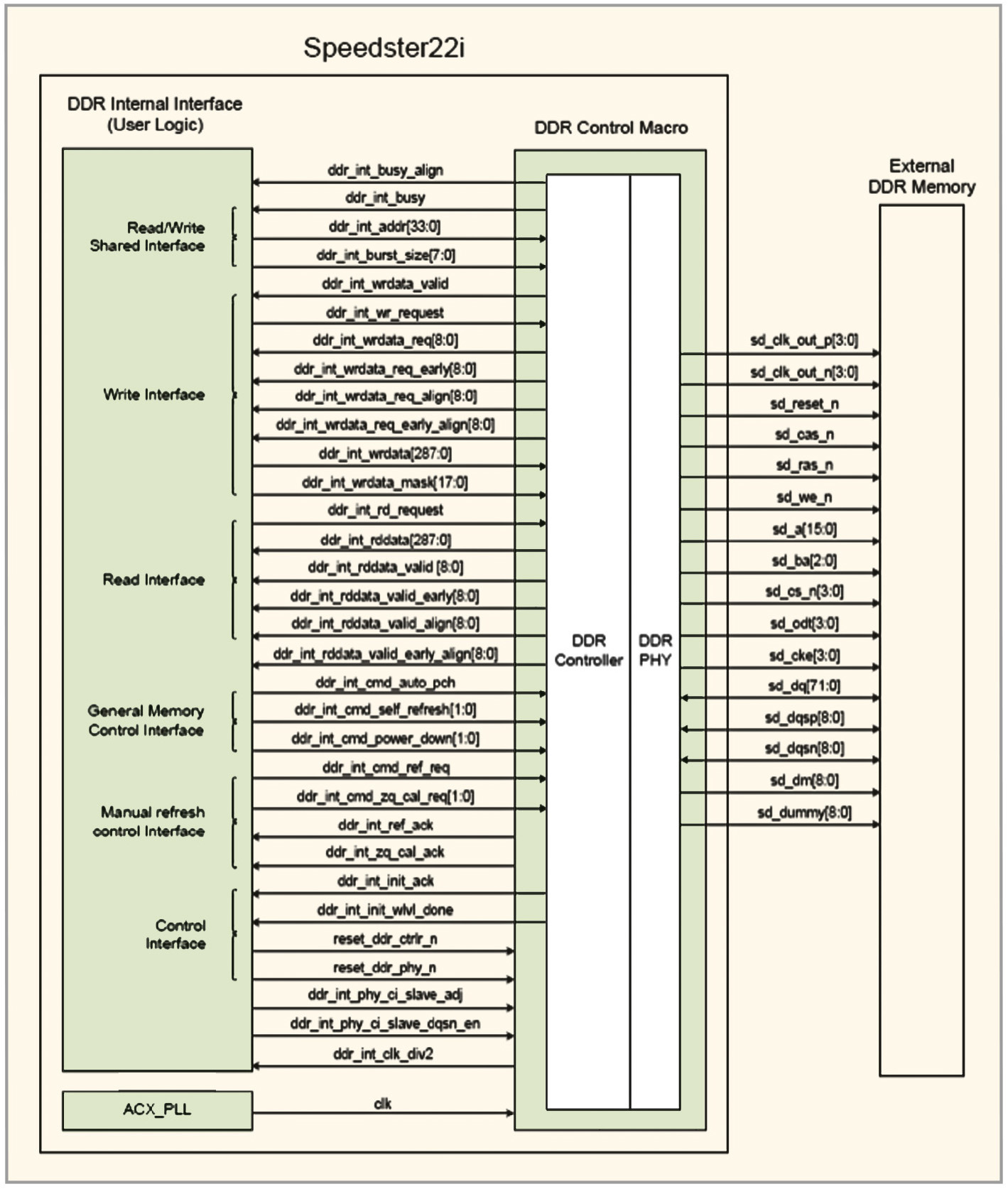

Ядро позволяет работать с памятью типа DDR, DDR-2 и DDR-3 различной организации. На рисунке 1 показана типовая схема подключения из руководства [1].

Блок, обозначенный как «DDR Control macro», является встроенным аппаратным ядром, а блок UserLogic реализуется на логических элементах ПЛИС. Задачей разработчика является конфигурирование аппаратного ядра и написание интерфейса пользователя.

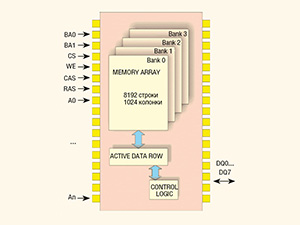

Поскольку модули памяти имеют разную организацию, для правильного конфигурирования ядра необходимо иметь представление о структуре динамической памяти. Современная динамическая память, как правило, объединяется в более крупные единицы – модули (SIMM, DIMM, SO-DIMM), которые используются в готовых изделиях как единое целое. Структура отдельной микросхемы динамической памяти приведена на рисунке 2.

Микросхемы памяти объединяются в линейки, имеющие общую адресацию. Таких линеек на модуле может быть несколько (как правило – две). Для адресации этих линеек используются дополнительные сигналы RANK. Для модулей памяти DIMM (SO-DIMM) ширина данных может составлять 64 или 72 бита. В последнем случае дополнительные биты используются как контрольные для обнаружения ошибок передачи данных.

Входящая в обозначение типа памяти цифра, например «3» для DDR-3, характеризует количество передаваемых за одну транзакцию слов данных. Такая порция данных называется бёрст (от англ. burst – всплеск, взрыв, вспышка). Эта цифра, в данном случае «3», представляет собой степень, в которую надо возвести двойку, чтобы определить длину бёрста. Таким образом, динамическая память типа DDR-3 обменивается с контроллером блоками (бёрстами) размером 23 = 8 слов. Понятно, что такой способ повышает скорость передачи данных, но при этом увеличивается задержка доступа к отдельному слову данных (латентность).

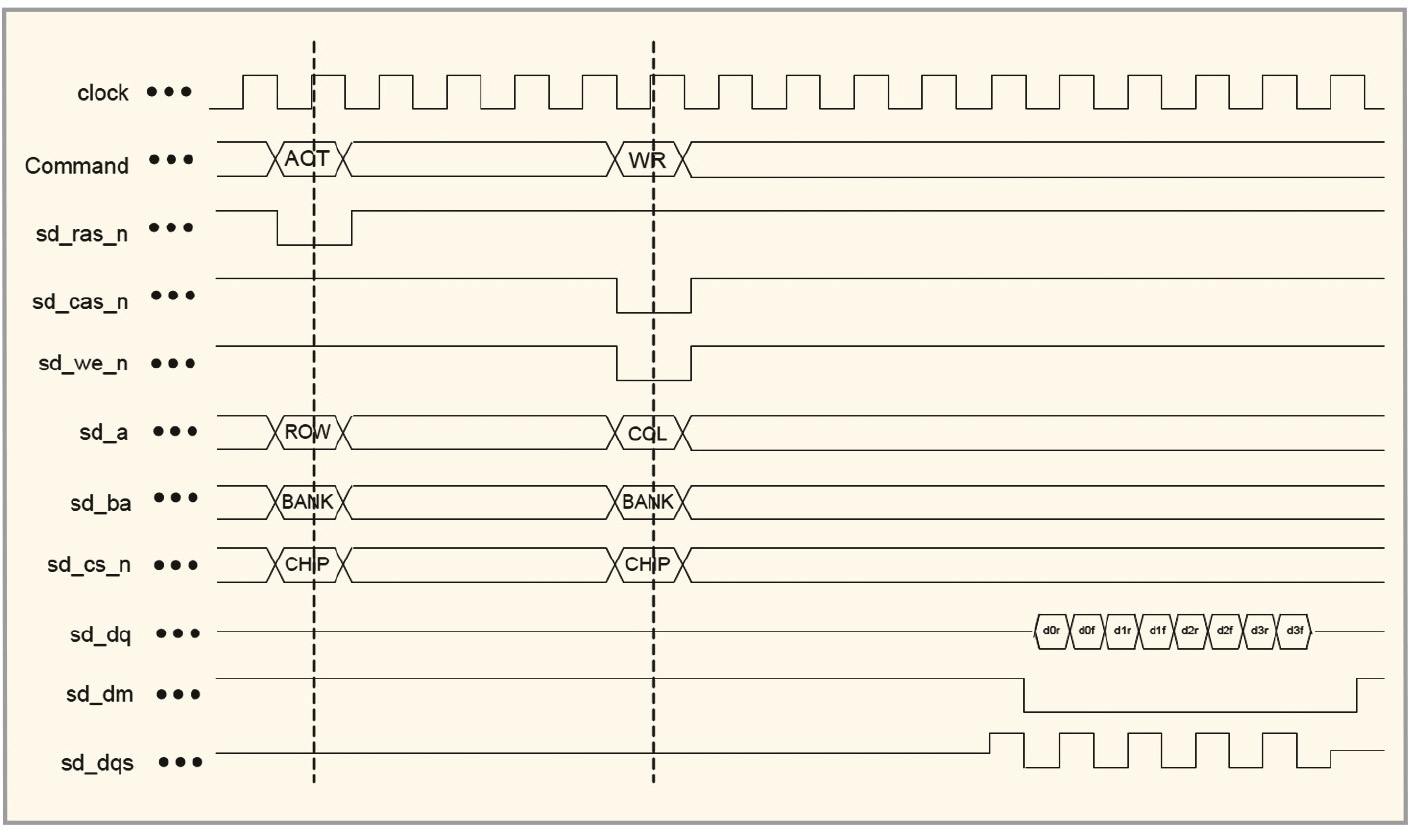

На рисунке 3 приведены временны́е диаграммы процесса записи в DDR-3 память со стороны контроллера памяти ПЛИС. На этих диаграммах видна ещё одна особенность памяти DDR: данные передаются по обоим фронтам тактового сигнала, что вдвое повышает скорость обмена.

Исходя из параметров адресации памяти, был определён максимальный объём адресуемой динамической памяти. Оказалось, что один контроллер может адресовать 233 слов данных шириной 64 бита (8 байт), а всего 236 байт, что составляет 68 719 476 736 байт данных. Всего же 6 контроллеров позволяют работать с объёмом памяти 412 316 860 416 байт, что составляет более 412 Гбайт!

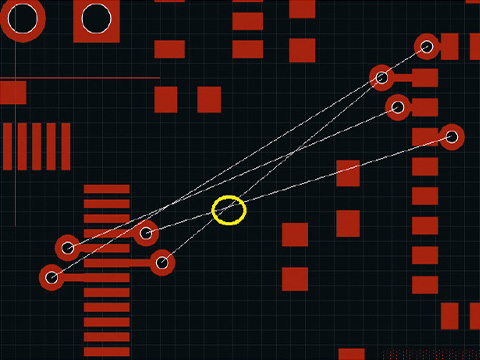

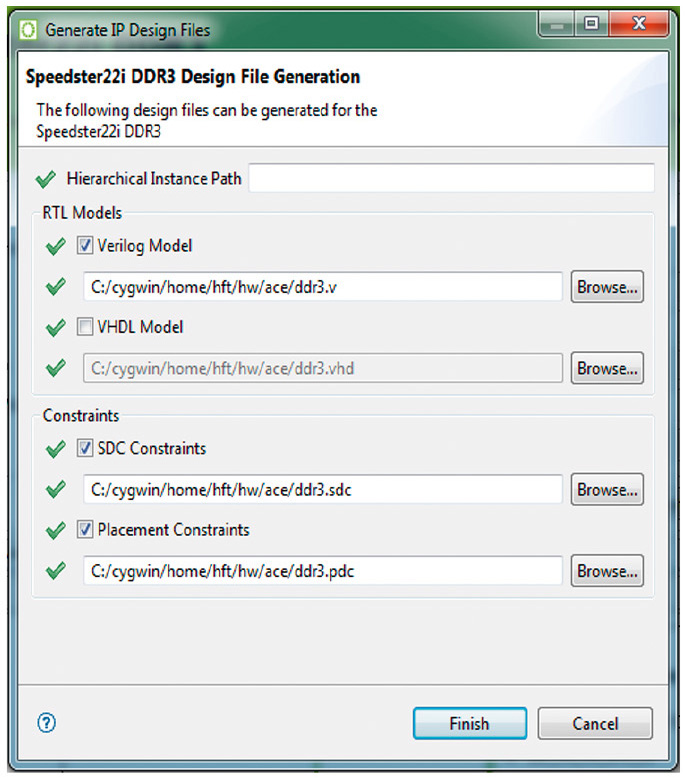

Для того чтобы использовать контроллер DDR-памяти в своих проектах, необходимо выполнить несколько несложных действий. Прежде всего, нужно сконфигурировать аппаратное ядро. Проще всего это сделать с помощью генератора ядер, входящего в состав оболочки ACE. Для модуля Micron DDR3-2GB, поставляемого в составе отладочного набора HD1000 Dev Kit, можно использовать предустановленные параметры. Максимальная скорость для модуля Micron – 1600, что соответствует внутренней частоте памяти 200 МГц и частоте шины обмена данными 800 МГц. Максимально же контроллер DDR-3 ПЛИС Speedster22i способен поддерживать модули DDR3-1866 (233/933 МГц). Модуль формата SO-DIMM подключается к плате к юго-восточному контроллеру (ES-банк). Важным параметром является Fabric_Interface_Width, который определяет тактовую частоту и ширину шины данных контроллера. Остальные параметры можно оставить по умолчанию и затем нажать кнопку «Generate» (см. рис. 4).

В результате генерируются три файла: файл модуля на языке Verilog (и/или VHDL) и два файла констрейнтов (ограничений) для размещения и синтеза (см. рис. 5).

Файл модуля на языке Verilog содержит все необходимые параметры и интерфейсные порты. Несмотря на большое количество портов, большинство из них являются опциональными и не требуют подключения.

Далее на входной порт clk необходимо подать тактовую частоту, соответствующую тактовой частоте шины передачи данных DDR-3 памяти. В частности, для памяти DDR3-1600 входная тактовая частота должна составлять 800 МГц. Эту частоту легко сгенерировать с помощью модуля DLL. Также необходимо определить частоту ddr_int_clk_sbus, которая обычно задаётся в диапазоне 16…100 МГц. Шина sbus предназначена для динамической реконфигурации контроллера и, как правило, не используется, но на неё обязательно должна быть подана тактовая частота.

С модулем интерфейса пользователя аппаратное ядро может работать в двух режимах. В режиме «1x» тактовая частота составляет clk/2, а ширина шин данных – 128 бит (144 бит для шины данных 72 бита). В режиме «2x» тактовая частота – clk/4 и ширина шин данных – 256 (288) бит. Эта тактовая частота вырабатывается в самом модуле и используется для тактирования пользовательской логики. Конкретный режим работы устанавливается параметром Fabric_Interface_Width.

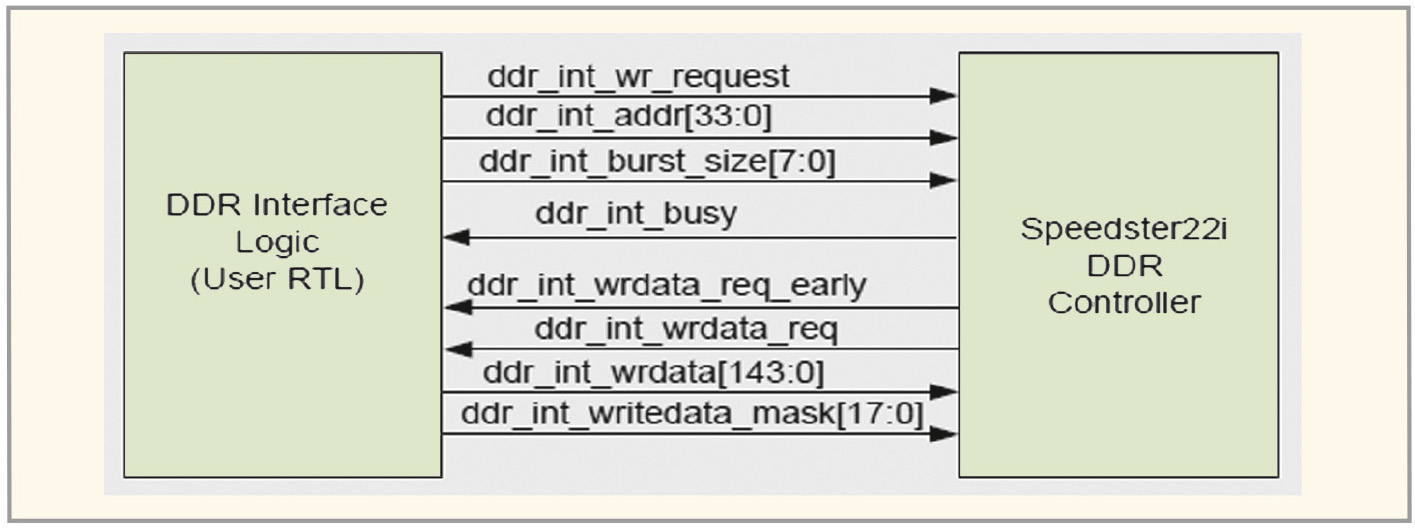

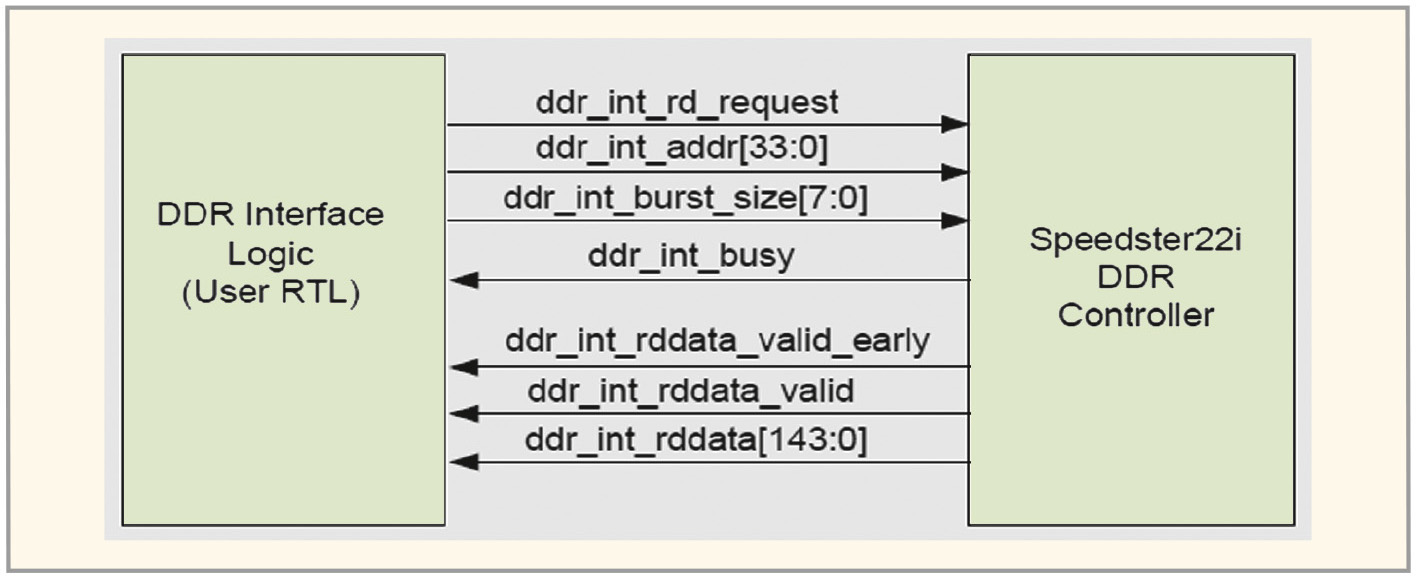

И, наконец, необходимо сопрячь остальные части проекта с контроллером DDR-3. Сделать это можно с помощью модуля DDR_interface_logic.v. Интерфейс этого модуля для записи и чтения показан на рисунках 6 и 7 соответственно.

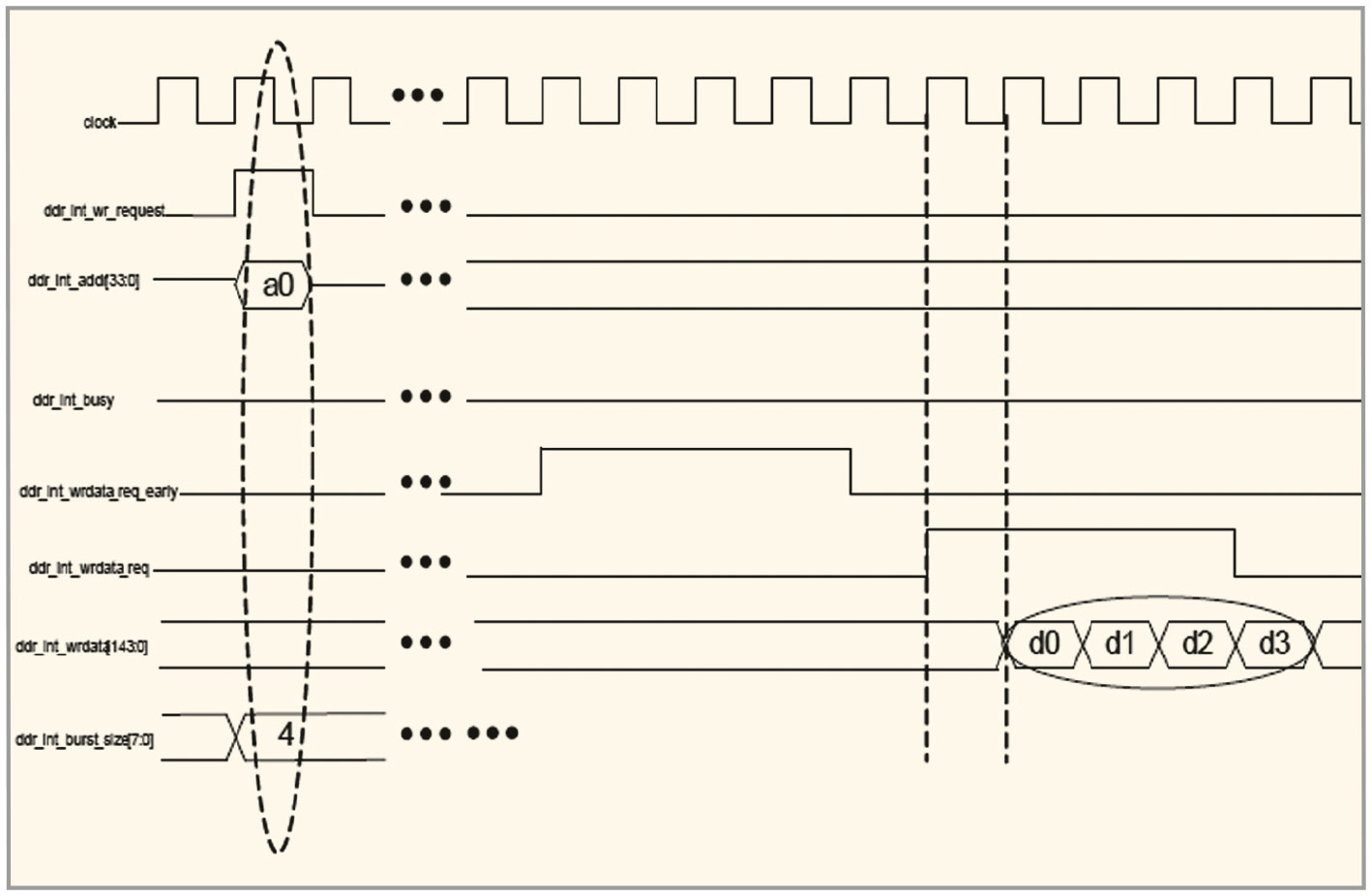

Временны́е диаграммы транзакций записи и чтения представлены на рисунках 8 и 9. В режиме «2x» временны́е диаграммы выглядят аналогично, за исключением того, что тактовая частота берётся вдвое ниже, а ширина шин данных – вдвое больше. Таким образом, за счёт вдвое меньшей тактовой частоты существенно понижаются требования к таймингу модулей пользователя. Тайминг же самого ядра оптимизирован изначально: его оптимизация не нужна и невозможна.

Из диаграмм видно, что данные передаются и принимаются бёрстами. Если, например, обмен с памятью ведётся блоками 64 бита × 8 = 512 бит, то обмен с контроллером в режиме «1x» ведётся блоками 128 бит × 4, а в режиме «2x» – 256 бит × 2, что составляет те же 512 бит.

Как правило, ширина шин данных, используемых в конкретном проекте, отличается от 512 бит, что требует применения логики преобразования данных. Такие схемы могут быть как простыми устройствами, осуществляющими преобразование адресов памяти и ширины данных по жёсткому алгоритму, так и сложными устройствами, выполняющими функции кэш-памяти. Обычно также требуется наличие схем пересинхронизации, так как тактовая частота пользовательского проекта часто отличается от тактовой частоты контроллера DDR. Однако вся эта «чёрная и белая магия» выполняется достаточно тривиально, хотя ей можно было бы посвятить отдельную статью.

Выводы

Аппаратный контроллер динамической памяти, применённый в ПЛИС Achronix, существенно упрощает работу с памятью DDR3. Он имеет простой и понятный пользовательский интерфейс и, в отличие от soft-ядер, не требует трудоёмкой оптимизации по таймингу. Широкий диапазон режимов и настроек позволяет работать с широкой номенклатурой различных БИС и модулей памяти. Кроме того, аппаратный контроллер динамической памяти может автоматически выполнять такие вспомогательные действия, как калибровка и регенерация данных.

Литература

- Документация по ПЛИС Achronix с сайта Achronix.ru. www.achronix.ru/documentation.html.

- Википедия, статья DDR3 SRAM. www.ru.wikipedia.org/wiki/DDR3_SDRAM.

- Статья по организации микросхем памяти типа DDR3. www.compress.ru/article.aspx?id=18761.

Если вам понравился материал, кликните значок — вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал —не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!