В 2007 году был выпущен стандарт DDR3, в 2012 году – DDR4, в настоящее время ожидается выход DDR5. Некоторые передовые разработчики уже вплотную подошли к созданию этой технологии, и ожидается, что JEDEC (Объединённый инженерный совет по электронным устройствам) выпустит этот стандарт в ближайшем будущем.

Преимущества DDR4 перед DDR3:

- повышенная скорость передачи данных;

- более высокая эффективность;

- улучшенная целостность данных;

- больший объём памяти.

Память DDR3 работает со скоростью 800–2133 MT/с (миллионов посылок в секунду), тогда как DDR4 – со скоростью 1600–3200 MT/с, т.е. вдвое быстрее своего предшественника. Кроме того, память DDR4 рассчитана на напряжение 1,2 В, что повышает её эффективность, продлевая время работы от батарей и снижая нагрузку по сравнению с напряжением 1,5 В, от которого питается DDR3.

Помимо этого, алгоритм нахождения контрольной суммы (CRC) и встроенный в технологию DDR4 детектор ошибок чётности улучшает целостность данных, выполняя дополнительную проверку передаваемых команд и данных. Кроме того, удельный объём памяти DDR4 был увеличен в 4 раза. Максимальный объём памяти DDR3 составляет 128 Гбит, тогда как для DDR4 эта цифра равна 512 Гбит.

Предполагается, что с появлением DDR5 скорость передачи данных и объём памяти снова удвоятся, т.е. достигнут 6 ГТ/с и 1 Тбит соответственно, а это подразумевает ещё более высокую эффективность.

Проблемы тестирования

Целостность сигнала

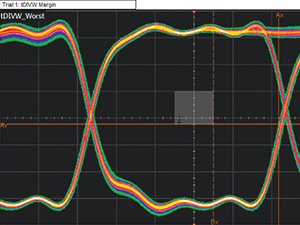

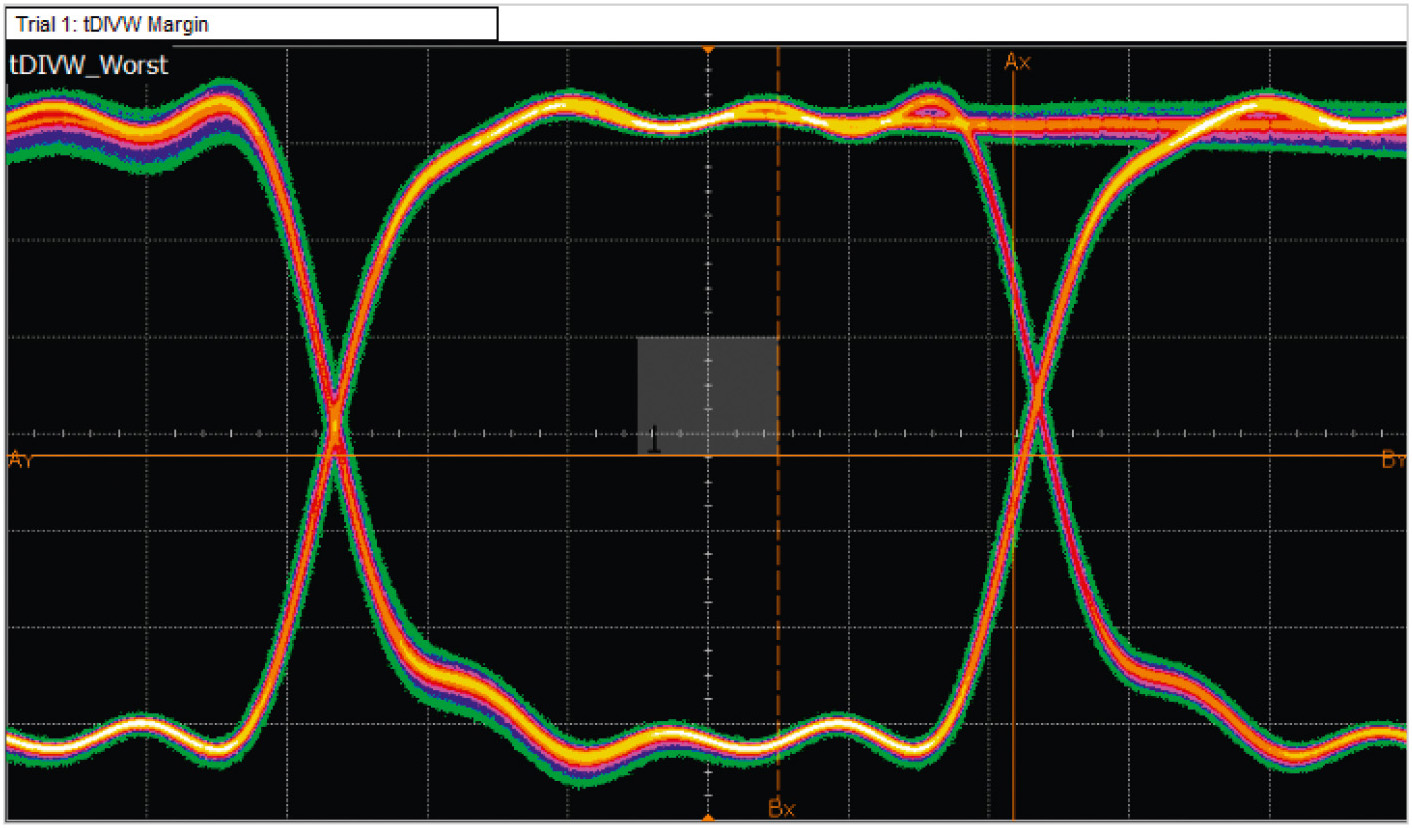

Наиболее распространёнными проблемами технологии DDR являются проблемы синхронизации контроллера памяти. Как правило, контроллер памяти покупается в уже готовом виде, а не проектируется самостоятельно. В этом случае необходимо добиться синхронной работы платы и контроллера памяти – для этого достаточно выполнить тесты времени установки и удержания и проверить скорость передачи данных. В прошлом скорости были ниже, поэтому конструктивные запасы были шире, и, если тесты времени установки и удержания проходили успешно, можно было с большой уверенностью утверждать, что система памяти DDR2 или DDR3 отвечает требованиям спецификаций. Однако с ростом скорости передачи конструктивные запасы сужаются. Работая с DDR4 или DDR5, получить достаточные конструктивные запасы для прохождения простых тестов времени установки и удержания практически невозможно. Для проверки DDR4 нужно использовать глазковую диаграмму.

Стандарт DDR4 предъявляет особые требования к допускам на случайный джиттер и коэффициент битовых ошибок. Можно создать маску для осциллографа согласно этому стандарту (см. рис.). Маска определяет область на экране осциллографа, в которой должен оставаться сигнал, чтобы отвечать требованиям стандарта. Если глазок закрывается слишком сильно и пересекает маску, то, скорее всего, это значит, что возникли битовые ошибки и требования спецификаций не выполняются.

Можно предположить, что глазок DDR5 будет закрываться из-за повышенной скорости передачи данных. В таких случаях для достаточного раскрытия глазка нужно применять методы эквализации. Кроме того, характеристики DDR5 определяются на шариковых выводах корпуса, однако установить пробник внутрь микросхемы не получится. Вместо этого придётся исследовать сигнал канала, но это не позволит понять, открыт или закрыт глазок во внутренних цепях микросхемы, поэтому для устранения влияния импульсной характеристики канала нужно применять эквалайзер с решающей обратной связью.

Повреждение данных

В процессе проверки DDR4, LPDDR4, DDR5 или LPDDR5 зачастую выявляется повреждение данных. Оно может происходить по разным причинам: либо из-за нарушения целостности сигнала, либо из-за функциональных проблем. Для проверки целостности сигнала (включая размер глазка, время перепадов и качество питающих напряжений) можно использовать осциллографы, а для проверки функциональности и соответствия протоколов систем памяти – логические анализаторы. Функциональные проблемы, когда память не получает корректные команды в нужной последовательности или в нужное время, могут привести к повреждению данных и вызвать системные сбои. Для выявления таких ошибок и их причин важную роль играют физические и функциональные тесты, которые позволяют отладить схему и предотвратить отказы.

Контрольно-измерительное оборудование для испытаний модулей памяти

Для упрощения тестирования и отладки можно применить программное обеспечение, выполняющее проверку на соответствие требованиям стандарта. Такое ПО работает прямо на осциллографе и помогает проверять целостность сигнала и физический уровень проектируемого устройства. Оно автоматизирует проверку соответствия, тестирует устройство и генерирует отчёт типа «годен / не годен» – нужно лишь подать сигналы на осциллограф и запустить приложение.

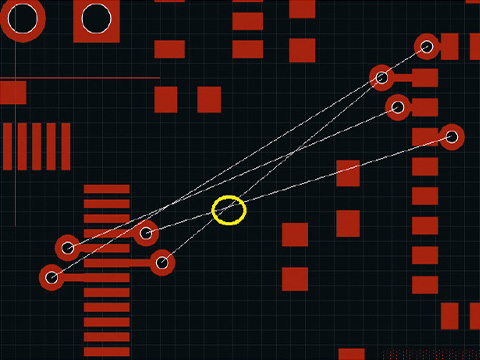

Для проверки функциональности или соответствия протокола можно захватить все сигналы DDR подходящим логическим анализатором (более 100 сигналов в схемах DIMM/SODIMM) со скоростью 4200 МТ/с и с глубиной захвата до 400 Мвыб/сигнал.

Приложение для анализа декодирует транзакции протокола и предлагает разные режимы представления трафика во всех точках системы. Эти отчёты и диаграммы помогают инженерам быстро исследовать поток трафика и выявлять проблемные области. ПО для проверки на соответствие протокола требованиям стандарта выявляет точную причину возникновения проблем в системах памяти.

Заключение

DDR – это технология изготовления микросхем памяти, которая за последние 10 лет включила в себя 2 поколения. В настоящее время ведётся разработка следующего поколения этой памяти. Каждое из них предлагало повышенные скорость, эффективность и объём памяти, но по мере того как стандарт позволял передавать всё бо¢льшие объёмы данных на более высоких скоростях, конструктивные запасы сокращались и, соответственно, усложнялись разработка и тестирование. Осциллографы и ПО для проверки на соответствие требованиям стандарта могут облегчить решение некоторых проблем на физическом уровне, а логические анализаторы позволяют тестировать и отлаживать системы на функциональном уровне или на уровне протокола.

Если вам понравился материал, кликните значок — вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал —не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!