Компания Cadence Design Systems в 2018 году активно расширяет функцио-нальные возможности своей линейки САПР печатных плат OrCAD/Allegro/SiP. Линейка продуктов начинается с недорогой базовой конфигурации OrCAD, которой пользуются небольшие частные компании, и заканчивается флагманским продуктом Allegro Venture PCB Editor, предназначенным для крупных предприятий. Кроме развития функциональности инструментов, можно отметить и усовершенствование графического интерфейса пользователя, повышение удобства работы схемного редактора и редактора печатных плат.

Каждые три месяца компания Cadence выпускает очередной квартальный релиз, в котором собраны интересные новые функции и обновления. Заметна тенденция по переносу части мощных функций из старших продуктов Allegro в более младшие версии: OrCAD Professional и OrCAD Standard. Например, в базовую версию OrCAD Standard включены следующие функции:

- новый 3D-редактор с возможностью проектирования гибко-жёстких плат;

- работа с дифференциальными парами с анализом статической фазы;

- проверки технологичности проекта (DFM).

Всё это делает САПР OrCAD полноценным современным инструментом, в котором реализованы все этапы проектирования – от разработки схемы до подготовки производственных файлов.

Рассмотрим, что предлагает компания Cadence в релизе QIR6, который вышел в апреле 2018 года, и какие пре-имущества эти новые возможности дают пользователям. Изменения коснулись следующих программ:

- менеджер загрузки обновлений ПО;

- редактор плат Allegro и OrCAD PCB Editor;

- схемный редактор OrCAD Capture.

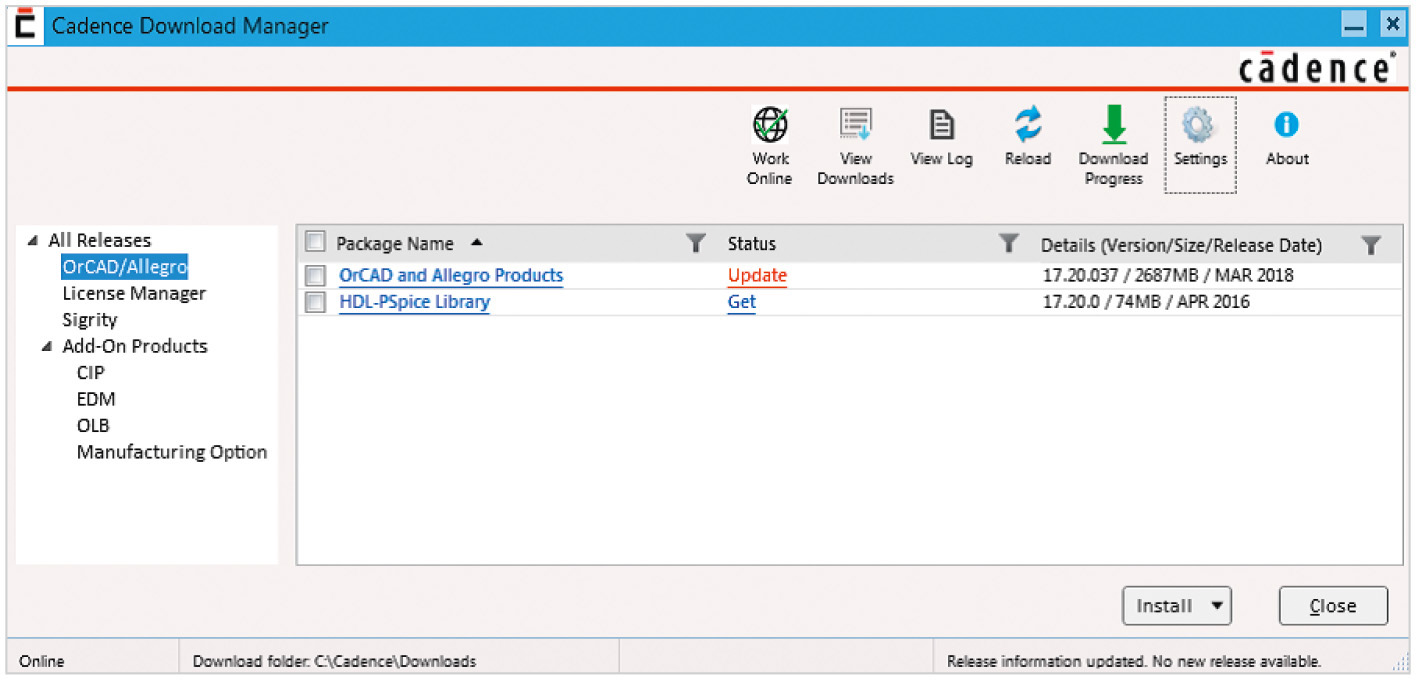

Менеджер загрузки обновлений ПО

Данная программа помогает загружать, устанавливать и обновлять различные инструменты САПР Cadence, выбирая их из списка (левое окно на рисунке 1) и отмечая требуемые продукты и дополнения к ним в окне справа.

В колонке Status можно увидеть, появились ли обновления или установлена последняя версия продукта.

Редактор печатных плат Allegro и OrCAD PCB Editor

В редакторе печатных плат появились следующие изменения:

- правила проектирования для производства (DFM и DFA);

- новые возможности 3D-редактора;

- улучшения в работе со STEP-моделями для 3D-редактора;

- улучшения в анализе высокоскоростных сигналов на базе Sigrity;

- улучшения в анализе DRC-пути возвратного тока;

- новая версия утилиты Allegro ECAD-MCAD Library Creator;

- повышение общей производительности;

- повышение качества и производительности в работе с полигонами;

- новые возможности совместной работы в Allegro PCB Symphony Team Design;

- обновление инструментов Produc-tivity Toolbox;

- улучшенные инструменты СВЧ-проектирования RF PCB и RF SiP.

Рассмотрим эти усовершенствования подробнее.

Правила проектирования для производства (DFM)

В редактор OrCAD PCB Editor 17.2 добавлены новые правила проверок для обеспечения качества производства печатной платы – Design for Manufacturing (DFM). Они располагаются во вкладке Manufacturing менеджера ограничений. Эти правила работают на уровне выходных производственных файлов (фактически Gerber-файлов), поэтому их можно применять для контроля готового проекта печатной платы, анализируя его с точки зрения технологичности производства плат, повышения выхода годных изделий, сокращения сроков и стоимости изготовления как образцов, так и серий печатных плат. В правила входят следующие 5 групп проверок:

- Проверка отступов от разных объектов до края платы или до выреза в плате.

- Анализ наличия островков маски или узких оборванных сегментов маски.

- Анализ гарантийного пояска от отверстия до площадки и от площадки до маски.

- Анализ зазоров в медном рисунке и расстояний до неметаллизированных отверстий.

- Анализ маркировки на площадках, переходных и крепёжных отверстиях.

Применение этих правил позволяет ещё до запуска плат в производство обнаружить нетехнологичные места и ошибки в проектах и тем самым сократить сроки разработки плат за счёт исключения возврата нетехнологичных проектов с производства.

В релизе QIR6-2018 в этот раздел добавлена возможность исключать некоторые компоненты из проверок по отступу от контура. Например, если необходимо установить на край платы торцевые разъёмы, то это нарушает правила DRC по расстоянию от компонента или вывода до края платы. Проверка DRC в этом случае создаёт множество маркеров, которые приходится «закрывать» вручную, что неудобно. Чтобы исключить такую проверку для подобных особых компонентов, теперь можно поместить их в специальный класс DFA_DEV_CLASS. Имя компонента должно начинаться с префикса FCON_, EMNT_ или MECH_ (для механических компонентов). В этом случае для данных компонентов проверка DRC на выход за границу платы не проводится, и пользователь может разместить их близко к краю.

Новые правила проверок качества монтажа Design for Assembly (DFA)

В PCB Editor версии 17.2 также были добавлены новые правила проверок для обеспечения качества монтажа – Design for Assembly (DFA). Они располагаются также во вкладке Manufacturing менеджера ограничений. Удобство этих проверок состоит в том, что они позволяют верифицировать проект с точки зрения возможности его сборки на автоматизированном монтажном оборудовании, оснащённом конвейерами и роботами. При проверках учитываются все процессы – от нанесения паяльной пасты через трафарет до установки планарных компонентов и оплавления в печи. При этом во внимание принимаются, например, такие важные нюансы, как утечка паяльной пасты через переходные отверстия при оплавлении или вытекание припоя из переходного отверстия с формированием пузырей, что может помешать качественной установке компонентов на этапе поверхностного монтажа второй стороны платы. Данные проверки подразделяются на 3 группы:

- Отступ от контура платы для компонентов и для участков припойной пасты.

- Правила минимальных зазоров:

• от тела компонента до механических отверстий;

• от тела компонента до выводов соседних компонентов;

• между участками с припойной пастой;

• между припойной пастой и ближайшими переходными отверстиями. - Наличие припойной пасты на каждой планарной площадке, поясок площадки относительно паяльной пасты, отступ маски относительно паяльной пасты.

Таким образом, в новой версии OrCAD 17.2 появилось множество полезных проверок, которые обеспечат производству гарантированное качество и отсутствие проблем с монтажом.

Дополнительные проверки в Allegro Venture

В корпоративной версии САПР Allegro Venture появились уникальные дополнительные технологические проверки DesignTrue DFM. Это отступы от контура для монтажа, зазоры между различными объектами, тентирование переходных отверстий, проверка вырезов в полигонах, смещение микроотверстий и проверка наличия локальных реперных точек.

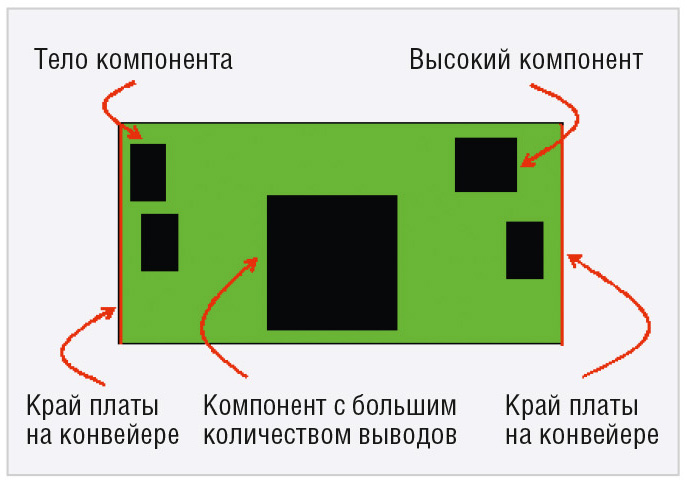

Отступы от контура. Если планируется автоматизированный монтаж печатных плат, то разработчику необходимо учитывать особенности данного процесса, в частности то, как плата будет располагаться на конвейере при нанесении паяльной пасты, установке компонентов и оплавлении в печи. Необязательно делать дополнительные поля с перемычками, если есть возможность использовать для этой цели края платы, но при этом необходимо освободить их от компонентов.

В Allegro можно указать те края платы, которые будут опираться на конвейер при поверхностном монтаже, то есть поля для монтажа, и задать для них специальные правила, регулирующие расстояние от компонентов. Кроме того, компоненты с большим количеством выводов и компоненты большой высоты могут быть автоматически выделены в отдельную группу с особыми правилами по отступу от «конвейерных» полей (см. рис. 2).

Зазоры между объектами. Переходные отверстия большого диаметра, расположенные под компонентом, могут служить источником проблем при монтаже, т.к. из них при оплавлении может вытечь и застыть пузырь припоя, который не даст качественно установить компонент с обратной стороны. В Allegro такие участки можно автоматически обнаруживать и отмечать флагами DRC.

Если говорить о компонентах небольшого размера, то во избежание сложностей при монтаже под ними нежелательно размещать ни переходные отверстия, ни проводники. Такие компоненты в Allegro можно поместить в отдельный список в разделе правил DFA Spacing Rules, чтобы, в случае если под ними оказались расположены проводники или отверстия, сообщить об этом разработчику. Также в новой системе Allegro Venture можно проверять:

- зазор от меди до реперных точек в слое;

- зазоры между участками паяльной пасты;

- зазоры от участков паяльной пасты до ближайших переходных отверстий (для предотвращения утечки припоя в отверстия при оплавлении).

Такие уникальные технологические проверки позволяют командам разработчиков предусмотреть и предотвратить сложности при монтаже и обеспечить высокое качество проектов, даже если некоторые проекты выполняются неопытными молодыми специалистами, сторонними компаниями или даже фрилансерами.

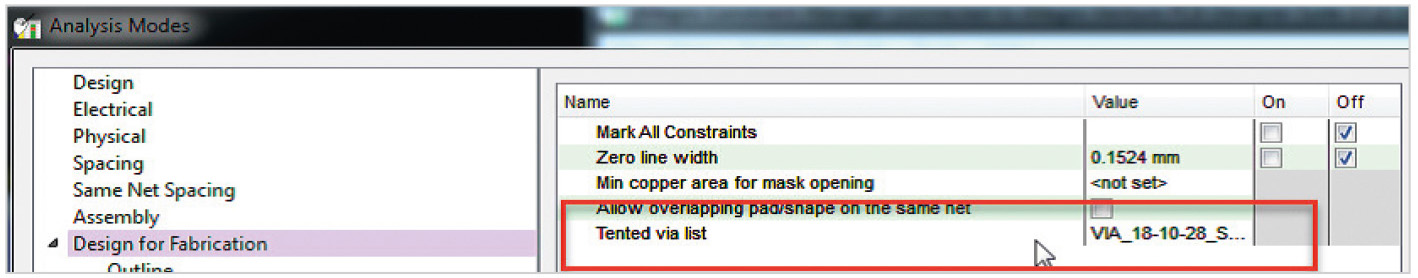

Тентирование переходных отверстий. В настоящее время всё более часто используемой технологией становится тентирование некоторых переходных отверстий, то есть полное закрытие их маской с предварительным заполнением отверстия смолой. Особенно полезно это делать в зоне BGA-компонентов. При этом зачастую в проекте могут присутствовать как тентированные, так и нетентированные отверстия, в зависимости от их диаметра или зоны расположения на плате.

В Allegro площадки и переходные отверстия автоматически могут быть проверены на отсутствие вскрытий маски. При этом можно исключить определённые типы отверстий из проверки, задав список падстеков, про которые известно, что они будут тентированы, то есть полностью закрыты маской. Этот раздел проверок (Tented via list) доступен в разделе Design for fabrication диалога Analysis Modes (см. рис. 3).

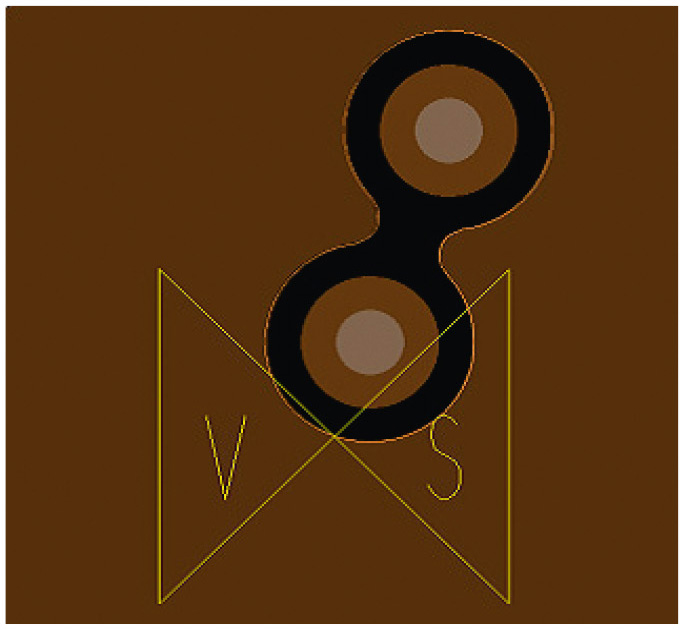

Проверка вырезов/отступов в полигонах. При автоматическом создании отступов от отверстий в полигонах могут образовываться протяжённые участки cо слишком узкими зазорами, наличие которых потенциально может привести к замыканию меди или материала покрытия платы. В таких случаях могут возникать производственные проблемы, в том числе при монтаже, даже если это зазор между участками одной и той же цепи. Рекомендуется не допускать слишком протяжённых узких зазоров, чтобы снизить вероятность замыкания.

Allegro Venture позволяет проверить минимальные расстояния между краями вырезов, чтобы обнаружить вероятность образования замыканий. На рисунке 4 показан пример такой ошибки (DRC void sliver) между переходным отверстием и полигоном.

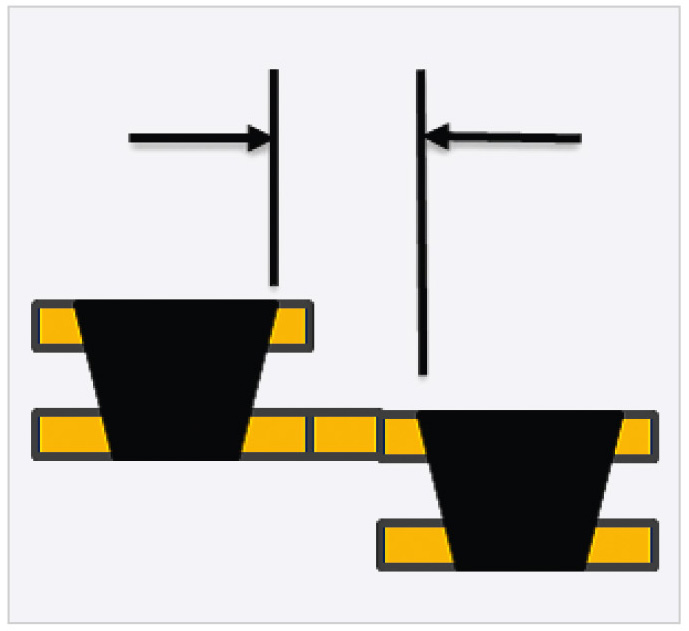

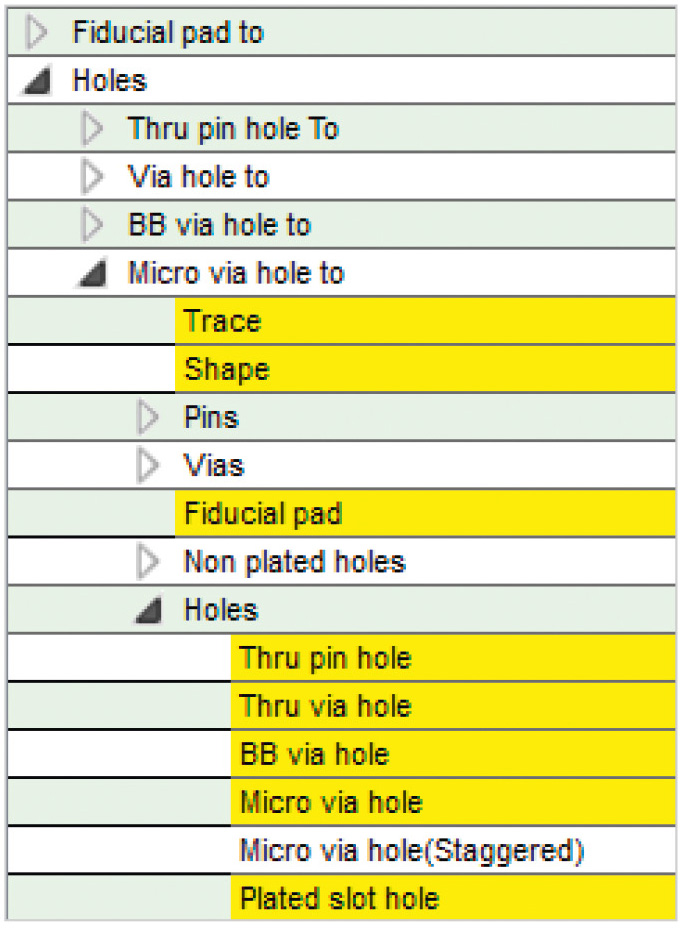

Смещение микроотверстий. При использовании микроотверстий в структурах HDI или похожих технологиях используются лазерные отверстия конической геометрии. В проектах большой плотности эта геометрическая структура позволяет уменьшить расстояние между микроотверстиями, если они принадлежат одной и той же цепи. Если микроотверстие переходит со слоя 1 на слой 2 и соединено с другим микроотверстием, переходящим со слоя 2 на слой 3, то минимальное расстояние между ними может быть меньше, чем для двух микроотверстий разных цепей (см. рис. 5).

Минимальный зазор в такой ситуации задаётся в менеджере ограничений Allegro отдельно, в категории Design for fabrication секции Copper spacing/Micro via hole (Staggered), как показано на рисунке 6. Использование ступенчатых микроотверстий в Allegro в сочетании с применением этого уникального параметра позволяет эффективно трассировать печатные платы, содержащие BGA-компоненты с шагом 0,5; 0,4 и даже 0,35 мм.

Проверки наличия реперных точек. Для возможности выполнения качественного монтажа плат со сложными компонентами с малым шагом и большим количеством выводов очень важно обеспечить наличие локальных реперных точек недалеко от этих компонентов. Это особенно принципиально, если плата имеет большие габариты.

В Allegro проверка наличия реперных точек проводится на основе списка футпринтов компонентов. Каждый тип компонента определяет минимальное количество реперных точек, допустимое для его качественного монтажа. Это позволяет гарантировать наличие требуемого количества реперных точек для сложных в монтаже компонентов, таких как BGA с большим количеством выводов, микро-QFN или CQFP с малым шагом.

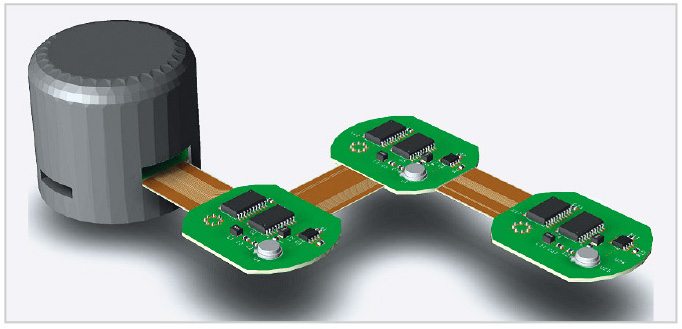

Новые возможности 3D-редактора

В релизе OrCAD 17.2 QIR6 новый редактор трёхмерного вида печатной платы уже не требует включения через настройки, а включён по умолчанию.

В обновлённом редакторе реализованы 3 основные новые возможности:

- Отображение теней при визуализации платы.

- Центрирование при перегибе гибких частей.

- Дополнительные опции представления моделей компонентов на экране.

Как видно из рисунка 7, модели компонентов на плате и сама плата теперь выглядят более реалистично за счёт отображения теней.

Функция центрирования автоматически меняет расположение платы на экране при перегибе шлейфов. Представление компонентов теперь предлагает две дополнительные опции: показывать в первую очередь STEP-модель, а если её нет, то «условный кубик»; или показывать преимущественно «условный кубик», а если его нельзя отобразить, то STEP-модель. Также в релизе QIR6 добавлены следующие возможности редактора:

- команда «Отменить привязку STEP-моделей» для всех компонентов;

- возможность экспортировать STEP-модель печатной платы без подключённых STEP-моделей компонентов;

- возможность обновлять компоненты, подгружая обновлённые STEP-модели.

Улучшения в анализе высокоскоростных сигналов на базе Sigrity

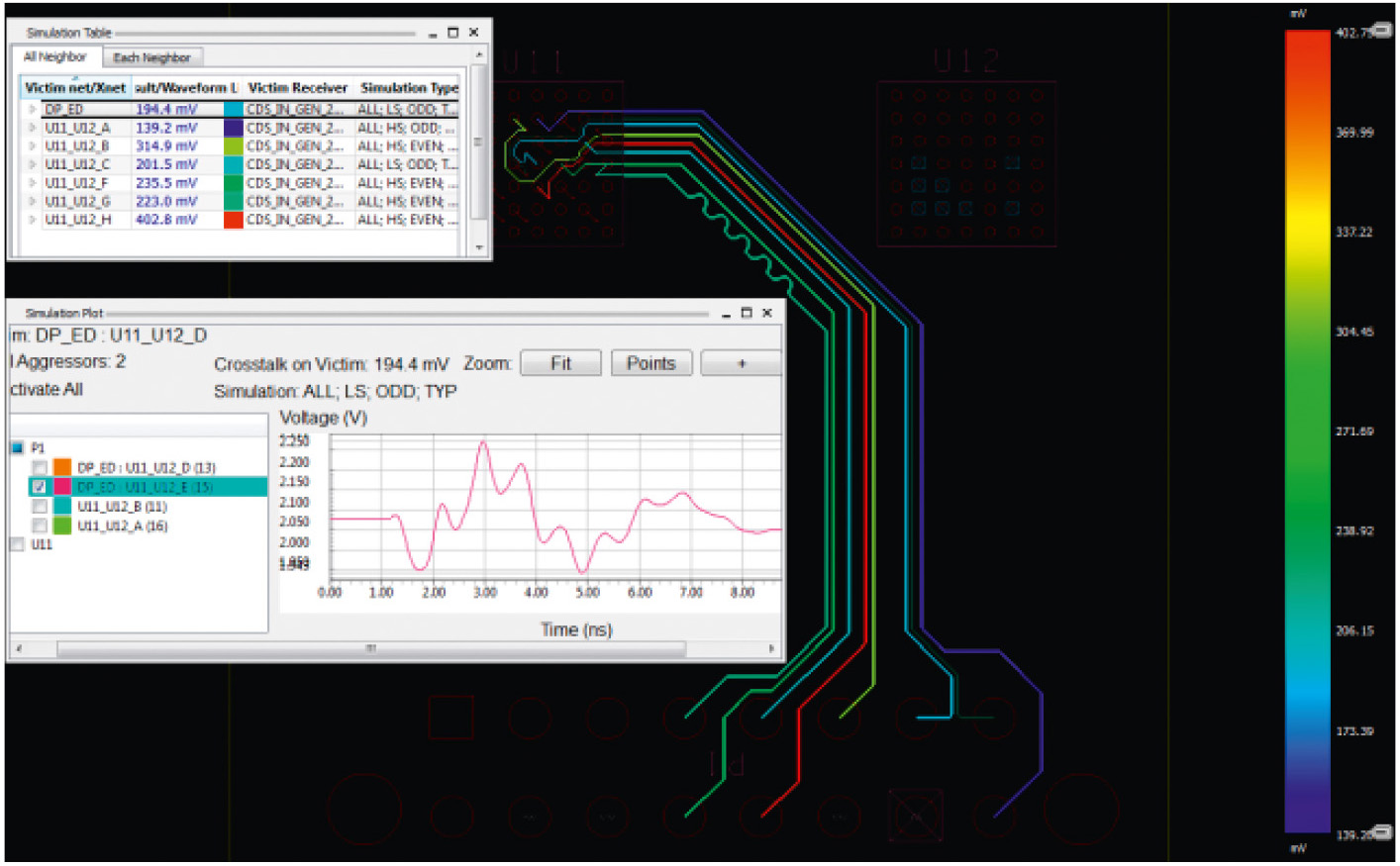

Уникальная возможность анализа и проверки целостности сигналов в Allegro, реализованная на базе системы Sigrity, появилась в релизе 17.2 QIR4. Эта технология позволяет проводить проверки SI/PI прямо в окне редактора печатной платы. Для задания и проверки правил необходимые константы устанавливаются, как обычно, в менеджере ограничений. Система предоставляет пользователю настроенный маршрут для детального анализа топологии платы. В релизе QIR6 эта функция была усилена: появился маршрут проектирования с анализом перекрёстных помех и путей возвратного тока, а также новые продвинутые электрические проверки (ERC – Electrical Rules Check). Данная функция доступна пользователям, имеющим лицензию Sigrity SI Base. Ранее эта лицензия называлась Allegro SI XL или SigXplorer. Пользователи таких лицензий могут бесплатно перейти на Sigrity SI Base и в дальнейшем оплачивать только обновления.

Новые маршруты анализа топологии. В двух новых маршрутах анализа можно запускать моделирование или загружать для просмотра предыдущие результаты. Результаты анализа визуализируются в виде таблицы с цветными столбцами и строками, а для выбранной строки можно просмотреть детальную расшифровку результатов анализа. В графическом окне редактора Allegro PCB Editor пользователь видит подсвеченные соответствующими цветами сигналы (см. рис. 8).

Анализ перекрёстных помех (Crosstalk Analysis). Возможность просмотреть перекрёстные помехи визуально с помощью цветовой индикации прямо в окне редактора печатных плат Allegro – это ключ к значительному повышению качества проектов с точки зрения целостности сигналов на высокоскоростных печатных платах. Разработчик сразу может увидеть степень взаимного влияния цепей-агрессоров и критических цепей и эффективно устранить проблемные места в трассировке.

Для запуска анализа перекрёстных помех следует настроить модели компонентов и указать моделируемые цепи. Для назначения моделей можно использовать Analysis Model Manager (AMM). Также можно напрямую подключать IBIS-модели, в том числе из стандартной библиотеки Cadence Allegro. Затем нужно указать окно анализа GeoWindow и минимальную величину взаимодействия (например, 1%) для исключения из рассмотрения несущественных наводок. Можно использовать как вариант анализа «Все соседние сигналы вместе», так и «Каждый соседний сигнал отдельно». В анализе «Все соседи» (All Neighbors) наихудшая наводка определяется удержанием каждого сигнала-жертвы либо в высоком, либо в низком состоянии при переключении агрессоров в верхнее и нижнее состояние. Анализ «Каждый сосед» (Each Neighbor) использует результаты анализа All Neighbors для поиска наихудших агрессоров, основываясь на величине наводки в процентах, заданной пользователем. Помимо табличного представления результатов, они отображаются в виде сегментов трасс на экране редактора с цветовой кодировкой цепей.

Анализ путей возвратного тока (Return Path Analysis). Наиболее частая проблема скоростных плат – это нарушение целостности сигналов по причине некорректных возвратных путей по полигонам земли и питания. Это важно для таких скоростных цепей, как Ethernet, PCI-Express, USB и др. С целью обнаружения и просмотра сигналов, для которых высок риск данного нарушения, в Allegro используется анализ путей возвратного тока.

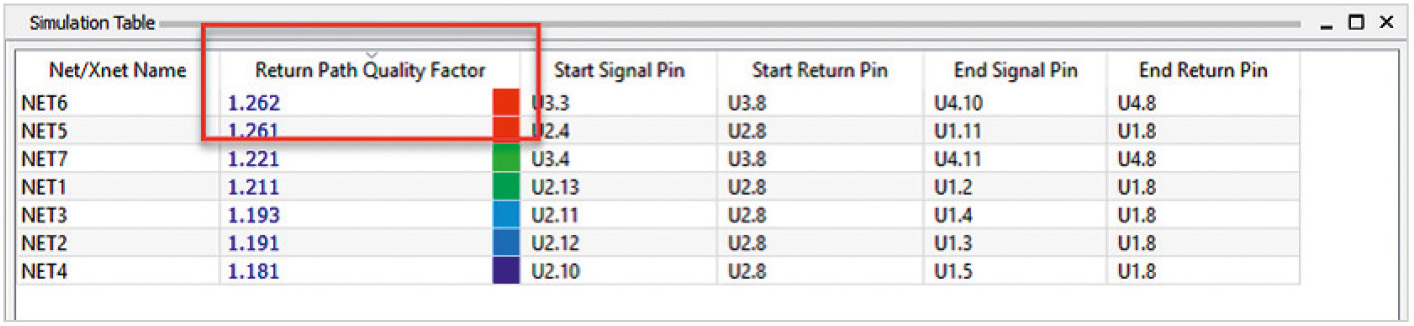

Для запуска анализа необходимо задать опорную цепь и требуемый набор сигнальных цепей Directed Group, которые соединяют компонент-источник и один или более компонент-приёмник. Результаты анализа представляются в таблице Simulation Table (см. рис. 9), где показано вычисленное системой значение фактора качества возвратного пути для каждой указанной цепи.

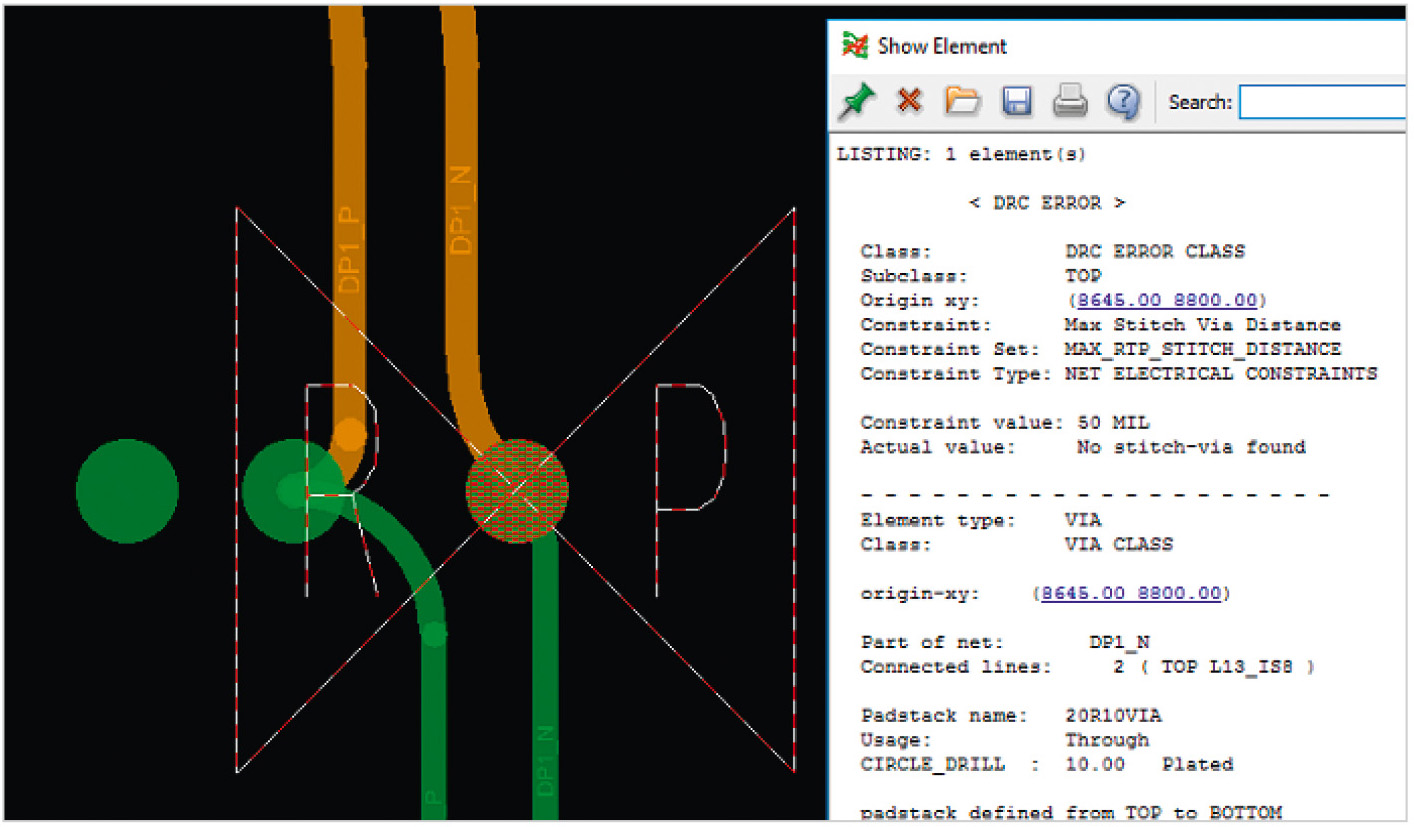

Анализ путей возвратного тока с помощью DRC-проверок. Обеспечить корректный путь возвратного тока можно с помощью аккуратной трассировки цепей над земляными опорными слоями. Однако при переходе сигнала со слоя на слой необходимо убедиться, что и возвратный ток имеет возможность перейти со слоя на слой, не образуя слишком больших токовых петель. Это можно делать вручную, но для современных сложных плат такая проверка может занять много времени и не гарантирует стопроцентного результата. САПР OrCAD с опцией OrCAD Sigrity ERC позволяет автоматически проанализировать как наличие сплошных опорных полигонов под критическими сигналами, так и расстояние до ближайших переходных отверстий, «сшивающих» полигоны в местах, где сигнал переходит на другой слой. В релизе QIR6 появилась возможность проверки расстояния от перехода сигнала или дифференциальной пары до ближайшего земляного отверстия (Stitching Via). В случае нарушения этого правила в менеджере ограничений и на экране выставляется флаг ошибки DRC, что позволяет разработчикам вовремя обнаружить те места, где возможно нарушение целостности сигналов (см. рис. 10).

Повышение качества и производительности при работе с полигонами

Системы OrCAD и Allegro весьма неплохо отрабатывают большое количество полигонов при визуализации, динамическом обновлении, перемещении компонентов и трассировке, однако современные проекты становятся всё более сложными, количество слоёв и полигонов растёт, что требует повышения эффективности САПР при их отображении и модификации.

В релизе OrCAD QIR6 добавлен режим Fast для ускоренной обработки вырезов в полигонах, за счёт чего существенно поднялась производительность при выполнении операций, затрагивающих динамические полигоны, например при перемещении проводников, отверстий, трассировке и прошивке полигонов массивами отверстий.

Повышение производительности разработчиков при трассировке

Разработчики печатных плат, использующие Allegro, получили множество других улучшений, позволяющих быстрее и эффективнее трассировать платы. Рассмотрим некоторые из них.

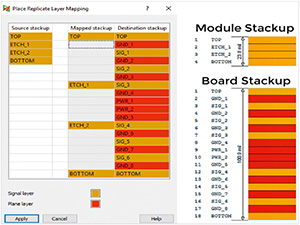

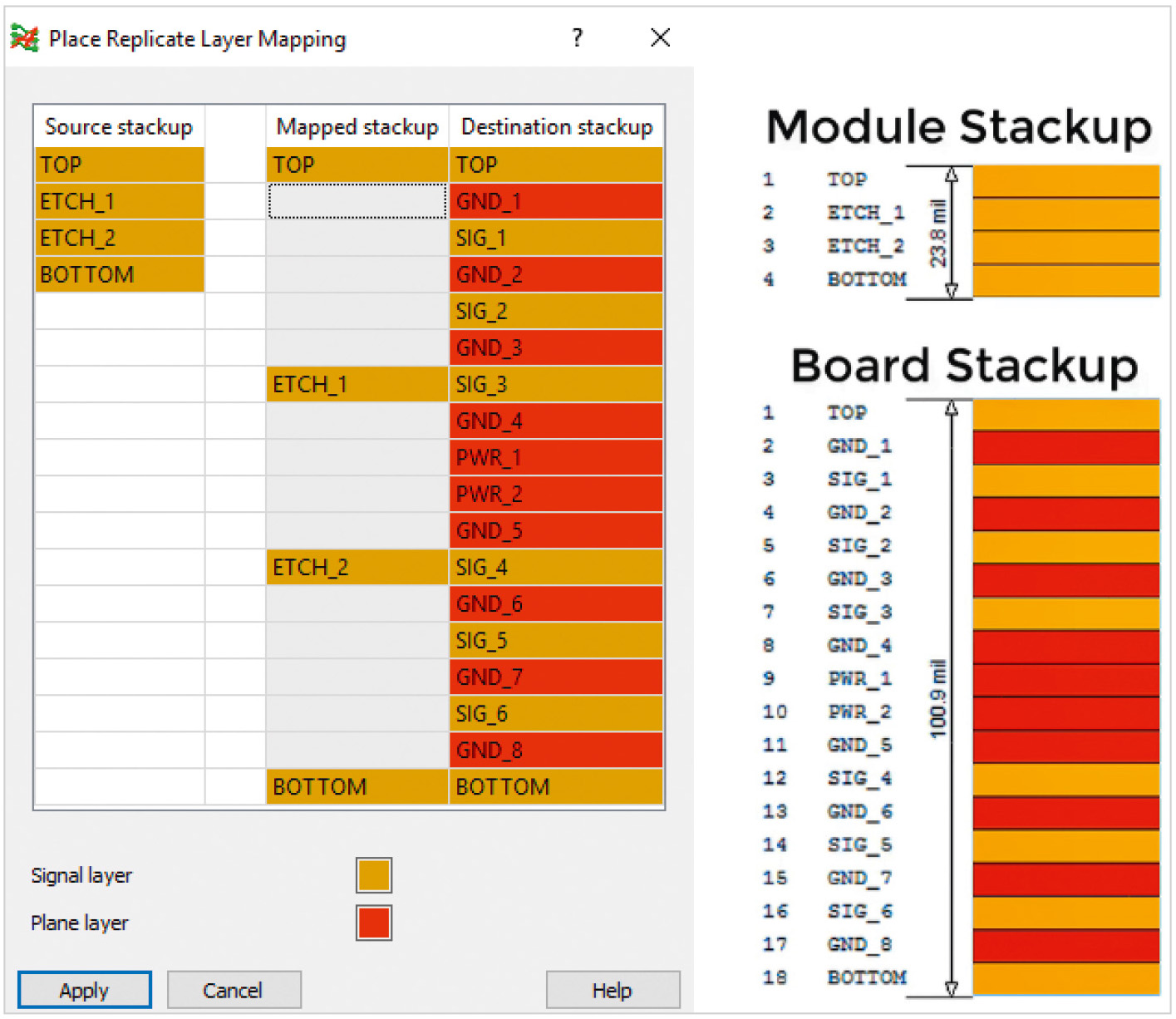

Функция размещения библиотечных модулей и размножения готовых фрагментов трассировки в PCB Editor теперь позволяет использовать заранее подготовленные библиотечные модули для печатных плат с любым стеком слоёв. Если стек слоёв библиотечного модуля не совпадает со стеком платы, на которую он ставится, возникает окно отображения слоёв, в котором можно указать соответствующие слои платы (см. рис. 11). В библиотечном модуле могут содержаться как компоненты и фрагменты трассировки, так и другие виды объектов, например зоны вырезов, регионы, тексты и линии маркировки.

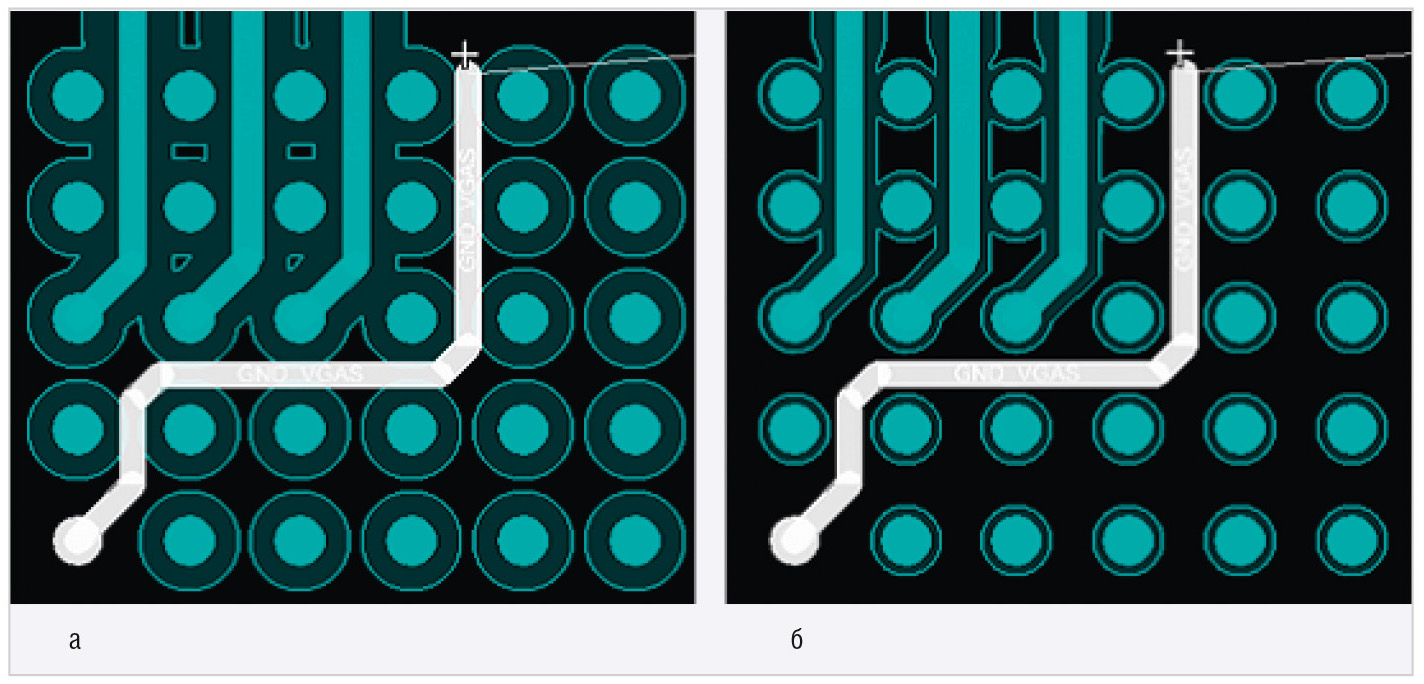

В возможности команды трассировки добавлена новая опция Clearance, которая позволяет увидеть каналы для возможной трассировки сигналов (см. рис. 12). Имеется переключение между режимами «Доступные каналы» и «Зазоры».

Копирование полигонов с помощью Copy/Paste теперь поддерживает возможность либо оставить исходную цепь при копировании, либо назначить цепь объекта при копировании полигона на некий объект платы.

Добавлена возможность экспорта топологии в PDF-формат. Если в установленной системе нет подключённой опции Allegro PDF Publisher, то печать в PDF производится в виде простого чертежа, без иерархии. При наличии PDF Publisher печать производится в интеллектуальный PDF-формат, в котором присутствует вся информация о проекте, включая иерархию компонентов, цепей и удобный поиск.

Возможность иметь несколько зон с разным стеком слоёв теперь стала более мощной. Редактирование стека такой зоны возможно, даже если в ней уже установлены компоненты или имеются переходные отверстия.

Новые возможности совместной работы (Allegro PCB Symphony Team Design)

Возможности командной работы позволяют нескольким разработчикам одновременно подключиться к проекту и заниматься его трассировкой. При этом каждый из них видит изменения, сделанные другими, без необходимости разделения проекта на зоны. Временного отключения подсоединённых разработчиков требуют только некоторые операции, такие как импорт нового нетлиста.

В релизе QIR6 опция командной работы позволяет выполнять копирование полигонов на другие слои (Z-Copy), 3D-визуализацию проекта, а также отслеживание работ, выполняемых в данный момент конкретным разработчиком, с помощью цветовой индикации курсоров и центровки экрана редактора в соответствующую область.

Обновление инструментов Productivity Toolbox

Набор инструментов Productivity Toolbox содержит дополнительные функции, которые позволяют выполнять различные нестандартные задачи, такие как генерирование штрих-кода, полярная сетка и др. Теперь в этот набор добавлена утилита для проверки правил размещения тестовых точек в зависимости от их размера и расстояния до компонентов.

Улучшенные инструменты СВЧ-проектирования RF PCB и RF SiP

Данные инструменты позволяют разработчикам СВЧ-плат и подложек микросхем эффективно размещать на плате и редактировать микрополосковые линии, а также различные СВЧ-топологии с возможностью их параметризации (например фильтры, сплиттеры, антенны и др.). Теперь стало возможным использовать смешанные библиотеки топологических элементов САПР моделирования MWO и ADS. Кроме того, в новой версии можно создавать топологию, используя как библиотеку компонентов MWO, так и ADS в одном проекте, а также экспортировать полученный результат в формат MWO или ADS.

Схемный редактор OrCAD Capture

В схемном редакторе Capture реализовано несколько существенных улучшений его функциональности и интерфейса пользователя. Рассмотрим их подробнее.

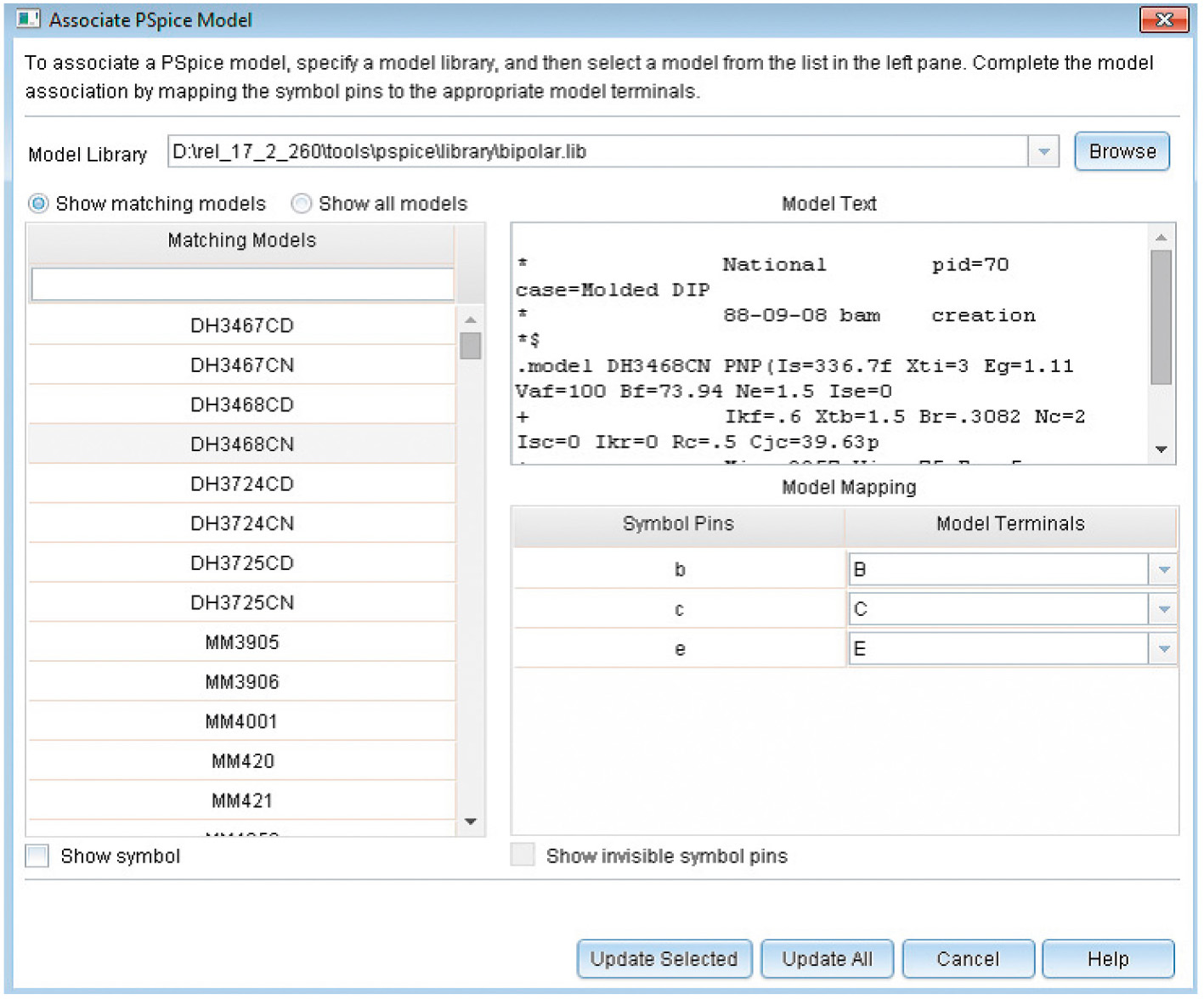

Схемный редактор Capture очень хорошо интегрирован с системой схемотехнического моделирования PSpice. Для того чтобы ещё более упростить работу схемотехников, был улучшен интерфейс назначения схемным символам новых SPICE-моделей (например, загруженных с сайтов производителей). Теперь достаточно указать файл библиотеки моделей, выбрать нужную модель из списка и назначить выводы символа соответствующим портам модели (см. рис. 13).

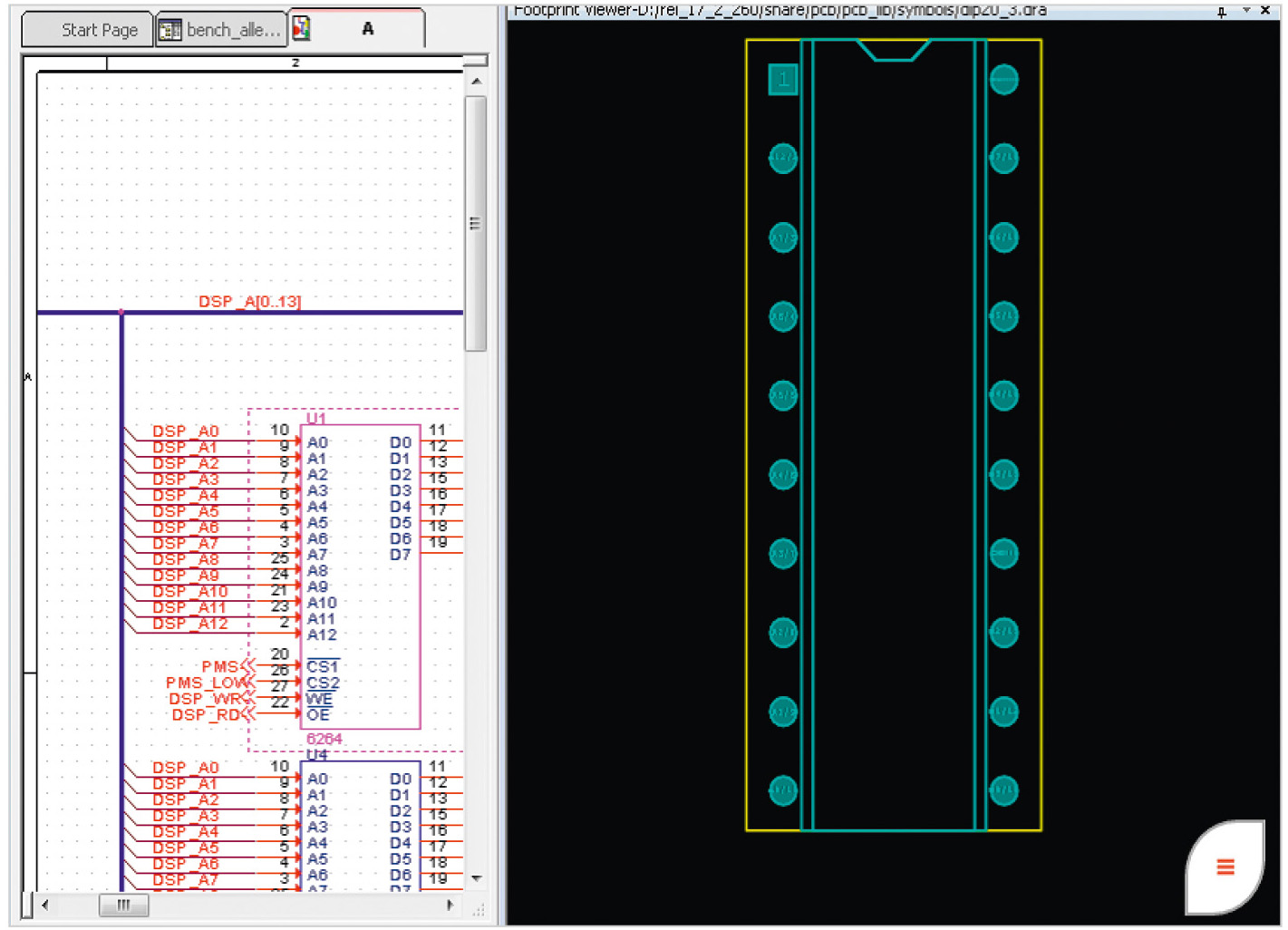

Кроме того, появилась возможность визуализации футпринта для выбранного схемного символа (см. рис. 14). При этом можно выделить вывод на схеме и увидеть, какому выводу он соответствует на футпринте, что облегчает проверку схемы.

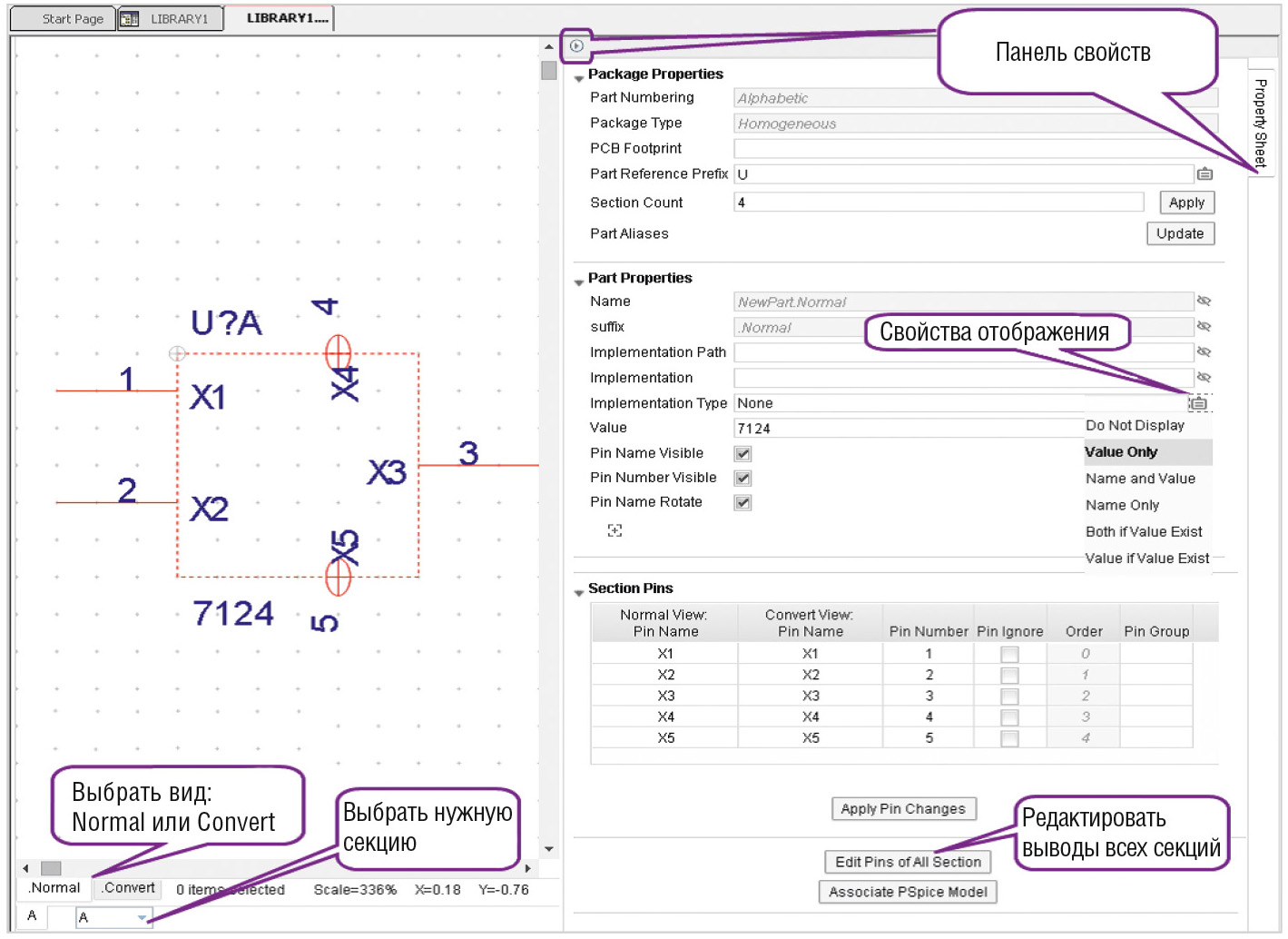

Полностью обновлён редактор схемных символов. Он стал проще и удобнее в работе. Теперь при редактировании символа пользователь видит панель со всеми его свойствами, может управлять видимостью номеров или названий выводов, назначать специальные свойства компоненту или его выводам (см. рис. 15).

Заключение

Cadence OrCAD/Allegro 17.2 QIR6 является более мощным и эффективным решением для проектирования современных печатных плат. Если в настоящее время используется OrCAD версии 16.6 или более ранних, переход на версию 17.2 не будет сложным, т.к. проекты и библиотеки переносятся в новую систему автоматически. Для перехода с P-CAD 2006 можно использовать конвертер PCB – BRD, созданный и поддерживаемый компанией ООО «ПСБ СОФТ». Конвертер позволяет перенести старые проекты печатных плат в новую систему практически без искажений посредством экспорта в формат P-CAD ASCII. Имеются также конвертеры из других систем проектирования.

Важно отметить, что при своей невысокой стоимости даже базовый продукт OrCAD PCB Designer Standard содержит всё необходимое для разработки плат – от схемы до производственных файлов. Система OrCAD Professional подойдет для более продвинутых разработчиков, которые занимаются трассировкой скоростных плат. Расширение OrCAD Sigrity ERC интересно для верификации проекта с точки зрения целостности сигналов. Доступность более продвинутых версий и таких мощных инструментов, как Allegro Venture и Sigrity, позволяет любому предприятию, от самого небольшого до очень крупного, выполнить любую поставленную задачу по разработке электронных устройств с максимальным качеством и эффективностью.

Если вам понравился материал, кликните значок - вы поможете нам узнать, каким статьям и новостям следует отдавать предпочтение. Если вы хотите обсудить материал - не стесняйтесь оставлять свои комментарии : возможно, они будут полезны другим нашим читателям!