# <u>Разработки</u> Безопасность

# Высокопроизводительные вычислительные системы с реконфигурируемой архитектурой, построенной на ПЛИС

Артём Коновальчик

В статье рассмотрены особенности построения высокопроизводительных систем на основе ПЛИС последнего поколения. Подробно раскрыты вопросы организации архитектуры комплекса, позволяющей заметно превосходить отечественные и зарубежные аналоги, а также существенно расширить спектр решаемых задач.

### Введение

Задача построения суперкомпьютеров с каждым днём приобретает всё большую актуальность и становится приоритетной в передовых разработках науки и техники, что вызвано растущим спросом на высокопроизводительные вычисления со стороны коммерческих, государственных и научных организаций.

Ключевой тенденцией в решении важнейших научно-технических задач становится непрерывное увеличение производительности вычислительных комплексов. Производительность однопроцессорных компьютеров практически достигла предела. Возможности дальнейшего роста производительности с помощью уменьшения технологических норм практически исчерпаны. Кроме того, при увеличении плотности размещения транзисторов на кристалле значительно возрастает сложность процессоров, поэтому прирост производительности не пропорционален затрачиваемым аппаратным ресурсам и энергии. Не помогает дальнейшее наращивание объёмов кэш-памяти микропроцессоров, а также числа одновременно выполняемых команд. Заявленные производителями пиковые характеристики процессоров практически недостижимы без низкоуровневого программирования. Большинство трудоёмких вычислительных задач выполняется на массовых микропроцессорах с низкой эффективностью, составляющей не более 10–20% [1]. Если десять лет назад компьютерному сообществу казалось, что вычислительная техника может неограниченно развиваться, совершенствуя микропроцессорные схемотехнические и технологические решения, то сейчас ясно, что без кардинальной перестройки архитектуры вычислительной техники сохранить темп роста её производительности невозможно.

Одним из способов повышения производительности вычислительных систем является распараллеливание вычислительных процессов. В то же время реальная производительность многопроцессорных вычислительных систем, которые ориентированы на традиционные методы организации параллельных вычислений и представляют собой механически соединённые традиционные микропроцессоры, зачастую не превышает 10-15% от заявленной пиковой производительности вследствие необходимости реализации множества процедур межпроцессорного обмена, а также синхронизации последовательных процессов, выполняемых в процессорах системы [2]. Основная причина этого - несоответствие между жёсткой архитектурой вычислительной системы (ВС) и информационной структурой решаемых задач, из-за чего существующие суперкомпьютеры и работают столь неэффективно. Данный недостаток позволяет устранить способ построения ВС с гибкой, динамически пе-

рестраиваемой (программируемой) архитектурой [3], подстраиваемой под информационную структуру конкретной задачи. Практическое внедрение данной концепции сдерживалось отсутствием необходимой для её реализации реконфигурируемой элементной базы. В последние годы такая элементная база на рынке появилась - это программируемые логические интегральные схемы (ПЛИС) высокой степени интеграции. На основе ПЛИС возможно без привлечения больших финансовых затрат создавать высокопроизводительные вычислительные системы с программируемой архитектурой, существенно опережающие существующие аналоги по многим ключевым характеристикам.

### ПЛИС — основной элемент суперкомпьютера

По этому пути уже идут ведущие мировые производители. В то же время западные и отечественные производители используют ПЛИС, как правило, только в качестве сопроцессоров к стандартным вычислительным узлам — универсальным микропроцессорам. Концепция же построения ВС с программируемой архитектурой предполагает использовать ПЛИС в качестве базы для создания реконфигурируемых вычислительных систем, адаптируемых к структуре решаемой задачи. В качестве основного вычислительного элемента используют-

www.cta.ru CTA 3/2013

Рис. 1. Общий вид БВР-01

ся вычислительные структуры, созданные в поле логических блоков ПЛИС, в то время как небольшое количество универсальных микропроцессоров выполняют вспомогательные функции: загрузку конфигураций ПЛИС, обмен данными, управление, тестирование, загрузку исходных данных, визуализацию результатов и т.п.

Высокопроизводительные вычислительные системы (ВВС) на основе ПЛИС предназначены для решения задач, требующих обработки сверхбольших информационных массивов и потоков. Современная тенденция к высокой плотности вычислений предъявляет особые требования к архитектуре построения ВВС и акцентирует внимание на достижении максимальной производительности при таких конструктивных ограничениях, как габариты, потребляемая мощность и тепловыделение. Имеюшиеся на сегодняшний день вычислители на базе ПЛИС в основном узко ориентированы на решение задач обработки по одному и тому же алгоритму большого количества наборов входных данных и до недавнего времени заметно уступали там, где требовались вычисления, связанные с высокоскоростной передачей данных как между элементами ВВС, так и при взаимодействии ВВС с другими элементами кластера.

В подавляющем большинстве случаев кластеры на основе ПЛИС приме-

няются для решения математических задач (в том числе задач криптографии и обеспечения информационной безопасности), при этом решения по объединению всех вычислительных блоков в единое вычислительное пространство заказчик принимает самостоятельно. Такой вариант вполне допустим для типовых задач. Однако круг задач, реализуемых на кластерах такого рода, значительно шире. Требования, предъявляемые к подобным системам их заказчиками, диктуют необходимость более специфического функционала, организации гораздо более сложного взаимодействия между узлами кластера, имеются существенные требования к пропускной способности каналов передачи данных. Этот список может быть расширен, однако уже на данном этапе становится ясно, что архитектурные и конструктивные требования заказчиков таковы, что элементы ВВС должны обладать значительно улучшенными функциональными характеристиками и давать возможность построения кластеров любых типов, в том числе и в зависимости от решаемой задачи.

В процессе построения любых программных систем решения о функциональных возможностях и структуре отдельных компонентов следует принимать после того, как будет разработана общая архитектура системы. Этот тезис верен в том числе и тогда, когда речь идёт о написании программного продукта для высокопроизводительных кластеров на основе ПЛИС. Наряду с написанием конфигурационных файлов ПЛИС существует необходимость в обеспечении совместного функционирования всех вычислительных модулей кластера, координации и диспетчеризации вычислительного процесса.

## АРХИТЕКТУРА СУПЕРКОМПЬЮТЕРА НА ОСНОВЕ ПЛИС

Современные ПЛИС потенциально обладают широкими возможностями

для применения в качестве основных элементов ВВС [4]. При этом главным препятствием к их использованию оста- ётся фактическое отсутствие адекватной архитектуры вычислителя (совокупности вычислителей — кластер), позволившей бы наиболее широко применить все потенциальные возможности.

Учитывая широкий класс задач, требующих новых подходов к высокопроизводительным вычислениям, на основе изложенных принципов перед разработчиками компании FASTWEL была поставлена задача создания вычислителя нового поколения БВР-01 (рис. 1). Вычислитель ориентирован на решение задач, требующих интенсивной обработки данных, применения методов линейной алгебры, цифровой обработки сигналов, математической физики, символьной обработки и рассчитан на использование во многих встраиваемых системах, в том числе в системах военного назначения, системах обеспечения информационной безопасности, мобильных системах транспорта. Главные его особенности – возможность гибкого конфигурирования собственной структуры и возможность объединения с другими аналогичными устройствами для создания кластерных структур.

БВР-01 представляет собой законченный блок в виде 19" конструктива высотой 1U с управляющим компьютером (УК) СРС1301 компании FAST-WEL, выполненным на базе процессора Intel Core 2 Duo, и с восемью ПЛИС Xilinx Virtex-6, соединёнными между собой современным высокоскоростным интерфейсом PCI Express Gen 2.0. На БВР-01 могут устанавливаться любые ПЛИС из семейства Xilinx Virtex-6: LX240, LX365, LX550, SX315 или SX475 (табл. 1). Модуль памяти EM-DDR3-2GB позволяет использовать память DDR3 ёмкостью 2 Гбайт на ПЛИС.

На задней панели блока расположены разъёмы внешних интерфейсов (рис. 2).

Таблица 1

# Основные характеристики современных ПЛИС серии Virtex-6

| основные характеристики современных плис серии уптех-о |                                       |                                            |                                  |                                  |                                  |                 |            |              |                                |

|--------------------------------------------------------|---------------------------------------|--------------------------------------------|----------------------------------|----------------------------------|----------------------------------|-----------------|------------|--------------|--------------------------------|

| Название<br>микросхемы                                 | Количество<br>логических<br>элементов | Конфигурируемые логические элементы (CLBs) |                                  | Блочная память                   |                                  |                 | Интерфейсы | Мас-адреса   | Количество<br>пользова-        |

|                                                        |                                       | Логические<br>элементы                     | Распределённая<br>память (кбайт) | Количество<br>блоков<br>18 кбайт | Количество<br>блоков<br>36 кбайт | Всего,<br>кбайт | для PCI-E  | для Ethernet | тельских<br>вводов/<br>выводов |

| XC6VLX75T                                              | 74 496                                | 11 640                                     | 1 045                            | 312                              | 156                              | 5 616           | 1          | 4            | 360                            |

| XC6VLX240T                                             | 241 152                               | 37 680                                     | 3 650                            | 832                              | 416                              | 14 976          | 2          | 4            | 720                            |

| XC6VLX365T                                             | 364 032                               | 56 880                                     | 4 130                            | 832                              | 416                              | 14 976          | 2          | 4            | 720                            |

| XC6VLX550T                                             | 549 888                               | 85 920                                     | 6 200                            | 1 264                            | 632                              | 22 752          | 2          | 4            | 1 200                          |

| XC6VSX315T                                             | 314 880                               | 49 200                                     | 5 090                            | 1 408                            | 704                              | 25 344          | 2          | 4            | 720                            |

| XC6VSX475T                                             | 476 160                               | 74 400                                     | 7 640                            | 2 128                            | 1 064                            | 38 304          | 2          | 4            | 840                            |

CTA 3/2013 www.cta.ru

Рис. 2. Интерфейсные разъёмы на задней панели БВР-01

Электропитание подаётся в БВР-01 через разъём питания, находящийся на задней панели. Подаваемое напряжения преобразуется до требуемого номинала интегрированными в устройство DC/DC-конверторами собственной разработки. Обеспечивается рабочий ток более 100 А по номиналу 1 В на пару ПЛИС, что допускает использование в БВР-01 самых больших и энергоёмких кристаллов ПЛИС семейства Virtex-6.

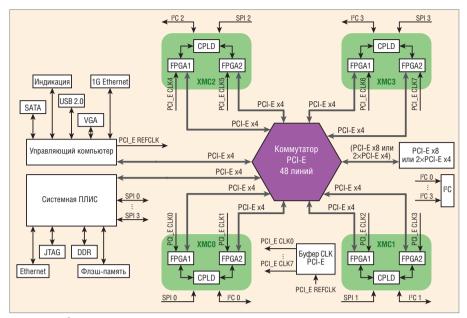

Структурная схема БВР-01 приведена на рис. 3.

Для реализации PCI Express в БВР-01 предусмотрен коммутатор PEX8648, с помощью которого каждая из восьми ПЛИС связана друг с другом и с УК, что позволяет передавать данные по шине PCI Express Gen 2.0 с суммарной пропускной способностью на уровне 20 Гбит/с. Внешний порт PCI Express позволяет каскадировать БВР-01 с использованием медных или оптических кабелей.

Мониторинг, диагностика, контроль данных о напряжении и температуре кристаллов ПЛИС, управление питанием БВР-01 производятся с использованием специально для этого разработанного модуля диагностики (МД), который имеет отдельный сетевой выход Fast Ethernet и реализован с использованием Web-интерфейса.

Габаритные размеры БВР-01 составляют  $44 \times 482 \times 650$  мм ( $B \times \text{Ш} \times \Gamma$ ), вес 25 кг.

В целом БВР-01 представляет собой современный, легко масштабируемый вычислитель на базе реконфигурируемых элементов ПЛИС Xilinx Virtex-6 (LX240, LX365, LX550, SX315 или SX475) и с общим энергопотреблением менее 800 Вт.

В основу его разработки положено объединение следующих составляюших:

- вычислительный элемент (ВЭ) в качестве основного (минимального) ВЭ предлагается модуль ХМС с установленными на нём двумя ПЛИС Хіlinx (LX550 или SX475);

- управляющий компьютер в качестве УК предлагается СОМ Expressмодуль СРС1301;

- плата Extended ATX плата-носитель с установленными на ней четырьмя ВЭ, УК, коммутатором PCI Express и системной ПЛИС;

Условные обозначения:

**CPLD** – конфигурационная ПЛИС; **XMC 0...3** – несущие платы;

**FPGA1**, **FPGA2** – программируемые логические интегральные схемы.

Рис. 3. Структурная схема БВР-01

модуль диагностики — в качестве МД предлагается плата RDM, управляющая диагностируемыми параметрами БВР-01, в том числе напряжением и температурой, и имеющая в своём составе сетевой выход Fast Ethernet.

Блок вычислительный реконфигурируемый (БВР-01) объединяет в себе 4 ВЭ, УК, плату-носитель, МД и является базовым элементом построения кластера. В БВР-01 реализованы такие принципы, как:

- универсальность возможность выполнения практически любых вычислительно-трудоёмких задач;

- масштабируемость возможность формировать кластер из любого количества таких блоков.

### ЗАКЛЮЧЕНИЕ

Индустрия суперкомпьютеров за последние годы прошла огромный путь и нашла своё место в решении широкого круга задач. В то же время требования к современным вычислительным системам всё возрастают и толкают производителей, с одной стороны, к конструированию узкоспециализированных решений, ориентированных на конкретные классы задач, а с другой — к поиску универсальных и наиболее эффективных решений.

Благодаря использованию уникальных технических и программных решений, а также высокоскоростных интерфейсов передачи данных БВР-01 в полной мере удовлетворяет требованиям, предъявляемым к современным уни-

версальным высокопроизводительным вычислителям, позволяя создавать на своей основе ПЛИС-суперкомпьютеры, превосходящие по технико-экономическим характеристикам ВВС с другой архитектурой в сегменте рынка суперЭВМ и предоставляя все основания для применения во встраиваемых системах военного назначения, требующих высокоскоростной обработки сверхбольших объёмов информации. Этот вывод подтверждается успешными результатами первых внедрений представленного в статье изделия.

### Литература

- Волков Д. Реальность и фантазии // Открытые системы. – 2006. – № 5.

- 2. Аладышев О.С., Дикарев Н.И., Овсянников А.П., Телегин П.Н., Шабанов Б.М. СуперЭВМ: области применения и требования к производительности // Известия высших учебных заведений. Электроника. 2004. № 1. С. 13—17.

- 3. Каляев А.В., Левин И.И. Модульно-наращиваемые многопроцессорные системы со структурно-процедурной организацией вычислений. М.: Янус-К, 2003. 380 с.

- 4. Virtex-6 Family Overview DS150 (v2.4). January 19, 2012 [Электронный ресурс]. Режим доступа: http://www.xilinx.com/support/documentation/data\_sheets/ds150.pdf.

Aвтор – сотрудник фирмы FASTWEL

Телефон: (495) 234-0639 E-mail: info@fastwel.ru